大家好,又到了每日學習的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通

2018-06-21 11:15:25 6164

6164

FIFO是隊列機制中最簡單的,每個接口上只有一個FIFO隊列,表面上看FIFO隊列并沒有提供什么QoS保證,甚至很多人認為FIFO嚴格意義上不算做一種隊列技術,實則不然,FIFO是其它隊列的基礎

2022-07-10 09:22:00 1338

1338 FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 1199

1199

FIFO為什么不能正常工作?復位信號有效長度不夠,接口時序不匹配,可看下面這篇文章。 本文將介紹: 非DFX工程如何確保異步FIFO自帶的set_max_delay生效? DFX工程如何確保異步

2023-11-02 09:25:01 475

475

最近加的群里面有些萌新在進行討論**FIFO的深度**的時候,覺得 **FIFO的深度計算比較難以理解** 。所

2023-11-28 16:19:46 347

347

知道... FSM有9個狀態,但它是一個快速測試,我認為它應該可以工作。會發生的是,如果我將串行輸入直接連接到串行輸出,一切正常,但是,當我把FIFO放在兩者的中間時,它不起作用,我沒有收到正確的數據

2019-02-14 08:09:57

大家好,我有一個設計問題,我有兩個域之間的接口:輸入是50MHz的16位并行數據輸出為500 MHz的1位串行數據,對于這種情況,我需要設計一個FIFO。任何人都可以幫助我設計FIFO,特別是最小

2019-01-10 10:45:27

FIFO的具體設計和常見問題

2021-01-06 06:04:20

以下是我寫的FIFO(AL422B)的程序,不知道哪里出錯了。求解答。。。。。。。(我是想用OV760+FIFO的采集圖片的,但是調試的時候調不出來)說明:操作平臺為MC9S12芯片,頻率為

2015-07-20 23:55:19

在我的應用程序中,我有一個狀態機,它寫入具有特定格式的字的FIFO。該狀態機每500字將一個時間字寫入FIFO。 FIFO IS 2:1比率TWFT virtex 5。當我使用軟件應用程序從FIFO

2020-06-15 13:50:11

的ARE接FIFO的讀引腳,DSP的INT1(幀同步事件)接FIFO的HF,想每半滿一次,就用DMA運送一幀數據(4096),想問下程序框架流程,和一些具體問題。如果可以的話,加我QQ:7614 75 745,非常感謝

2014-11-04 20:29:28

L3GD20是否有FIFO空中斷? #fifo#l3gd20以上來自于谷歌翻譯以下為原文 Does the L3GD20 have FIFO empty interrupt available? #fifo #l3gd20

2018-12-06 16:11:43

抄了原子哥的驅動代碼,放在了c8t6最小系統板上去跑,一切正常,自檢原本通過不了,一頓操作后可以通過了,加速度角速度讀取也OK,唯獨讀取FIFO中的數據讀不出來具體為mpu_dmp_get_data

2022-02-10 06:12:34

你好,我正在運行低級UART W/ISR的示例應用CE219656。該部分已更改為運行在PSoC6 WiFi板上。未修改的代碼工作正常。然而,對于我的應用程序,我想看看在執行FIFO讀之前,RX

2018-09-29 15:54:54

請問大家這個管腳的具體作用,因為之前使用的是ad9218,沒有這個管腳,現在更換芯片,發現在這個管腳,但不知道該怎么用,這個是什么功能,如果不用該怎么處理,手冊上并沒有說不用該怎么處理,難道是必須使用嗎?那該怎么做呢?求教!

2023-12-13 08:34:56

sudo的具體作用是干嘛的?分幾種情況來使用呀?

2020-06-19 05:56:29

跨時鐘域處理 & 亞穩態處理&異步FIFO1.FIFO概述FIFO: 一、先入先出隊列(First Input First Output,FIFO)這是一種傳統的按序執行方法,先進

2022-02-16 06:55:41

你好。我正在嘗試使用下面的Xilinx FIFO,但我不明白為什么dout會在那時停止?在這一點上,fifo不再起作用了。有誰知道如何解決這個問題?我只是讓你知道,aclk,wr_clk是192Mhz,bclk,rd_clk是100Mhz。

2020-05-04 07:14:43

充電電感的作用,具體工作原理?

2015-03-29 10:26:23

希望大神能分析分析復合管的具體作用

2013-06-03 23:36:14

有沒有大神弄過叉指電極?或是對其有所了解,,請教一下,設計及成這種結構具體有什么作用?和普通的PCB上的焊盤有區別么?

2017-05-13 22:49:24

小于等于PIPE_BUF時,那么或者寫入全部字節,或者一個字節都不寫入,它屬于一個一次性行為,具體要看FIFO中是否有足夠的緩沖區。(2)當要寫入的數據量大于PIPE_BUF時,Linux將不再保證寫入

2016-09-24 10:49:41

fifo就不要造輪子了,用現成的就行了。linux內核中有目前人類寫出的基于c語言的最強FIFO,請自行搜索學習《巧奪天工的kfifo》,或者我的另一篇博文《整數的環回特性》。直接把最常用的幾個函數

2021-08-16 08:41:16

XINLINX FPGA與CY7C68013通訊,異步slave fifo通訊方式,PKTEND信號的作用是什么,不用的話是不是應該拉高 ,另外由于fifo adr用的都公用地址線,時序上怎么選擇,誰能共享一下verilog HDL的例子。

2015-07-10 15:17:28

毫米波雷達的作用和有效距離式多少?是否可以用于探測人體生物電信號?

2021-12-18 09:56:13

這個電路是低水位報警電路。滑動變阻器模擬檢測到的水位信息的模擬量。不明白的事,R6,R7,以及三極管具體有啥作用。謝謝

2019-05-19 00:20:47

求大神指導,單片機的FLASH SIZE 具體是什么含義,有什么作用,原理是什么

2017-05-01 20:15:28

轉換回到導線上。這種插入阻抗與頻率相關,其1MHz值一般位于30-500M?的范圍內,具體視探頭而定。在大多數情況下,電流探頭的插入阻抗很小,產生的負載可以忽略不計。 電流探頭有兩種形式,一種特定

2017-08-30 15:43:48

這兩天學習無線模塊 有以下幾點疑問 求大神:1、設置地址碼的寬度有什么作用 2、接收通道的地址碼 通道040位 通道1~5的地址碼 高位與通道1相同 低位可設置這樣的設計作用是什么3、數據包中

2020-05-28 02:48:05

我在網上看到一篇利用格雷碼來設計異步FIFO,但是看他們寫的一些源碼,小弟有些不是很理解,在設計時為什么會出現Waddr和wptr兩個關于寫指針的問題,他們之間的關系是什么????wptr在定義時候為什么比Waddr多一位呀???

2017-05-19 11:04:13

FIFO IP與RAMFIFO IP有何不同?

2023-08-11 10:52:12

你好,在看DAC3164 的datasheet 時,遇到個問題。SYNC P/N 用來resetDAC內部的FIFO。我想問的是,該DAC內部的FIFO有多大,需要多少個dataclk后需reset?謝謝~

2019-05-20 10:42:15

LIS3DH是否有FIFO空中斷? #motion-sensor #accelerometer#lis3dh #fifo#lis3dh以上來自于谷歌翻譯以下為原文 Does the LIS3DH

2019-06-04 11:40:52

哪位能幫忙分析一下這個電路的具體作用,表示已經看瞢了?非常感謝

2019-05-09 22:32:31

本帖最后由 一只耳朵怪 于 2018-6-13 15:01 編輯

SPI使用FIFO和不使用有什么區別,是不是使用FIFO效率更高

2018-06-13 11:12:07

本帖最后由 一只耳朵怪 于 2018-5-22 10:05 編輯

請問,該開發板中的芯片 SN74CBTLV3257RGYR的具體作用?我查看到的芯片資料的說明很少,沒有具體提到有何用處。該板子有兩處連續用了3個該芯片的。 謝謝

2018-05-22 04:07:57

智能食品安全快速檢測儀有什么作用【山東云唐·YT-G2400】有機磷農藥特殊分子結構的構成,導致其自身不能夠產生熒光,在進行檢測的過程中就可以使用該項原理,有機磷農藥會對膽堿酯酶產生一定的抑制作用

2021-03-31 10:20:53

農藥超標檢測儀有哪些作用【山東云唐】農藥是對于靶標生物作用的一種化合物,其中絕大多數是有機化合物,它包括殺蟲劑、殺菌劑、除草劑和植物生長調節劑等.從各種類型的污染物對生態系統影響面來看,化學農藥

2021-04-02 17:31:27

1.什么是FIFO?FIFO是英文First In First Out 的縮寫,是一種先進先出的數

2009-07-22 16:00:48 0

0 FIFO中文應用筆記

2009-07-28 10:03:31 30

30 系統在上電復位時,SPI工作在標準SPI模式,禁止FIFO功能。FIFO的寄存器SPIFFTX、SPIFFRX和SPIFFCT不起作用。通過將SPIFFTX寄存器中的SPIFFEN的位置為1,使能FIFO模式。SPIRST能在操作的任一階

2009-09-29 10:38:26 33

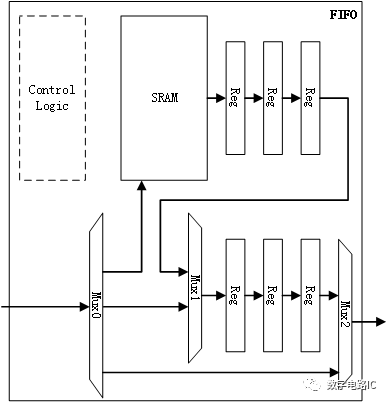

33 設計一個FIFO是ASIC設計者遇到的最普遍的問題之一。本文著重介紹怎樣設計FIFO——這是一個看似簡單卻很復雜的任務。一開始,要注意,FIFO通常用于時鐘域的過渡,是雙時鐘設計

2009-10-15 08:44:35 94

94 摘要:文章介紹了一個正向設計,并已成功流片的FIFO存儲器電路結構設計及關鍵技術.重點研究了實現該電路的兩類關鍵技術,存儲電路和控制邏輯。文中的設計思想和具體的邏輯

2010-05-04 08:48:53 17

17 介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計異步FIFO的難點,解決了異步FIFO設計中存在的兩

2010-07-28 16:08:06 32

32 摘要:使用FIFO同步源自不同時鐘域的數據是在數字IC設計中經常使用的方法,設計功能正確的FUFO會遇到很多問題,探討了兩種不同的異步FIFO的設計思路。兩種思路

2006-03-24 12:58:33 680

680

什么是fifo (First Input First Output,先入先出隊列)這是一種傳統的按序執行方法,先進入的指令先完成并引退,跟著才執行第二條指令。1.什么是FIFO

2007-12-20 13:51:59 11835

11835 摘要:首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;在傳統設計的基礎上提出一種新穎的電路結構并對其進行

2009-06-20 12:46:50 3667

3667

基于FPGA的FIFO設計和應用

引 言

在利用DSP實現視頻實時跟蹤時,需要進行大量高速的圖像采集。而DSP本身自帶的FIFO并不足以支持系統中大量數據的暫時存儲

2009-11-20 11:25:45 2127

2127

FIFO_學習心得。 FIFO_學習心得

2015-11-09 14:07:47 6

6 異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 基于FLASH的FIFO讀寫,介紹的比較詳細,值得一讀。

2016-04-28 10:30:27 22

22 最經典的FIFO原理,詳細講述了FIFO的原理,適合入門新手,仔細分析閱讀,也適合高手查閱。

2016-05-03 15:15:08 0

0 本文首先對異步 FIFO 設計的重點難點進行分析,最后給出詳細代碼。 一、FIFO簡單講解 FIFO的本質是RAM, 先進先出 重要參數:fifo深度(簡單來說就是需要存多少個數據) fifo

2017-11-15 12:52:41 7993

7993

在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 7873

7873

FIFO( First In First Out)簡單說就是指先進先出。由于微電子技術的飛速發展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。作為一種新型大規模集成電路,FIFO芯片以其靈活、方便、高效的特性。

2017-12-06 14:29:31 10173

10173

通過在 MEMS 信號處理電路中設計一個異步結構的 FIFO ,可以有效地降低系統對MEMS的頻繁訪問。設計一個具有多種工作模式的FIFO,可以滿足一些特殊的姿態檢測需求,更好地滿足系統智能化操作需要。實現了一個具體可行的方案,可以實際應用到各種MEMS電路模塊中。

2018-05-05 09:13:00 1524

1524

IP核的全稱是: AXI4-STREAM FIFO 設置注意事項:一定要選擇異步時鐘,也就是雙時鐘,如下: 關于其他配置: TLAST 一般要選擇的,作為邊界界定。其他可以不選。深度不必太深,因為只起到穿越時鐘區域的作用。

2018-03-26 14:40:00 4916

4916

配置FIFO的方法有兩種:

一種是通過QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中選擇FIFO參數編輯器來搭建自己需要的FIFO,這是自動生成FIFO的方法

2018-07-20 08:00:00 17

17 其它進程在讀這些數據 FIFO內沒有數據。解阻塞的原因則是FIFO中有新的數據寫入,不論信寫入數據量的大小,也不論讀操作請求多少數據量。 讀打開的阻塞標志只對本進程第一個讀操作施加作用,如果

2019-04-02 14:45:10 291

291 根據FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2019-11-29 07:08:00 1608

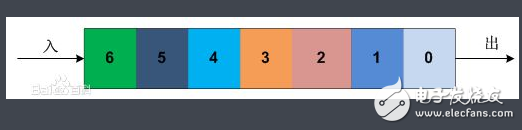

1608 FIFO隊列不對報文進行分類,當報文進入接口的速度大于接口能發送的速度時,FIFO按報文到達接口的先后順序讓報文進入隊列,同時,FIFO在隊列的出口讓報文按進隊的順序出隊,先進的報文將先出隊,后進的報文將后出隊。

2019-11-29 07:04:00 4345

4345 FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進先出。FPGA或者ASIC中使用到的FIFO一般指的是對數據的存儲具有先進先出特性的一個存儲器,常被用于數據

2021-03-12 16:30:48 2795

2795

1.定義 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序

2021-04-09 17:31:42 4697

4697

電容的具體作用介紹 電容器的種類很多,不同種類的電容器其作用也不同。主要有應用于電源電路,實現旁路、去藕、濾波和儲能的作用;應用于信號電路,主要完成耦合、振蕩/同步及時間常數的作用。以下是詳細介紹

2021-06-22 14:29:49 5112

5112 異步FIFO通過比較讀寫地址進行滿空判斷,但是讀寫地址屬于不同的時鐘域,所以在比較之前需要先將讀寫地址進行同步處理,將寫地址同步到讀時鐘域再和讀地址比較進行FIFO空狀態判斷(同步后的寫地址一定

2021-08-04 14:05:21 3794

3794 的Empty和Almost_empty以及讀使能配合起來使用,來保證能夠連續讀,并準確的判斷FIFO空滿狀態,提前決定是否能啟動讀使能。 具體的實施辦法是:當Empty為1,立即停止讀;當Empty

2021-09-09 11:15:00 6293

6293 STM32 串口 FIFO

2021-12-03 09:36:08 37

37 跨時鐘域處理 & 亞穩態處理&異步FIFO1.FIFO概述FIFO: 一、先入先出隊列(First Input First Output,FIFO)這是一種傳統的按序執行方法,先進

2021-12-17 18:29:31 10

10 FIFO最常被用來解決寫、讀不匹配的問題(時鐘、位寬),總結下來,其實FIFO最大的作用就是緩沖。既然是緩沖,那么就要知道這個緩存的空間到底需要多大。接下來的討論,都建立在滿足一次FIFO突發傳輸

2022-02-26 17:41:52 3045

3045

FIFO是FPGA項目中使用最多的IP核,一個項目使用幾個,甚至是幾十個FIFO都是很正常的。通常情況下,每個FIFO的參數,特別是位寬和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在FPGA中對圖像的一行數據進行緩存時,可以采用FIFO這一結構,如上圖所示,新一行圖像數據流入到FIFO1中,FIFO1中會對圖像數據進行緩存,當FIFO1中緩存有一行圖像數據時,在下一行圖像數據來臨的時候,將FIFO1中緩存的圖像數據讀出,并傳遞給下一個FIFO

2022-05-10 09:59:29 3056

3056 FIFO的使用非常廣泛,一般用于不同時鐘域之間的數據傳輸,或者用于不同數據寬度之間的數據匹配。在實際的工程應用,可以根據需要自己寫FIFO。不考慮資源的情況下,也可以使用Xilinx提供的IP核來完成。

2022-08-14 10:49:47 3567

3567 邏輯核? IP FIFO生成器用戶指南描述了FIFO生成器,以及有關設計、定制和實現的信息核心。

2022-08-28 11:09:00 2

2 FIFO的分類根均FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2022-11-01 09:57:08 1315

1315 同步FIFO的意思是說FIFO的讀寫時鐘是同一個時鐘,不同于異步FIFO,異步FIFO的讀寫時鐘是完全異步的。同步FIFO的對外接口包括時鐘,清零,讀請求,寫請求,數據輸入總線,數據輸出總線,空以及滿信號。

2022-11-01 09:58:16 1189

1189 FIFO 是我們設計中常用的工具,因為它們使我們能夠在進行信號和圖像處理時緩沖數據。我們還使用異步FIFO來處理數據總線的時鐘域交叉問題。

2022-11-04 09:14:11 3214

3214 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡稱,是一種先進先出的數據緩存器,與普通存儲器的區別在于沒有外部讀寫的地址線,缺點是只能順序的讀取

2022-12-12 14:17:41 2789

2789 FIFO(First In First Out)是異步數據傳輸時經常使用的存儲器。該存儲器的特點是數據先進先出(后進后出)。其實,多位寬數據的異步傳輸問題,無論是從快時鐘到慢時鐘域,還是從慢時鐘到快時鐘域,都可以使用 FIFO 處理。

2023-03-26 16:00:21 1823

1823

FIFO(First In First Out )先入先出存儲器,在FPG設計中常用于跨時鐘域的處理,FIFO可簡單分為同步FIFO和異步FIFO。

2023-04-25 15:55:28 2892

2892

今天咱們開始聊聊FIFO的設計。FIFO是一個數字電路中常見的模塊,主要作用是數據產生端和接受端在短期內速率不匹配時作為數據緩存。FIFO是指First In, First Out,即先進先出,跟大家排隊一樣。越早排隊的人排在越前面,輪到他的次序也越早,所以FIFO有些時候也被稱為隊列queue。

2023-05-04 15:48:20 544

544 FIFO是異步數據傳輸時常用的存儲器,多bit數據異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 978

978

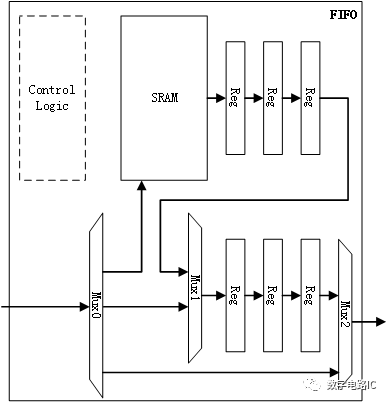

異步FIFO主要由五部分組成:寫控制端、讀控制端、FIFO Memory和兩個時鐘同步端

2023-05-26 16:17:20 911

911

FIFO 是FPGA設計中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機制,是設計人員將數據從一個模塊傳輸到另一個模塊的常用選擇。

2023-06-14 08:59:29 223

223 ? FIFO 是FPGA設計中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機制,是設計人員將數據從一個模塊傳輸到另一個模塊的常用選擇。 在這篇文章中,展示了一個簡單的 RTL 同步

2023-06-14 09:02:19 461

461 Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1625

1625

FIFO在設計是一個非常常見并且非常重要的模塊,很多公司有成熟的IP,所以一部分人并沒有人真正研究寫過FIFO,本文僅簡述FIFO中部分值得保留的設計思路。

2023-09-11 17:05:51 356

356

異步FIFO包含"讀"和"寫“兩個部分,寫操作和讀操作在不同的時鐘域中執行,這意味著Write_Clk和Read_Clk的頻率和相位可以完全獨立。異步FIFO

2023-09-14 11:21:45 545

545

電容有移相作用,那移相具體是什么作用? 關于電容的移相作用,其實可以從三個方面來進行詳細解析: 1. 從物理學角度來說,電容儲存電荷,當電壓變化時,電容器中的電荷會發生變化,這種變化會導致電容器產生

2023-10-17 16:15:46 1616

1616 同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用? 1. 同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO在處理時序有明顯的區別。同步FIFO相對來說是較為

2023-10-18 15:23:58 789

789 請問異步FIFO的溢出操作時怎么樣判斷的? 異步FIFO是數據傳輸的一種常用方式,在一些儲存器和計算機系統中,常常會用到異步FIFO。作為一種FIFO,異步FIFO經常面臨兩種情況:溢出

2023-10-18 15:28:41 299

299

電子發燒友App

電子發燒友App

評論