一:fifo是什么

FIFO的完整英文拼寫為FirstIn First Out,即先進先出。FPGA或者ASIC中使用到的FIFO一般指的是對數據的存儲具有先進先出特性的一個存儲器,常被用于數據的緩存或者高速異步數據的交互。

二:FIFO有幾種結構

FIFO從大的情況來分,有兩類結構:單時鐘FIFO(SCFIFO)和雙時鐘FIFO(DCFIFO),其中雙時鐘FIFO又可以分為普通雙時鐘(DCFIFO)和混合寬度雙時鐘FIFO (DCFIFO_MIXED_WIDTHS)。三種FIFO結構的英文含義如下所示:

?SCFIFO: 單時鐘FIFO

?DCFIFO:雙時鐘 FIFO

?DCFIFO_MIXED_WIDTHS: 混合寬度雙時鐘

在沒有特別指明的情況下,混合寬度雙時鐘FIFO和雙時鐘FIFO統稱為雙時鐘FIFO。

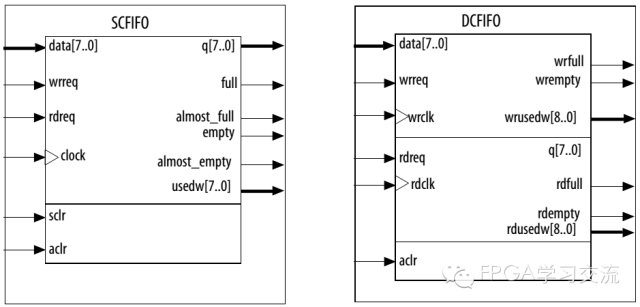

下圖為分別為單時鐘FIFO和雙時鐘FIFO的符號圖:

從圖中我們可以看到,單時鐘FIFO具有一個獨立的時鐘端口clock,當Clock上升沿到達時,且wrreq有效時,將data[7..0]中的數據寫入FIFO;當Clock上升沿到達時,且rdreq有效時,將q[7..0]中的數據輸出FIFO;full是滿標志位,當FIFO寫滿時有效,almost_full是將滿標志,當快寫滿時有效,almost_full數值可以配置;同理empty與almost_empty是空標志和將要空標志,自己也可以配置almost_empty。usedw[7..0]是當前FIFO可以使用的數據。sclr是同步清零,當有效時且Clocks上升沿到達時清楚FIFO的數據;aclr是異步清零,當有效時清除FIFO的數據。

雙時鐘FIFO和單時鐘FIFO基本一樣,就是讀寫分別采用不同的時鐘信號。wrfull為寫滿標志,wrempty為寫空標志,當我們想在只有FIFO空的時候才能寫入時就用wrempty來判斷,wrusedw[8..0]寫入多少數據,rdusedw[8..0]能讀出多少數據。這里將寫入的數據和刻度的數據分開計數的原因是,當我們寫入數據長度和讀數據長度不同時,比如寫的數據長度是16位,讀的數據長度是8位,當寫入一個數據wrusedw[8..0]=1,而rdusedw[8..0]=2。rdfull是讀滿標志,當我們要想要只有寫滿時才可讀可根據這個標志判斷(讀數據包)。rdempty讀空標志,當FIFO沒有可讀數據時有效。aclr異步請零。雙時鐘FIFO只有異步清零。

三:不同結構的FIFO各有什么作用

單時鐘FIFO:

單時鐘FIFO常用于片內數據交互,例如,在FPGA的控制下從外部傳感器讀取到的一連串傳感器數據,首先被寫入FIFO中,然后再以UART串口的數據發送速率將數據依次發送出去。由于傳感器的單次讀取數據可能很快,但并不是時刻都需要采集數據,例如某傳感器使用SPI接口的協議,FPGA以2M的SPI數據速率從該傳感器中讀取20個數據,然后以9600的波特率通過串口發送出去。此過程每秒鐘執行一次。因為2M的數據速率遠高于串口9600的波特率,因此需要將從傳感器中采集到的數據首先用FIFO緩存起來,然后再以串口的數據速率緩慢發送出去。這里,由于傳感器數據的讀取和串口數據的發送都是可以同步于同一個時鐘的,因此可以使用單時鐘結構的FIFO來實現此功能。

雙時鐘FIFO:

雙時鐘FIFO的一個典型應用就是異步數據的收發。

所謂異步數據是指數據的發送端和接收端分別同步與不同的時鐘域,使用雙時鐘FIFO的獨立的讀寫時鐘結構,能夠將不同時鐘域中的數據同步到所需的時鐘域系統中。例如,在一個視頻圖像采集系統中,實現將攝像頭采集的數據通過VGA在顯示器上顯示。攝像頭輸入的數據長度和速度與輸出到VGA顯示的數據長度和速度都不相同,這種情況下使用雙時鐘FIFO。

四:如何在Altera FPGA中使用FIFO實現功能設計

在Altera FPGA中使用FIFO實現用戶功能設計主要有三種實現方式,第一種為用戶根據需求自己編寫FIFO邏輯,當用戶對于FIFO的功能有特殊需求時,可以使用此種方式實現,但此種方式要求用戶有較高的RTL設計能力。第二種方式為使用第三方提供的開源IP核,此種IP核以源碼的形式提供,能夠快速的應用到用戶系統中,當用戶對FIFO功能有特殊需求時,可以在此源碼的基礎上進行修改,以適應自己的系統需求。第三種方式為使用Quartus II軟件提供的免費FIFO IP核,此種方式下,Quartus II軟件為用戶提供了友好的圖形化界面方便用戶對FIFO的各種參數和結構進行配置,生成的FIFO IP核針對Altera不同系列的器件,還可以實現結構上的優化。

原文標題:一起來了解一下FIFO!

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1643文章

21963瀏覽量

614082 -

fifo

+關注

關注

3文章

400瀏覽量

44617

原文標題:一起來了解一下FIFO!

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Altera Agilex 3 FPGA和SoC產品介紹

Altera大學成立,助力FPGA教學發展與人才培養

基于FPGA的FIFO實現

如何在MATLAB中使用DeepSeek模型

使用SCL編寫FIFO功能塊

Altera正式獨立運營:FPGA行業格局將迎來新變局

如何在Windows中使用MTP協議

FIFO Generator的Xilinx官方手冊

如何在Altera FPGA中使用FIFO實現功能設計?

如何在Altera FPGA中使用FIFO實現功能設計?

評論