智多晶FIFO_Generatorv2.0 IP

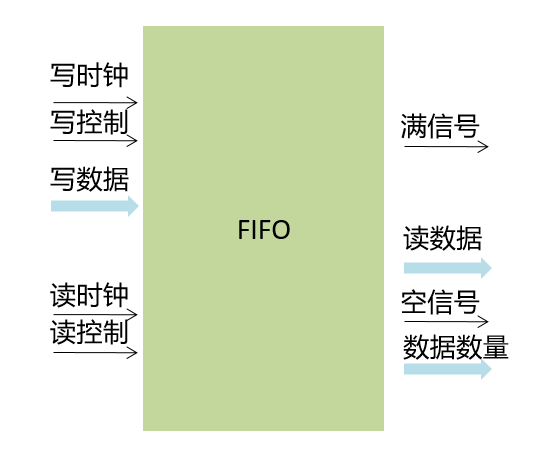

FIFO_Generator是智多晶設計的一款通用型FIFO IP。當前發布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比輸入輸出數據位寬支持和異步FIFO跨時鐘級數配置功能。

FIFO_Generator IP特性

支持同步/異步選擇

支持RAM類型選擇:自動、塊(BLOCK)RAM、分布式RAM

讀端口支持普通/預讀模式:普通讀模式 、預讀模式(First Word Fall Through)

支持跨時鐘域級數配置

支持輸入輸出數據位寬比例可變

數據保護,確保不會出現寫超和讀超的情況

支持data_count輸出(可配置)

支持prog_full, prog_empty端口(可配置)

支持almost_full, almost_empty端口(可配置)

RAM類型選擇

FIFO_Generator IP支持用戶選擇FIFO內RAM的資源類型,可選“塊(Block)RAM”和“分布式RAM”。默認為“自動”,軟件根據用戶輸入的FIFO數據位寬和深度,自動選擇合適的資源來實現。

分布式RAM使用LUT資源,塊(Block)RAM使用塊RAM(EBR)資源。一般建議小尺寸FIFO使用分布式RAM,大尺寸的FIFO使用塊(Block)RAM。合理選擇使用的存儲資源類型可以獲得很好的性能和資源占用。

讀數據模式選擇

FIFO_Generator IP支持2種FIFO讀模式,“普通讀模式”和“預讀(FWFT)模式”。

普通讀模式,數據在進行有效讀信號(rd_en & !empty)以后立即更新。在沒進行讀操作之前,端口上的數據無效,或保持上一次讀出的數據。

FIFO普通讀模式時序圖

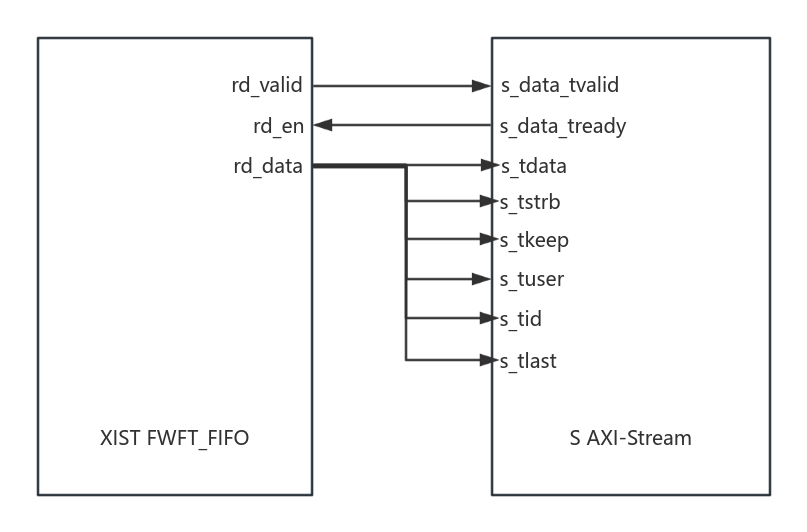

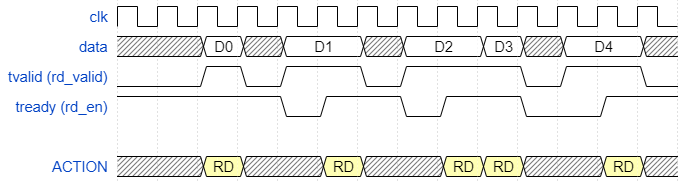

預讀模式,數據在FIFO內會自動搬運到端口上并以rd_valid信號作為端口數據可用且未過期的標志。預讀模式下,以rd_valid和rd_en信號同時為1的作為讀取條件,因此工作在預讀模式的FIFO和AXI/AHB/APB總線的握手反壓操作兼容性非常好。

智多晶FWFT FIFO適配AXI-Stream接口的典型連接

AXI-Stream握手反壓式操作時序圖

輸入輸出數據位寬比例變化

2.0版本的FIFO generator IP新增對輸入輸出端口的數據位寬調整的支持。默認為1:1模式,可選8:1,4:1,2:1,1:2,1:4,1:8。

當用戶選擇非等比輸入輸出接口位寬時,如果啟用data_count端口,會分別得到wr和rd兩個端口的data_count輸出。

該特性在選擇塊(Block)RAM和分布式RAM模式下都提供支持,對RAM類型沒有要求。

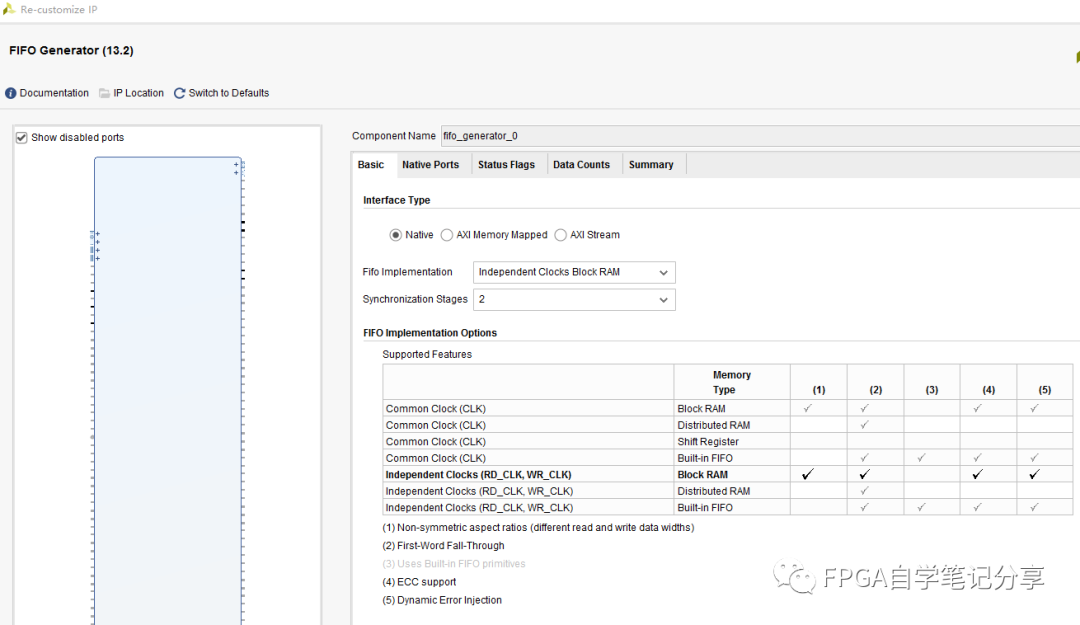

FIFO_Generator IP配置與使用

打開IP

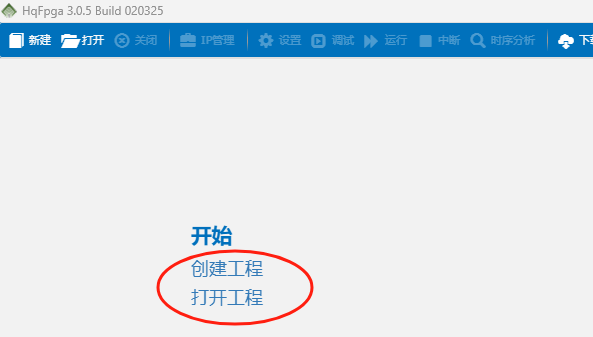

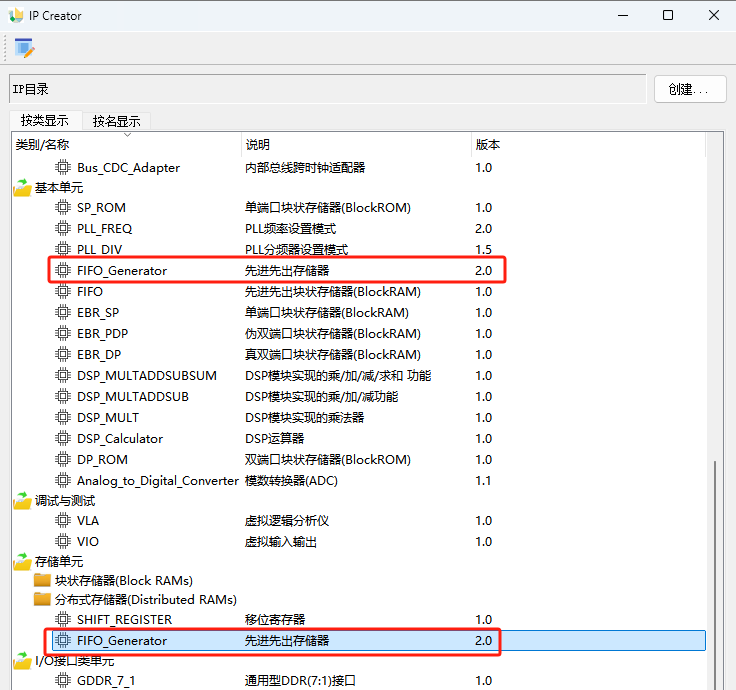

第一步,使用HqFpga v3版本軟件,創建或打開一個工程。

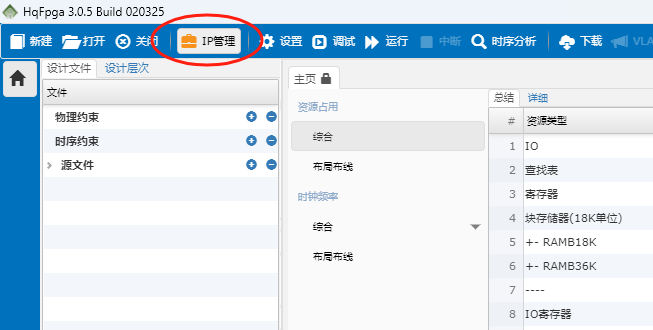

第二步,在已打開的工程中,點擊“IP管理”圖標。

第三步,在IP管理器“IP Creator”--“存儲單元”分類或“基本單元”分類下找到FIFO_Generator IP,雙擊打開FIFO_Generator IP配置界面。

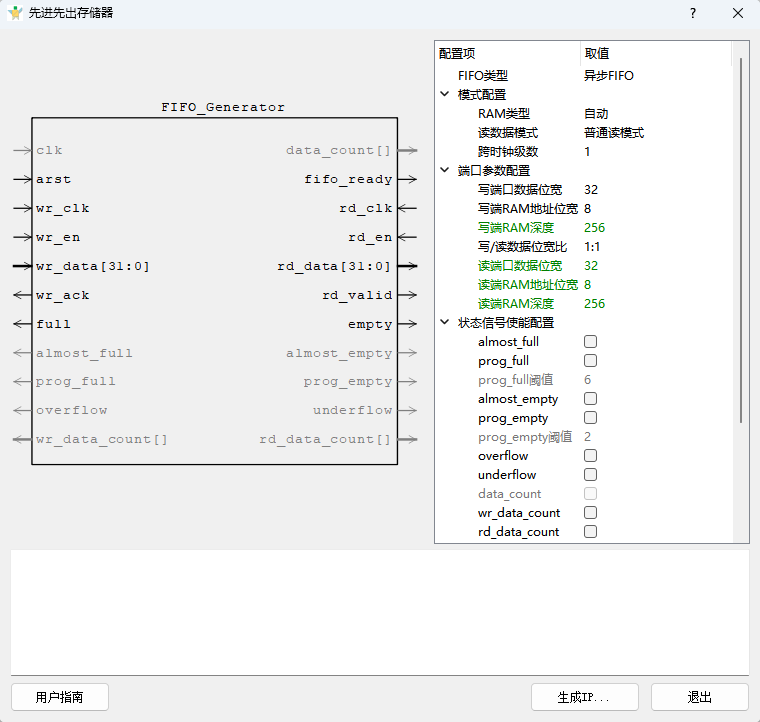

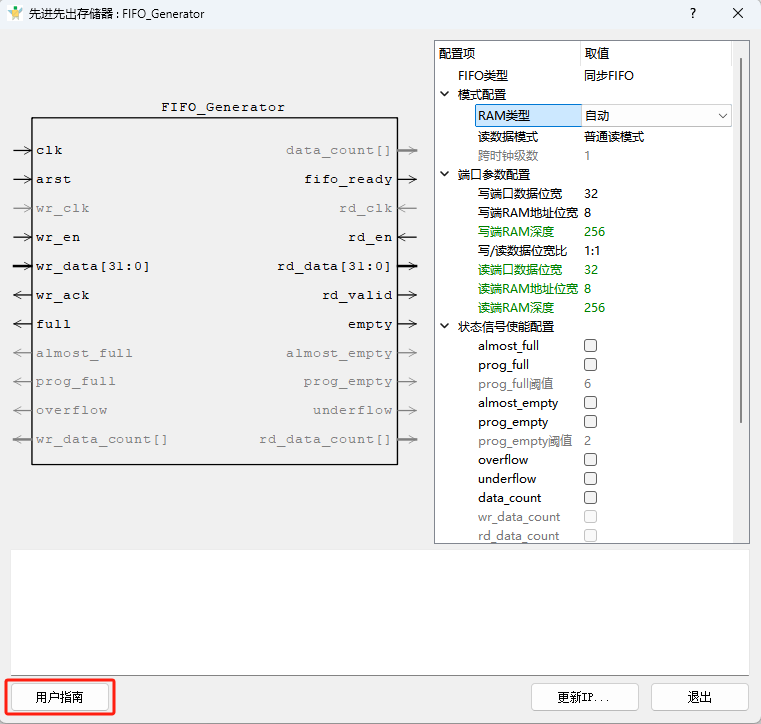

配置IP

IP配置界面的配置選項清晰明確。從上到下依次對FIFO類型,功能模式,端口規模參數進行配置,最后選擇需要用到的狀態信號。針對輸入輸出數據端口變位寬的特性,IP界面會根據當前的配置以綠字方式提供實時信息反饋,幫助用戶理解這些配置產生的效果。

不同的功能配置會影響輸出IP占用的FPGA邏輯資源和IP模塊的性能,建議用戶關閉不需要的功能從而獲得最佳的資源和性能表現。

設計資源

FIFO_Generator IP用戶文檔已隨IP發布,可通過IP界面直接獲得。

在FIFO_Generator IP界面左下角,點擊“用戶指南”可以直接打開FIFO_Generator IP的用戶指南(UserGuide)pdf文件。

其它相關設計資源后續會陸續通過官網發布,歡迎關注。有任何疑問請通過智多晶公眾號或FAE與我們聯系。

-

IP

+關注

關注

5文章

1787瀏覽量

151351 -

fifo

+關注

關注

3文章

400瀏覽量

44625 -

時鐘

+關注

關注

11文章

1884瀏覽量

132855 -

端口

+關注

關注

4文章

1045瀏覽量

32729

原文標題:“芯”技術分享 | 智多晶FIFO_Generator IP介紹

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Efinity FIFO IP仿真問題 -v1

智多晶XSTC_8B10B IP介紹

智多晶eSPI_Slave IP介紹

為什么為spartan6生成fifo ip_core時會出現警告?

國產智多晶FPGA介紹及應用

來自FIFO的嚴重警告怎么解決?

【正點原子FPGA連載】第十三章IP核之FIFO實驗-領航者ZYNQ之FPGA開發指南

如何將IP模塊整合到System Generator for DSP中

利用XILINX提供的FIFO IP進行讀寫測試

XILINX FPGA IP之FIFO Generator例化仿真

FIFO Generator的Xilinx官方手冊

智多晶LPC_Controller IP介紹

智多晶FIFO_Generator IP介紹

智多晶FIFO_Generator IP介紹

評論