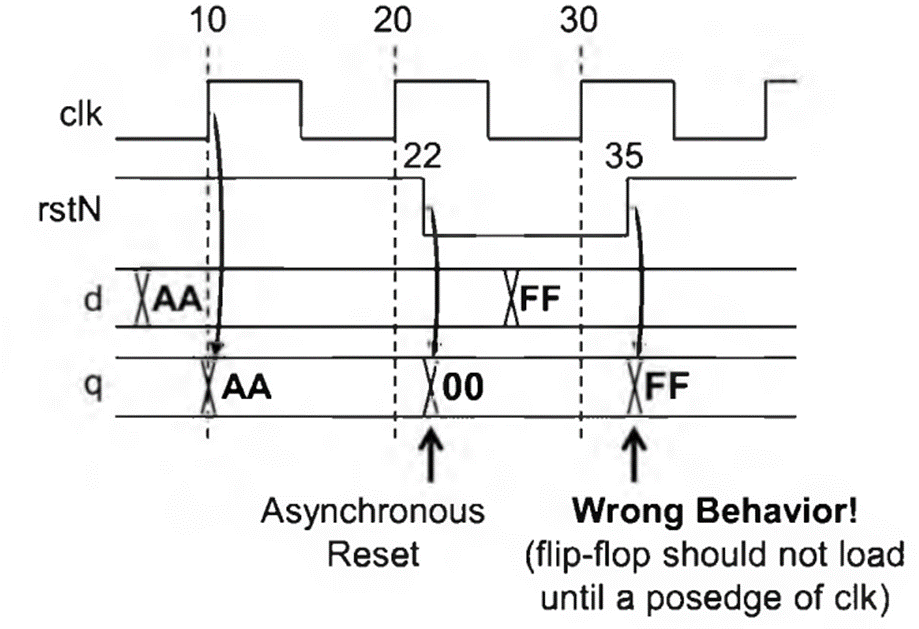

Part1數(shù)字硬件建模SystemVerilog-時(shí)序邏輯建模(4)同步和異步復(fù)位

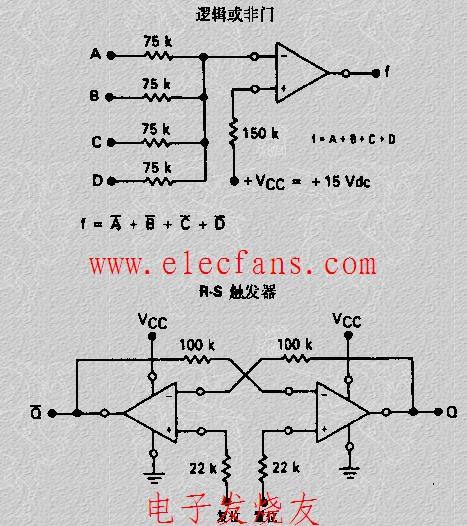

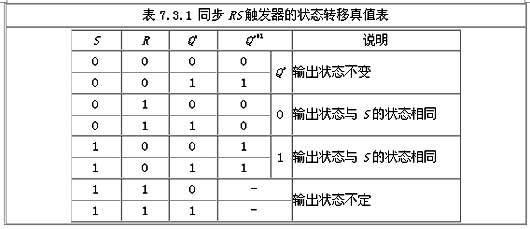

數(shù)字門級電路可分為兩大類:組合邏輯和時(shí)序邏輯。鎖存器是組合邏輯和時(shí)序邏輯的一個(gè)交叉點(diǎn),在后面會(huì)作為單獨(dú)的主題處理。

組合邏輯描述了門級電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個(gè)輸入的邏輯與。如果輸入值發(fā)生變化,輸出值將反映這一變化,組合邏輯的RTL模型需要反映這種門級行為,這意味著邏輯塊的輸出必須始終反映該邏輯塊當(dāng)前輸入值的組合。

SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續(xù)賦值語句、always程序塊和函數(shù)。接下來幾篇文章將探討每種編碼風(fēng)格,并推薦最佳實(shí)踐編碼風(fēng)格。

Part2同步和異步復(fù)位

在實(shí)現(xiàn)層面上,實(shí)際的觸發(fā)器可以是不可復(fù)位的(沒有復(fù)位輸入),也可以有一個(gè)復(fù)位輸入控制。復(fù)位控制可以與時(shí)鐘同步或異步,也可以是高電平或低電平控制。一些觸發(fā)器設(shè)備也有一個(gè)置位(有時(shí)稱為預(yù)置)輸入。每種類型的觸發(fā)器都有其優(yōu)點(diǎn)和缺點(diǎn)。這些工程上的權(quán)衡不在本文討論的范圍內(nèi),本文的重點(diǎn)是反映這些實(shí)現(xiàn)特點(diǎn)的RTL建模風(fēng)格。

| 注意事項(xiàng) |

|---|

| 特定的目標(biāo)ASIC或FPGA器件基本只支持一種類型的復(fù)位。 |

ASIC和FPGA在設(shè)備使用的復(fù)位類型上可能有所不同,這可能會(huì)影響RTL的建模風(fēng)格。特別是FPGA器件,通常只有一種復(fù)位類型的觸發(fā)器(也許是同步的、高電平的)。相反,許多ASIC器件和一些FPGA器件都有同步和異步觸發(fā)器可用。同樣地,一些器件只有復(fù)位輸入的觸發(fā)器,而其他器件也有置位和復(fù)位輸入的觸發(fā)器。

| 最佳實(shí)踐指南8-5 |

|---|

| 使用首選的復(fù)位類型編寫RTL模型,并讓綜合編譯器將復(fù)位功能映射到目標(biāo)ASIC或FPGA支持的復(fù)位類型。只有在有必要的情況下,才編寫RTL模型,以使用特定目標(biāo)ASIC或FPGA使用的相同類型的復(fù)位,從而實(shí)現(xiàn)該特定器件的最優(yōu)速度和面積。 |

許多RTL設(shè)計(jì)工程師,都是用一種預(yù)設(shè)的風(fēng)格或復(fù)位來建模,而不關(guān)心目標(biāo)器件支持什么。綜合編譯器可以將RTL模型中的任何類型的復(fù)位映射到目標(biāo)ASIC和FPGA器件中可用的任何類型的復(fù)位。例如,如果RTL模型使用主動(dòng)低電平復(fù)位,而目標(biāo)器件只有主動(dòng)高電平復(fù)位的觸發(fā)器,那么綜合編譯器將添加額外的門級邏輯來轉(zhuǎn)換RTL模型中使用的復(fù)位。如果RTL模型使用同步復(fù)位,而目標(biāo)器件只有異步復(fù)位的觸發(fā)器,那么綜合編譯器將在異步觸發(fā)器的外部添加額外的門級邏輯,使其與時(shí)鐘同步復(fù)位。FPGA有充足的速度和容量。可以得到一個(gè)功能齊全的設(shè)計(jì),而不必?fù)?dān)心綜合過程是否必須添加一些額外的邏輯,以將RTL風(fēng)格的復(fù)位映射到目標(biāo)器件的觸發(fā)器類型。

Part3不可復(fù)位的RTL觸發(fā)器模型

一個(gè)沒有復(fù)位輸入的觸發(fā)器只能通過數(shù)據(jù)輸入和時(shí)鐘來控制。RTL模型在每次程序觸發(fā)時(shí)將數(shù)據(jù)輸入轉(zhuǎn)移到觸發(fā)器的輸出。沒有任何if-else條件可能會(huì)指定數(shù)據(jù)輸入以外的值。一個(gè)不可復(fù)位的觸發(fā)器的RTL模型的例子是:

always_ff?@(posedge?clk)?q?<=?d;

當(dāng)綜合在一個(gè)特定的ASIC或FPGA目標(biāo)中實(shí)現(xiàn)這個(gè)RTL功能時(shí),將選擇該設(shè)備庫中可用的觸發(fā)器類型。這可能是一個(gè)沒有復(fù)位或置位輸入的觸發(fā)器,一個(gè)只有一個(gè)復(fù)位輸入的觸發(fā)器或一個(gè)置位和復(fù)位輸入都被關(guān)斷的觸發(fā)器。

Part4同步復(fù)位RTL觸發(fā)器模型

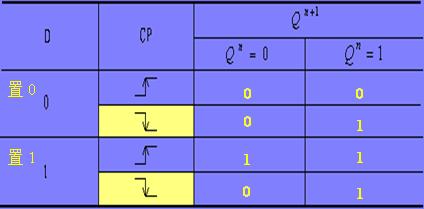

一個(gè)同步復(fù)位的觸發(fā)器有一個(gè)復(fù)位輸入,但該輸入只有在時(shí)鐘輸入被觸發(fā)時(shí)才被采樣。RTL模型包含一個(gè)if條件,當(dāng)復(fù)位激活時(shí)分配一個(gè)值,或者當(dāng)復(fù)位不激活時(shí)分支到else語句。復(fù)位信號不是always程序的靈敏度列表的一部分。靈敏度列表只包含觸發(fā)觸發(fā)器的時(shí)鐘沿。因此,always過程中的編程語句只在時(shí)鐘觸發(fā)發(fā)生時(shí)被評估。

下面的例子說明了一個(gè)具有主動(dòng)低電平同步復(fù)位的觸發(fā)器。

always_ff?@(po?sedge?clk) if?(!rstN)?q?<=?'0;?//?同步有源低電平復(fù)位 else?q?<=?d;

當(dāng)綜合將這個(gè)RTL功能映射到一個(gè)特定的FPGA目標(biāo)時(shí),如果有同步復(fù)位的觸發(fā)器,將選擇一個(gè)觸發(fā)器。如果目標(biāo)器件有高電平觸發(fā)器,綜合將為rstN信號添加一個(gè)反相器。如果目標(biāo)器件中沒有同步復(fù)位的觸發(fā)器,同步復(fù)位信號將與觸發(fā)器的數(shù)據(jù)輸入相加。任何時(shí)候復(fù)位都是有效的,一個(gè)0將被輸入到觸發(fā)器的時(shí)鐘中,這就提供了一個(gè)與時(shí)鐘同步的復(fù)位功能。如果目標(biāo)設(shè)備的觸發(fā)器也有異步復(fù)位或置位輸入,它們將被綁在一起,處于非活動(dòng)狀態(tài)。

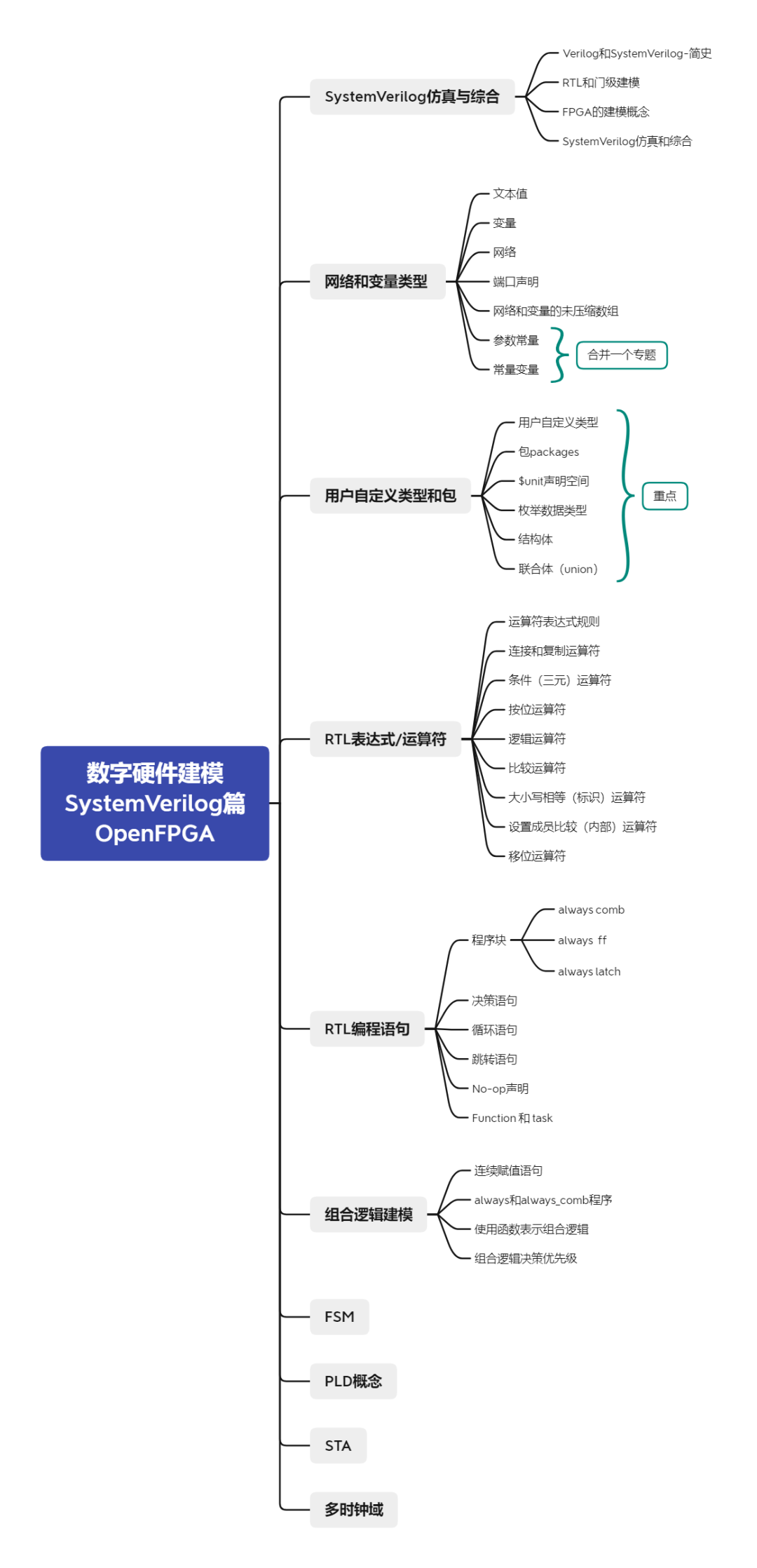

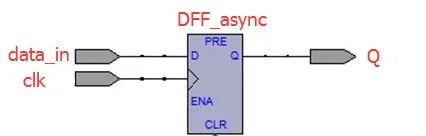

圖8-8顯示了針對通用觸發(fā)器的綜合結(jié)果,該器件具有同步復(fù)位觸發(fā)器,即Xilinx Virtex ?-7 ? FPGA。觸發(fā)器的復(fù)位是高電平有效,所以rstN輸入是反相的。

圖 8-7: 綜合結(jié)果。異步復(fù)位DFF映射到Xilinx Virtex -7 FPGA中

圖 8-7: 綜合結(jié)果。異步復(fù)位DFF映射到Xilinx Virtex -7 FPGA中

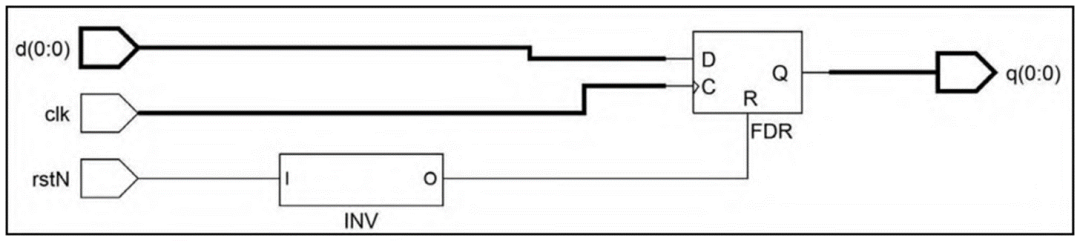

圖8-8顯示了將相同的通用觸發(fā)器定位到?jīng)]有同步復(fù)位觸發(fā)器的設(shè)備上的結(jié)果,即XilinxCoolRunner-11 CPLD。該觸發(fā)器的異步高電平有效CLR和PRE輸入沒有被使用。

圖8-8:綜合結(jié)果。映射到Xilinx CoolRunner-11 CPLD的異步復(fù)位

圖8-8:綜合結(jié)果。映射到Xilinx CoolRunner-11 CPLD的異步復(fù)位

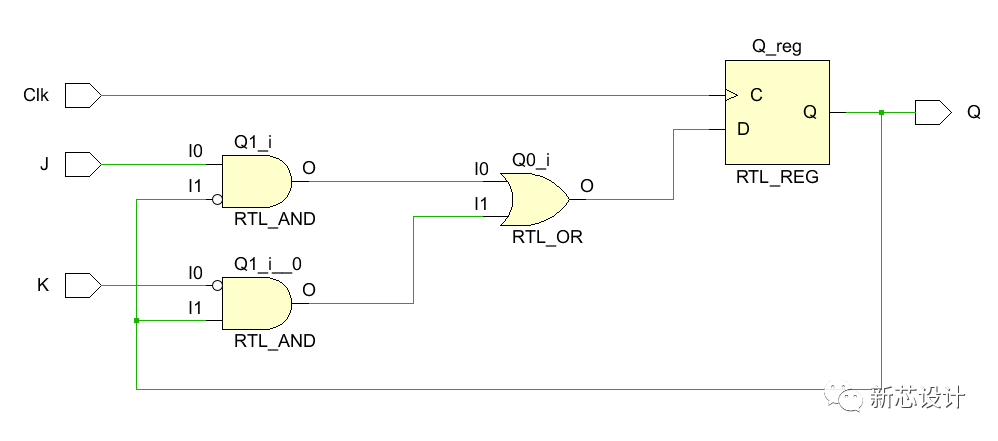

Part5異步復(fù)位RTL觸發(fā)器模型

一個(gè)具有異步復(fù)位的觸發(fā)器有一個(gè)復(fù)位控制輸入,在復(fù)位生效的那一刻將改變觸發(fā)器的狀態(tài),與時(shí)鐘無關(guān)。RTL模型的靈敏度列表包含了觸發(fā)觸發(fā)器的時(shí)鐘邊沿和復(fù)位信號的邊沿。因?yàn)閺?fù)位的邊沿在敏感度列表中,所以只要復(fù)位有效,always程序就會(huì)觸發(fā),而不需要等待時(shí)鐘輸入的變化。RTL模型包含一個(gè)if條件,當(dāng)復(fù)位激活時(shí)分配一個(gè)值,或者當(dāng)復(fù)位不激活時(shí)分支到else語句。

下面的例子模擬了一個(gè)具有主動(dòng)低電平異步復(fù)位的觸發(fā)器。

always_ff?@?(?posedgeclk?or?negedge?rstN) if?(!rstN)?q?<=?'0;?//?主動(dòng)低電平異步復(fù)位 else?q?<=?d;

忽略異步復(fù)位的尾部邊沿。always程序的一個(gè)綜合要求是,如果posedge或negedge被用于敏感度列表中的一個(gè)信號,那么必須為這個(gè)列表中的所有信號指定一個(gè)邊沿。下面的代碼片斷是不能綜合的,因?yàn)閞stN沒有用posedge或negedge限定。

always?@(posedge?clk?or?rstN)?//?incorrect?sensitivity? if?(!rstN)?q?<='0;?//?Asynchronous?active-low?reset? else?q?<=?d;

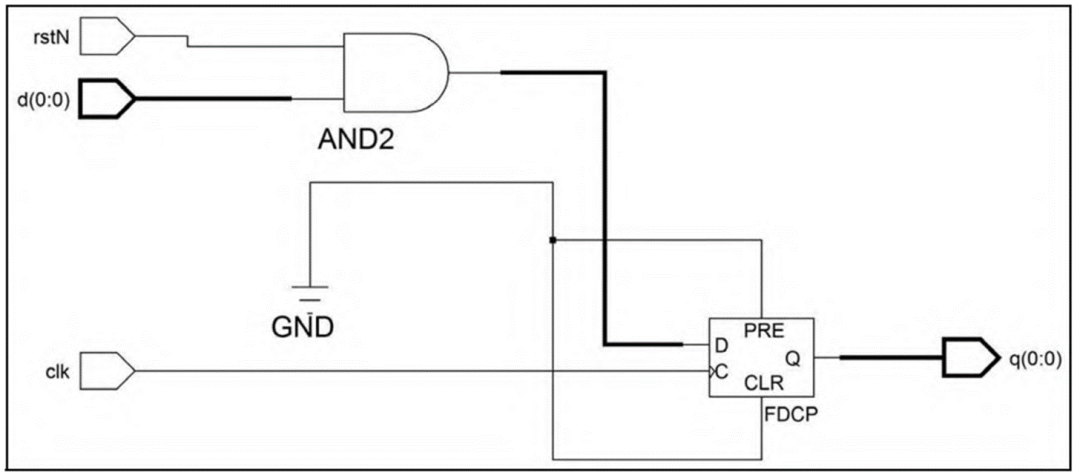

正確的行為還要求只有異步復(fù)位的邊沿被列在always程序的敏感度列表中。敏感度列表決定了always程序中的編程語句何時(shí)被執(zhí)行。對于異步復(fù)位,敏感度列表需要在復(fù)位激活時(shí)觸發(fā),以便立即復(fù)位觸發(fā)器。然而,如果always程序也在復(fù)位回到非活動(dòng)狀態(tài)時(shí)觸發(fā),那么復(fù)位活動(dòng)的if測試將評估為假,else分支將被執(zhí)行。在沒有時(shí)鐘邊沿的情況下,看起來就像發(fā)生了一個(gè)時(shí)鐘事件。圖8-9顯示了一個(gè)波形,說明了上述代碼片段的不正確的仿真行為。

圖8-9:不正確建模的異步復(fù)位結(jié)果的波形

圖8-9:不正確建模的異步復(fù)位結(jié)果的波形

仿真和綜合都要求在敏感列表中只包括異步復(fù)位的邊沿--仿真要求這樣做以獲得正確的異步復(fù)位行為,而綜合則在語法上要求這樣。SystemVerilog的語法并沒有強(qiáng)制執(zhí)行這個(gè)限制。

這是一種RTL編碼風(fēng)格,設(shè)計(jì)人員必須遵循。Lint檢查器可以檢查這個(gè)編碼風(fēng)格是否被遵循。

| 最佳實(shí)踐指南8-6 || :--------- | | -----------: || 在使用高電平或低電平復(fù)位時(shí)要保持一致。對高電平和低電平控制信號使用一致的命名規(guī)則。 |

雖然可以使用高電平或低電平復(fù)位,但項(xiàng)目中的所有RTL模型應(yīng)該是一致的。

混合的復(fù)位極性會(huì)導(dǎo)致代碼難以理解、維護(hù)和重用。

本文采用的慣例是在有低電平信號的名稱后面加上一個(gè)大寫的"N"。另一個(gè)常見的慣例是在有源低電平信號名稱后面加上"_n"。

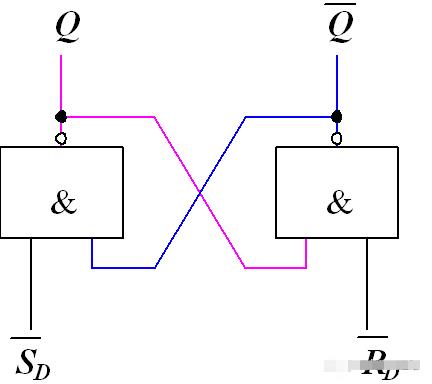

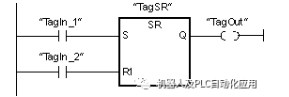

Part6異步置位-復(fù)位觸發(fā)器

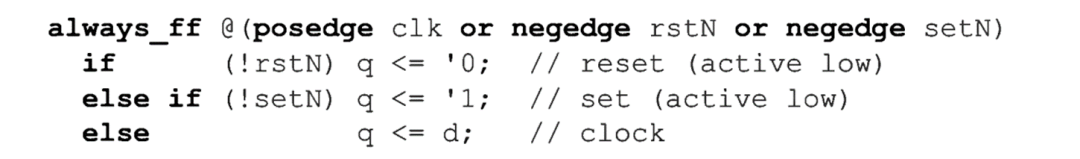

一些觸發(fā)器同時(shí)具有復(fù)位和置位控制輸入。一個(gè)if-else-if決策系列被用來模擬這種行為,如下面的例子。

一個(gè)if-else-if語句將優(yōu)先考慮被測試的第一個(gè)輸入。在上面的例子中,如果兩者同時(shí)激活,那么復(fù)位就會(huì)優(yōu)先于置位輸入。

| 注意事項(xiàng) |

|---|

| 在RTL模型中給予置位或復(fù)位輸入的優(yōu)先權(quán)應(yīng)與特定的目標(biāo)ASIC或FPGA器件相匹配。有些器件優(yōu)先考慮復(fù)位輸入,而其他器件則優(yōu)先考慮置位輸入。 |

| 最佳實(shí)踐指南8-7 |

|---|

| 為了達(dá)到最佳的綜合結(jié)果質(zhì)量(QoR),對RTL觸發(fā)器進(jìn)行建模,只需要一個(gè)復(fù)位輸入或一個(gè)置位輸入。如果設(shè)計(jì)的功能需要,只對置位/復(fù)位觸發(fā)器進(jìn)行建模。 |

如果需要一個(gè)置位/復(fù)位的觸發(fā)器行為,請為置位和復(fù)位編寫RTL模型的優(yōu)先級,以匹配設(shè)計(jì)將在其中實(shí)現(xiàn)的特定目標(biāo)器件的優(yōu)先級。由于并不是所有的目標(biāo)器件都有相同的置位/復(fù)位優(yōu)先級,因此很難編寫置位/復(fù)位觸發(fā)器RTL模型,就很難為所有目標(biāo)器件進(jìn)行最佳綜合。如果目標(biāo)器件沒有與RTL模型具有相同優(yōu)先級的置位/復(fù)位觸發(fā)器,綜合編譯器可以在觸發(fā)器之外添加額外的邏輯,使其與RTL模型相匹配。然而,這種額外的邏輯可能會(huì)影響器件的時(shí)序,并且在從復(fù)位狀態(tài)出來時(shí),會(huì)引起與設(shè)計(jì)中其他部分的競爭條件。

置位/復(fù)位觸發(fā)器對這些輸入也有更嚴(yán)格的建立和保持時(shí)間,而觸發(fā)器只有一個(gè)置位或復(fù)位輸入,但沒有兩個(gè)。即使RTL模型中置位和復(fù)位的優(yōu)先級與目標(biāo)器件的優(yōu)先級一致,設(shè)計(jì)人員也需要注意設(shè)計(jì)是否能滿足這些建立和保持時(shí)間要求。

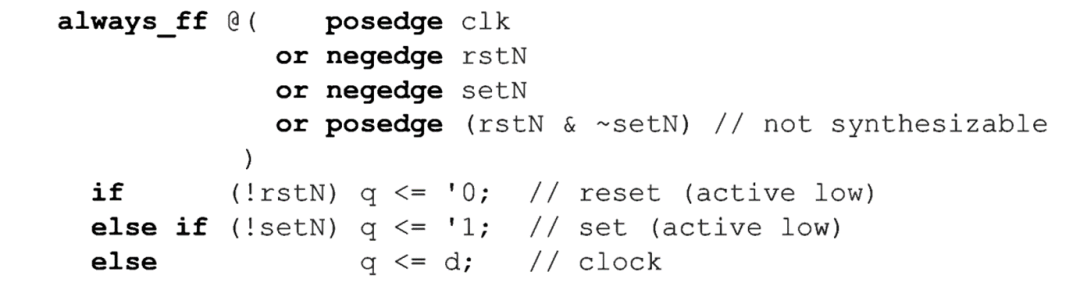

置位/復(fù)位觸發(fā)器的仿真故障。上面顯示的置位-復(fù)位觸發(fā)器RTL模型的例子在功能上是正確的,并且可以正確地進(jìn)行綜合。但是,這段代碼有一個(gè)潛在的仿真故障。如果setN和rstN的控制輸入同時(shí)有效,然后rstN變得無效,就會(huì)出現(xiàn)這種故障。在這個(gè)例子中,rstN具有優(yōu)先權(quán),并且觸發(fā)器正確復(fù)位。當(dāng)rstN輸入變得不活躍,setN輸入應(yīng)該接管,并且觸發(fā)器應(yīng)該切換到其置位狀態(tài)。仿真中的故障是,RTL模型只對rstN的前邊沿敏感--這 ?是 ?綜合編譯器的要求--而對rstN的前后邊沿不敏感。當(dāng)rstN變得不活躍時(shí),敏感度列表將不會(huì)觸發(fā),因此錯(cuò)過了置位觸發(fā)器,即使setN仍然活躍。這個(gè)故障只持續(xù)到時(shí)鐘的下一個(gè)正邊沿,它將觸發(fā)always程序,并導(dǎo)致該程序被重新評估。

防止這種仿真故障的辦法是將復(fù)位的后邊沿添加到靈敏度列表中。然而,僅僅增加復(fù)位的后邊沿會(huì)導(dǎo)致前面描述的同樣問題,即復(fù)位的后邊沿可以作為一個(gè)時(shí)鐘。因此,復(fù)位輸入的非活動(dòng)電平需要與置位輸入的活動(dòng)電平相加,當(dāng)該結(jié)果為真時(shí),靈敏度列表將被觸發(fā)。

為防止仿真故障,修訂后的敏感度列表為:

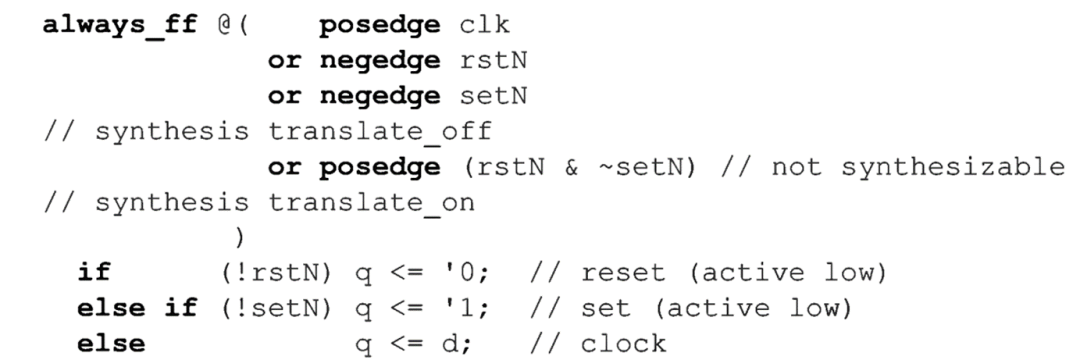

對表達(dá)式的結(jié)果進(jìn)行觸發(fā)在SystemVerilog語言中是合法的,但綜合編譯器不允許。為了避免仿真故障,需要從綜合中隱藏額外的觸發(fā)。這可以通過使用綜合的translate_off/translate_on pragmas來實(shí)現(xiàn)。綜合語是以synthesis一詞開頭的特殊語句。仿真器會(huì)忽略這些注釋,但綜合編譯器會(huì)對它們采取行動(dòng)。下面的片段添加了translate_off/translate_on語句。

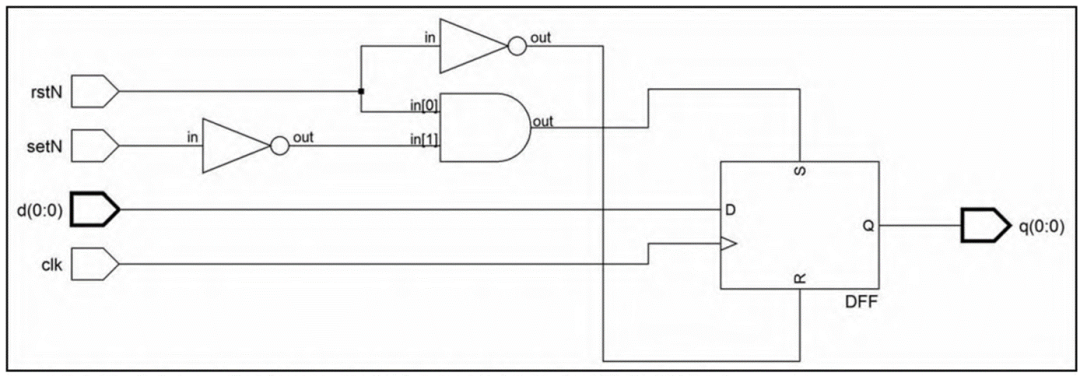

圖8-12顯示了綜合這個(gè)置位-復(fù)位觸發(fā)器代碼的結(jié)果。

圖8-12:一個(gè)異步置位-復(fù)位觸發(fā)器的綜合結(jié)果

圖8-12:一個(gè)異步置位-復(fù)位觸發(fā)器的綜合結(jié)果

請注意,綜合編譯器在通用觸發(fā)器的set輸入之前添加了額外的邏輯,以強(qiáng)制執(zhí)行rstN比setN有優(yōu)先權(quán)。如果目標(biāo)ASIC或FPGA設(shè)備有set/reset觸發(fā)器,其中reset優(yōu)先于set,那么當(dāng)通用觸發(fā)器被映射到ASIC或FPGA時(shí),這個(gè)附加邏輯將被刪除。否則,附加邏輯將被保留,以便ASIC或FPGA實(shí)現(xiàn)與RTL模型相匹配。

在針對特定的ASIC或FPGA之前,綜合編譯器使用的通用觸發(fā)器具有高電平有效的置位和復(fù)位輸入。因此,綜合編譯器在RTL模型中對有源低電平信號添加了反相器。如果目標(biāo)器件具有低電平有效的控制輸入,這些反相器將被刪除。

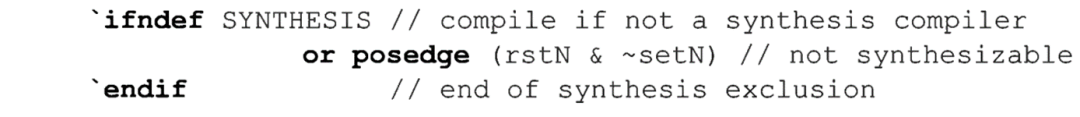

使用translate_off和translate_on綜合pragmas的另一種方法是使用條件編譯。大多數(shù)綜合編譯器都有一個(gè)預(yù)定義的SYNTHESIS宏,可以用來有條件地包括或排除綜合工具所編譯的代碼。要排除前面例子中的不可綜合的那一行,代碼應(yīng)該是。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論