一、JK 觸發器的 Verilog 代碼實現和 RTL 電路實現

module JK_FF(

input wire Clk,

input wire J,

input wire K,

output reg Q

);

// 公式

always @(posedge Clk) begin

Q <= (J&(~Q))|((~K)&Q);

end

// 查找表

// always @(posedge Clk)

// case({J,K})

// 2'b00: Q <= Q;

// 2'b01: Q <= 0;

// 2'b10: Q <= 1;

// 2'b11: Q <= ~Q;

// endcase

endmodule

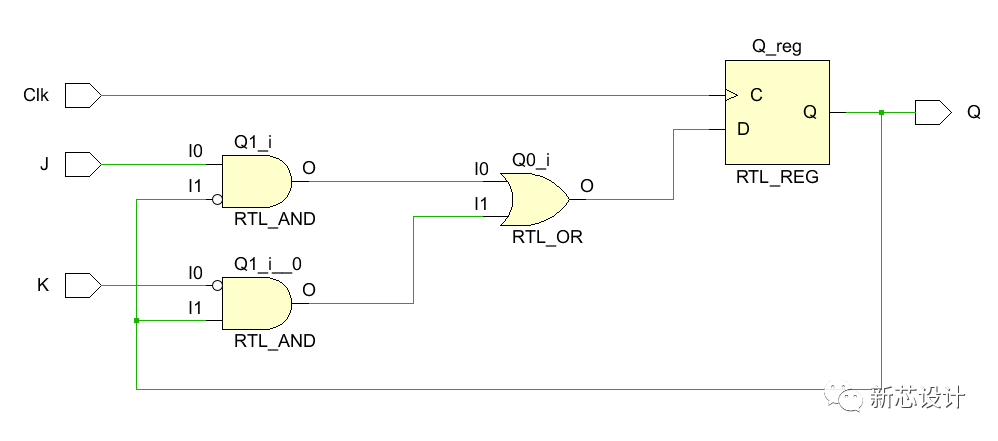

JK 觸發器的 RTL 電路圖如下所示:

JK 觸發器的 RTL 電路圖

二、T 觸發器的 Verilog 代碼實現和 RTL 電路實現

module T_FF(

input wire Clk,

input wire T,

output reg Q

);

// 公式

always @(posedge Clk) begin

Q <= (T&(~Q))|((~T)&Q);

end

// 查找表

// always @(posedge Clk)

// if(t)

// Q <= ~Q;

// else

// Q <= Q;

endmodule

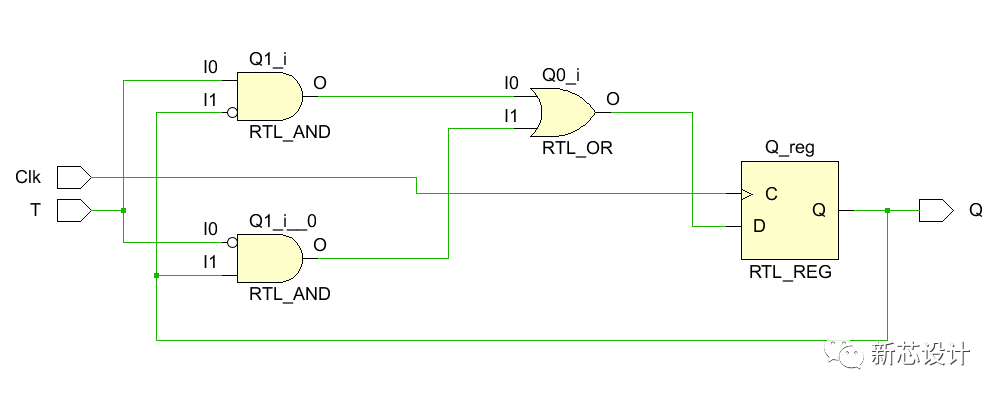

T 觸發器的 RTL 電路圖如下所示:

T 觸發器的 RTL 電路圖

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

RTL

+關注

關注

1文章

388瀏覽量

60653 -

JK觸發器

+關注

關注

1文章

44瀏覽量

16221 -

觸發器

+關注

關注

14文章

2032瀏覽量

61860 -

Verilog設計

+關注

關注

0文章

20瀏覽量

6612

發布評論請先 登錄

相關推薦

熱點推薦

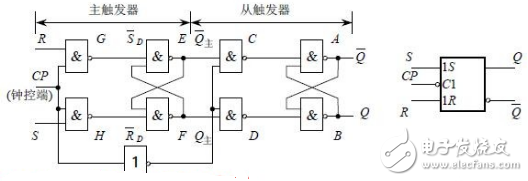

主從jk觸發器和邊沿jk觸發器的區別

主從JK觸發器和邊沿JK觸發器是數字電路中常用的存儲元件,它們在功能和應用上既有相似之處,也存在顯著的區別。以下將從多個方面介紹這兩種

JK觸發器與T觸發器的Verilog代碼實現和RTL電路實現

JK觸發器與T觸發器的Verilog代碼實現和RTL電路實現

評論