時序邏輯電路

一:觸發器

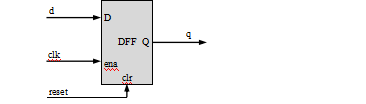

1:D觸發器:時序邏輯電路最小單元。

(1):D觸發器工作原理

忽略清零端情況下:當使能條件(往往為時鐘的觸發沿:上升沿/下降沿)滿足時,將輸入D端的數據給到輸出Q,當使能條件不滿足時,輸入數據D會暫存在觸發器當中,直到觸發條件滿足才給到輸出Q。

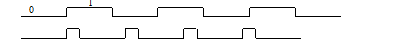

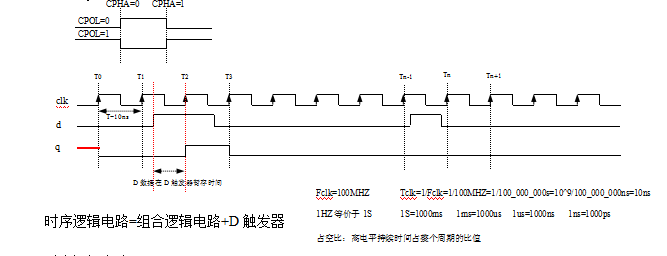

(2):D觸發器工作時序

時鐘clk:周期性變化信號。

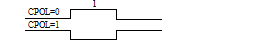

時鐘極性(CPOL):時鐘初始值是0,時鐘極性為0;時鐘初始值是1,時鐘極性為1。

時鐘相位(CPHA):出現第一個沿,時鐘相位為0;出現第二個沿,時鐘相位為1。

時序邏輯電路=組合邏輯電路+D觸發器

二:時序邏輯電路

1:時序邏輯電路概念:

2:時序邏輯電路建模采用行為建模

以“always”為關鍵字出現,不僅可以描述組合邏輯電路;也可以描述時序邏輯電路。

(1):如果描述的是組合邏輯電路,表示形式為always @ (電平信號),一般可以寫成:always @ (A0,A1,A2)/always @ (*)----組合邏輯電路

所有的組合邏輯電路賦值方式全部為阻塞賦值(“=”);

所有在always塊中位于賦值號左側信號必須定義為寄存器型(“reg”)。

(2):如果描述的是時序邏輯電路,表示形式為always @ (posedge clk)/always @ (negedge clk)。

always @ (posedge clk, negedge rst_n)----異步復位

always @ (posedge clk)----同步復位

所有的時序邏輯電路賦值方式全部為非阻塞賦值(“<=”);

所有在always塊中位于賦值號左側信號必須定義為寄存器型(“reg”)。

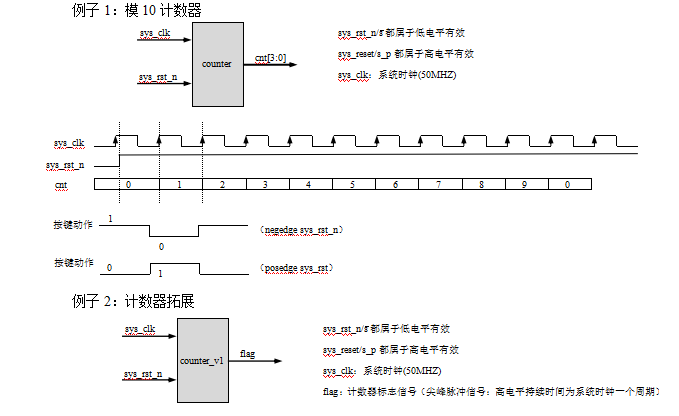

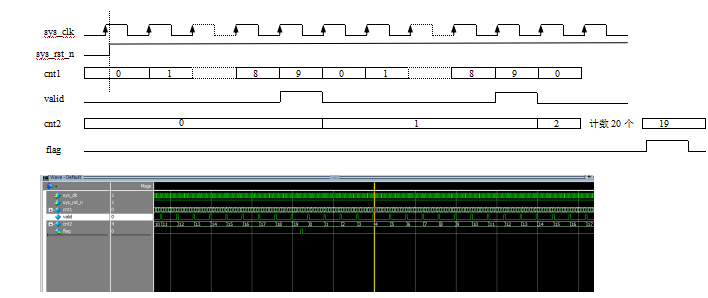

三:時序邏輯電路實例

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA學習-時序邏輯電路

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1645文章

22046瀏覽量

618296

原文標題:FPGA學習-時序邏輯電路

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA學習-時序邏輯電路

FPGA學習-時序邏輯電路

評論