時(shí)序邏輯電路是數(shù)字電路中的一種重要類型,它具有存儲(chǔ)功能,能夠根據(jù)輸入信號(hào)和內(nèi)部狀態(tài)的變化來改變其輸出。時(shí)序邏輯電路廣泛應(yīng)用于計(jì)算機(jī)、通信、控制等領(lǐng)域。本文將介紹時(shí)序邏輯電路的描述方法,包括狀態(tài)圖、狀態(tài)表、有限狀態(tài)機(jī)、卡諾圖、布爾差分方程、布爾函數(shù)、時(shí)序邏輯仿真等。

- 狀態(tài)圖

狀態(tài)圖是一種圖形化的描述方法,用于表示時(shí)序邏輯電路的狀態(tài)轉(zhuǎn)換關(guān)系。狀態(tài)圖由節(jié)點(diǎn)和有向邊組成,節(jié)點(diǎn)表示電路的狀態(tài),有向邊表示狀態(tài)之間的轉(zhuǎn)換。狀態(tài)圖的繪制步驟如下:

1.1 確定狀態(tài)集合:首先需要確定電路的所有可能狀態(tài),并將它們表示為狀態(tài)集合。

1.2 確定初始狀態(tài):在狀態(tài)集中選擇一個(gè)狀態(tài)作為初始狀態(tài)。

1.3 確定輸入變量:確定電路的輸入變量,它們將影響狀態(tài)轉(zhuǎn)換。

1.4 繪制狀態(tài)轉(zhuǎn)換:根據(jù)電路的邏輯功能,繪制狀態(tài)之間的轉(zhuǎn)換關(guān)系。對(duì)于每個(gè)狀態(tài),列出所有可能的輸入變量組合,并確定它們對(duì)應(yīng)的下一個(gè)狀態(tài)。

1.5 標(biāo)注狀態(tài)轉(zhuǎn)換條件:在有向邊旁邊標(biāo)注狀態(tài)轉(zhuǎn)換的條件,通常使用布爾表達(dá)式表示。

1.6 檢查狀態(tài)圖的完整性:確保狀態(tài)圖包含了所有可能的狀態(tài)轉(zhuǎn)換。

- 狀態(tài)表

狀態(tài)表是一種表格化的描述方法,用于表示時(shí)序邏輯電路的狀態(tài)轉(zhuǎn)換關(guān)系。狀態(tài)表通常包括以下幾列:當(dāng)前狀態(tài)、輸入變量、輸出變量和下一個(gè)狀態(tài)。狀態(tài)表的編制步驟如下:

2.1 確定狀態(tài)集合:與狀態(tài)圖相同,首先確定電路的所有可能狀態(tài)。

2.2 列出輸入變量:確定電路的輸入變量,并在狀態(tài)表的左側(cè)列出它們。

2.3 列出輸出變量:確定電路的輸出變量,并在狀態(tài)表的右側(cè)列出它們。

2.4 填充狀態(tài)表:對(duì)于每個(gè)狀態(tài)和輸入變量的組合,確定下一個(gè)狀態(tài)和輸出變量,并將它們填入狀態(tài)表中。

2.5 檢查狀態(tài)表的完整性:確保狀態(tài)表包含了所有可能的狀態(tài)轉(zhuǎn)換。

- 有限狀態(tài)機(jī)(FSM)

有限狀態(tài)機(jī)是一種抽象的計(jì)算模型,用于描述時(shí)序邏輯電路的狀態(tài)轉(zhuǎn)換關(guān)系。有限狀態(tài)機(jī)由一組狀態(tài)、一組輸入變量、一組輸出變量和一組狀態(tài)轉(zhuǎn)換規(guī)則組成。有限狀態(tài)機(jī)的描述方法包括:

3.1 確定狀態(tài)集合:與狀態(tài)圖和狀態(tài)表相同,首先確定電路的所有可能狀態(tài)。

3.2 確定初始狀態(tài):在狀態(tài)集中選擇一個(gè)狀態(tài)作為初始狀態(tài)。

3.3 確定輸入變量:確定電路的輸入變量,它們將影響狀態(tài)轉(zhuǎn)換。

3.4 確定輸出變量:確定電路的輸出變量,它們將根據(jù)狀態(tài)轉(zhuǎn)換結(jié)果產(chǎn)生。

3.5 確定狀態(tài)轉(zhuǎn)換規(guī)則:根據(jù)電路的邏輯功能,確定狀態(tài)轉(zhuǎn)換規(guī)則。狀態(tài)轉(zhuǎn)換規(guī)則通常使用布爾表達(dá)式表示。

3.6 描述有限狀態(tài)機(jī):使用狀態(tài)圖或狀態(tài)表描述有限狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換關(guān)系。

- 卡諾圖

卡諾圖是一種圖形化的優(yōu)化方法,用于簡(jiǎn)化布爾函數(shù)。卡諾圖的繪制步驟如下:

4.1 列出布爾函數(shù)的真值表:首先列出布爾函數(shù)的所有可能輸入組合及其對(duì)應(yīng)的輸出值。

4.2 繪制卡諾圖:根據(jù)輸入變量的數(shù)量,繪制相應(yīng)大小的卡諾圖。卡諾圖由單元格組成,每個(gè)單元格對(duì)應(yīng)一個(gè)輸入組合。

4.3 標(biāo)記1值:在卡諾圖中,將真值表中的1值對(duì)應(yīng)的單元格標(biāo)記出來。

4.4 尋找覆蓋1值的最小集合:在卡諾圖中,尋找能夠覆蓋所有1值的最小單元格集合。這些單元格集合可以共享邊或頂點(diǎn)。

4.5 簡(jiǎn)化布爾函數(shù):使用找到的最小單元格集合,構(gòu)造簡(jiǎn)化后的布爾函數(shù)。

- 布爾差分方程

布爾差分方程是一種代數(shù)化的描述方法,用于表示時(shí)序邏輯電路的狀態(tài)轉(zhuǎn)換關(guān)系。布爾差分方程的建立步驟如下:

5.1 確定狀態(tài)變量:首先確定電路的狀態(tài)變量,它們將表示電路的狀態(tài)。

5.2 確定輸入變量:確定電路的輸入變量,它們將影響狀態(tài)轉(zhuǎn)換。

5.3 建立狀態(tài)方程:根據(jù)電路的邏輯功能,建立狀態(tài)變量與輸入變量之間的關(guān)系,通常使用布爾表達(dá)式表示。

5.4 建立輸出方程:根據(jù)狀態(tài)變量和輸入變量,建立輸出變量與它們之間的關(guān)系,通常使用布爾表達(dá)式表示。

5.5 求解布爾差分方程:使用布爾代數(shù)的運(yùn)算規(guī)則,求解布爾差分方程,得到電路的狀態(tài)轉(zhuǎn)換關(guān)系。

-

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1639瀏覽量

81903 -

時(shí)序邏輯電路

+關(guān)注

關(guān)注

2文章

94瀏覽量

16851 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4380瀏覽量

64844 -

輸入信號(hào)

+關(guān)注

關(guān)注

0文章

473瀏覽量

12892

發(fā)布評(píng)論請(qǐng)先 登錄

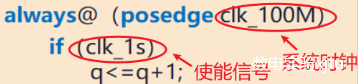

如何使用Verilog硬件描述語言描述時(shí)序邏輯電路?

同步時(shí)序邏輯電路

異步時(shí)序邏輯電路

組合邏輯電路和時(shí)序邏輯電路比較_組合邏輯電路和時(shí)序邏輯電路有什么區(qū)別

時(shí)序邏輯電路分析有幾個(gè)步驟(同步時(shí)序邏輯電路的分析方法)

時(shí)序邏輯電路由什么組成_時(shí)序邏輯電路特點(diǎn)是什么

時(shí)序邏輯電路的分析方法

時(shí)序邏輯電路的描述方法有哪些

時(shí)序邏輯電路的描述方法有哪些

評(píng)論