在FPGA 上設(shè)計(jì)一個(gè)高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項(xiàng)巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡(luò)都是運(yùn)行在一個(gè)單一時(shí)鐘下。隨著FPGA 技術(shù)的發(fā)展,Xilinx 公司推出了Virtex-4 平臺(tái)

2011-10-21 16:13:51 1270

1270

針對(duì)不同類(lèi)型的器件,Xilinx公司提供的全局時(shí)鐘網(wǎng)絡(luò)在數(shù)量、性能等方面略有區(qū)別,下面以Virtex-4系列芯片為例,簡(jiǎn)單介紹FPGA全局時(shí)鐘網(wǎng)絡(luò)結(jié)構(gòu)。

2013-11-28 18:49:00 12149

12149

腳CLKFB上。另外,在FPGA里,只有BUFG的輸出引腳接在時(shí)鐘網(wǎng)絡(luò)上,所以一般來(lái)說(shuō)你可以不使用DCM,但你一定會(huì)使用BUFG。有些兄弟總喜歡直接將外部輸入的時(shí)鐘驅(qū)動(dòng)內(nèi)部的寄存器,其實(shí)這個(gè)時(shí)候雖然你沒(méi)有明顯地例化BUFG,但工具會(huì)自動(dòng)給你加上的。

2018-05-11 03:53:00 1566

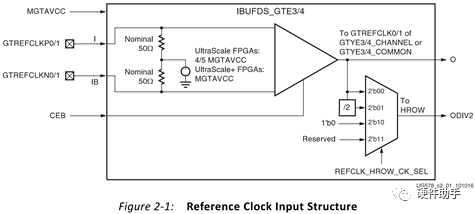

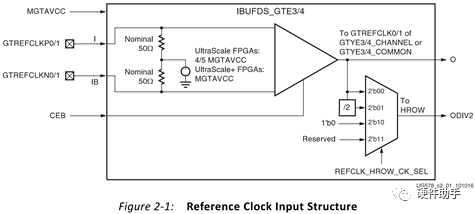

1566 本文主要介紹Xilinx FPGA的GTx的參考時(shí)鐘。下面就從參考時(shí)鐘的模式、參考時(shí)鐘的選擇等方面進(jìn)行介紹。 參考時(shí)鐘的模式 參考時(shí)鐘可以配置為輸入模式也可以是輸出模式,但是在運(yùn)行期間不能切換。作為

2020-11-14 11:39:15 13866

13866

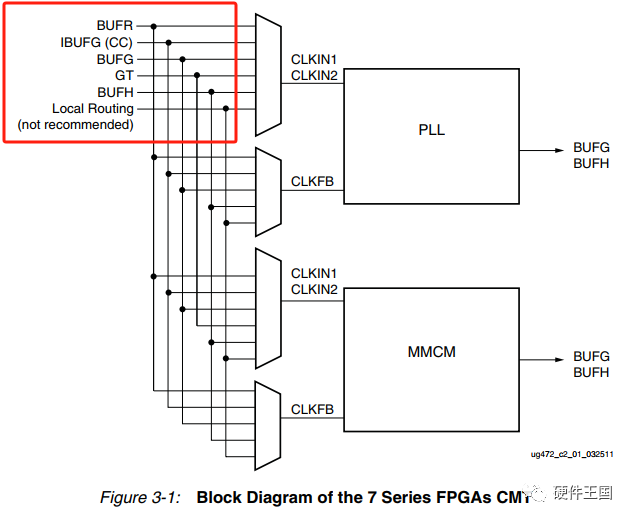

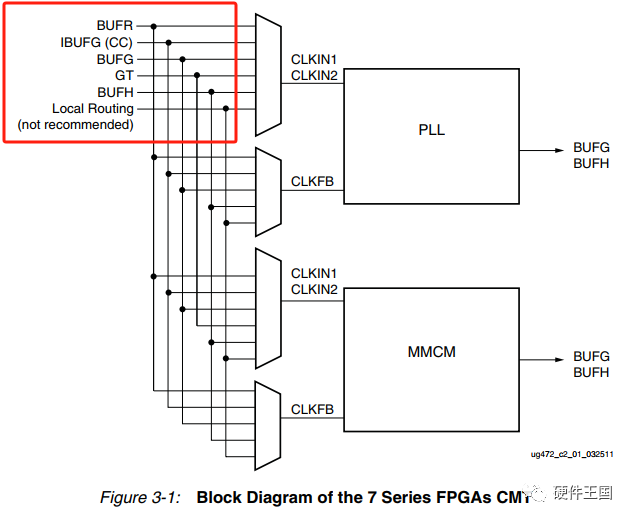

7系列FPGA擁有豐富的時(shí)鐘資源。各種緩沖器類(lèi)型、時(shí)鐘輸入管腳和時(shí)鐘連接,可以滿足許多不同的應(yīng)用需求。選擇合適的時(shí)鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 鎖相環(huán)基本上是每一個(gè)fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時(shí)鐘資源對(duì)xilinx fpga的底層時(shí)鐘資源做過(guò)說(shuō)明,但是對(duì)于fpga的應(yīng)用來(lái)說(shuō),使用Clocking Wizard IP時(shí)十分方便的。

2023-06-12 17:42:03 2883

2883

上文XILINX FPGA IP之Clocking Wizard詳解說(shuō)到時(shí)鐘IP的支持動(dòng)態(tài)重配的,本節(jié)介紹通過(guò)DRP進(jìn)行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

。Xilinx FPGA7系列分為全局時(shí)鐘(Global clock)和局部時(shí)鐘(Regional clock)資源。目前,大型設(shè)計(jì)一般推薦使用同步時(shí)序電路。同步時(shí)序電路基于時(shí)鐘觸發(fā)沿設(shè)計(jì),對(duì)時(shí)鐘的周期

2023-07-24 11:07:04 655

655

通過(guò)上一篇文章“時(shí)鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時(shí)鐘、區(qū)域時(shí)鐘、時(shí)鐘管理塊(CMT)。 通過(guò)以上時(shí)鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時(shí)鐘分配

2023-08-31 10:44:31 1032

1032

本文主要介紹Xilinx FPGA的GTx的參考時(shí)鐘。下面就從參考時(shí)鐘的模式、參考時(shí)鐘的選擇等方面進(jìn)行介紹。

2023-09-15 09:14:26 1956

1956

7系列FPGA包含最多24個(gè)CMT塊,CMT具體的分布和與其他時(shí)鐘資源的關(guān)系請(qǐng)參考本合集(FPGA應(yīng)用開(kāi)發(fā))的上一篇文章。本文主要介紹CMT內(nèi)部MMCM和PLL的區(qū)別以及在實(shí)際開(kāi)發(fā)中怎么使用CMT,怎么實(shí)現(xiàn)跨時(shí)鐘區(qū)域,第一次讀者最好先閱讀上一篇文章——解剖時(shí)鐘結(jié)構(gòu)篇。

2023-11-17 17:08:11 1347

1347

FPGA中的BUFGCE_DIV/BUFG_GT以及Versal中的MBUFG/BUFG_GT等。對(duì)于這類(lèi)時(shí)鐘,Vivado會(huì)自動(dòng)創(chuàng)建時(shí)鐘,并不需要用戶手工通過(guò)create_generated_clock創(chuàng)建。

2024-01-11 09:50:09 400

400

我有2個(gè)時(shí)鐘輸入通過(guò)一個(gè)支持時(shí)鐘的IO對(duì)(AN19和AN20)進(jìn)入FPGA。時(shí)鐘輸入具有相同的頻率,但不同相。是否可以通過(guò)他們自己的IODELAY和BUFIO來(lái)分配每個(gè)本地時(shí)鐘網(wǎng)絡(luò)?我希望一個(gè)時(shí)鐘

2020-05-29 15:52:06

7 series FPGAs MultiBoot功能指讓FPGA從2個(gè)或者多個(gè)BIT文件中加載一個(gè)BIT文件運(yùn)行程序,本文檔介紹基于個(gè)人參考設(shè)計(jì)例程K7MultiBoot的應(yīng)用筆記

2019-04-05 00:25:27

嗨,我想了解7系列收發(fā)器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

大家好,對(duì)于BUFG-BUFG級(jí)聯(lián)對(duì)錯(cuò)誤,我有[Place 30-120]次優(yōu)放置。我知道錯(cuò)誤的發(fā)生是因?yàn)?b class="flag-6" style="color: red">BUFG無(wú)法級(jí)聯(lián)...請(qǐng)參閱下面的“有問(wèn)題”邏輯。如您所見(jiàn),時(shí)鐘多路復(fù)用器的輸出連接到時(shí)鐘

2018-10-29 14:20:35

的所有可配置單元(CLB)、I/O 單元(IOB)和選擇性塊 RAM(Block Select RAM)的時(shí)延和抖動(dòng)都為最小。為了適應(yīng)復(fù)雜設(shè)計(jì)的需要,Xilinx 的 FPGA 中集成的專(zhuān)用時(shí)鐘資源

2014-11-24 17:58:10

四、時(shí)鐘資源介紹4.1 BUFG BUFG在“Device”中如圖2-1-1所示,其中它有多種模式可根據(jù)需求來(lái)選擇使用,可以實(shí)現(xiàn)將時(shí)鐘傳遞到FPGA中的各種資源,具體架構(gòu)在上文已做闡述,本文

2022-01-06 08:21:32

嗨,我收到了來(lái)自ISE的警告信息。這導(dǎo)致BUFIO2的輸入信號(hào)無(wú)法路由。“警告:放置:1137- 此設(shè)計(jì)不保證可路由!此設(shè)計(jì)包含一個(gè)全局緩沖實(shí)例,驅(qū)動(dòng)網(wǎng)絡(luò),驅(qū)動(dòng)以下(前30個(gè))非時(shí)鐘源引腳。這不是

2019-05-29 09:57:25

FPGA 時(shí)鐘分配網(wǎng)絡(luò)設(shè)計(jì)技術(shù)

2012-08-20 17:15:27

現(xiàn)了,將時(shí)鐘的布線成樹(shù)形結(jié)構(gòu),使得到達(dá)每一個(gè)邏輯單元的時(shí)鐘信號(hào)同相,這樣就可以實(shí)現(xiàn)同步,這就是全局時(shí)鐘網(wǎng)絡(luò),GC_CLK。也就是說(shuō)GC_CLK在FPGA內(nèi)部是固定的位置,與其對(duì)應(yīng)的引腳也就固定了,這樣

2019-07-09 08:00:00

,FPGA上的全局時(shí)鐘管腳用完了就出現(xiàn)不夠用的情況。FPGA全局時(shí)鐘約束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

數(shù)據(jù)或控制信號(hào)跟隨損壞。我們將從 7 系列FPGA開(kāi)始我們的旅程。當(dāng)我們考慮時(shí)鐘規(guī)劃時(shí),我們需要確保使用設(shè)備內(nèi)最合適的資源并了解其內(nèi)部時(shí)鐘架構(gòu)。我們只需要簡(jiǎn)單的確保時(shí)鐘信號(hào)連接到 IO 上適當(dāng)?shù)?b class="flag-6" style="color: red">時(shí)鐘引腳

2022-10-08 15:28:35

Xilinx 7系列FPGA簡(jiǎn)介--選型參考

2021-02-01 06:10:55

/O管腳分析,可以參考表1-1管腳定義說(shuō)明。2.Xilinx7系列FPGA管腳Pinout文件下載我們?cè)谶M(jìn)行原理圖庫(kù)設(shè)計(jì)時(shí),如何獲得FPGA每個(gè)管腳定義呢?在UG475官方文檔第二章7 Series

2021-05-28 09:23:25

/O管腳分析,可以參考表1-1管腳定義說(shuō)明。2.Xilinx7系列FPGA管腳Pinout文件下載我們?cè)谶M(jìn)行原理圖庫(kù)設(shè)計(jì)時(shí),如何獲得FPGA每個(gè)管腳定義呢?在UG475官方文檔第二章7 Series

2021-07-08 08:00:00

Xilinx FPGA配置clocking時(shí)鐘動(dòng)態(tài)相位輸出

2019-08-05 11:35:39

? Zynq? 7000 series (XC7Z045)FPGA.This design uses several LMZ3 series modules, LDOs, and a DDR

2018-11-05 16:42:31

xilinx公司的7系列FPGA應(yīng)用指南

2012-08-14 12:17:40

xilinx和altera區(qū)別分析1. 從好用來(lái)說(shuō),肯定是Xilinx的好用,不過(guò)Altera的便宜他們的特點(diǎn),Xilinx的短線資源非常豐富,這樣在實(shí)現(xiàn)的時(shí)候,布線的成功率很高,尤其是邏輯做得比較

2012-02-28 14:40:59

我在CZ7020-484引腳FPGA上出現(xiàn)了時(shí)鐘放置錯(cuò)誤。我們?cè)谝_V4,V5上放置了一個(gè)bufgds(差分時(shí)鐘輸入)通過(guò)BUFIO時(shí)鐘緩沖器。Vivado抱怨錯(cuò)誤消息12-1411說(shuō)bufgds的位置與bufio的位置有沖突。我不知道如何解決這個(gè)問(wèn)題。 sombody可以提供一些提示嗎?

2020-05-21 14:06:55

BUFIO2的SDR時(shí)鐘輸入的文檔),錯(cuò)誤就消失了......我有點(diǎn)困惑可能導(dǎo)致錯(cuò)誤發(fā)生的原因。我當(dāng)然不是專(zhuān)家,但在根據(jù)Xilinx文檔進(jìn)行檢查時(shí),我發(fā)現(xiàn)設(shè)計(jì)沒(méi)有任何問(wèn)題。為了增加更多的混淆,即使在項(xiàng)目

2018-10-17 12:00:23

上,BUFG的輸出引腳反饋回來(lái)接在DCM的反饋時(shí)鐘腳CLKFB上。另外,在FPGA里,只有BUFG的輸出引腳接在時(shí)鐘網(wǎng)絡(luò)上,所以一般來(lái)說(shuō)你可以不使用DCM,但你一定會(huì)使用BUFG。DCM,是Xilinx

2018-08-31 09:08:22

嗨Spartan-6時(shí)鐘專(zhuān)家, 我遇到了一個(gè)稍微令人煩惱的問(wèn)題,我認(rèn)為我可以在設(shè)計(jì)中使用任何GCLK引腳作為反饋引腳,利用DCM將時(shí)鐘偏移到外部反饋焊盤(pán)。但是,我太天真了,BUFIO2FB位置(右

2019-06-27 07:31:14

時(shí)鐘。是否有可能強(qiáng)制使用HPC?我是否需要在每個(gè)時(shí)鐘區(qū)域?qū)嵗粋€(gè)MMCM以確保使用HPC?在這種情況下,如何將50MHz輸入時(shí)鐘連接到所有MMCM?簡(jiǎn)而言之:哪種設(shè)置最適合將低抖動(dòng)時(shí)鐘轉(zhuǎn)發(fā)到ADC和DAC?在任何一種情況下,我需要實(shí)例化哪些BUFG / BUFIO?提前謝謝了,基督教

2020-06-16 08:34:58

) - > bufio2_fb- > pll |- (5) -| ---(6)--- | -------(7)---- | ----(8)--- | 延遲時(shí)間顯示在fpga編輯器中: T5

2019-07-29 14:53:19

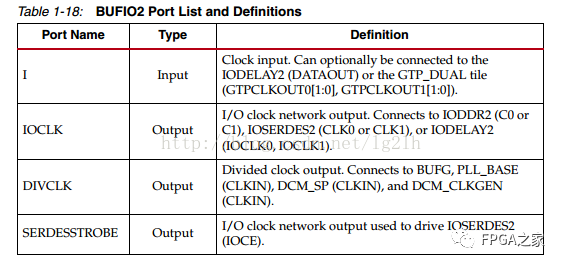

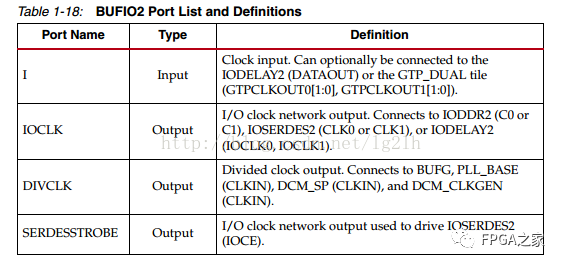

大家好。BUFG資源和DCM / PLL模塊在許多FPGA線路上使用專(zhuān)用時(shí)鐘布線資源。對(duì)于SerDes應(yīng)用,我們使用BUFIO2來(lái)獲得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

/ BUFIO時(shí)鐘組件對(duì)未放置在可路由時(shí)鐘IOB / BUFIO站點(diǎn)對(duì)上。時(shí)鐘IOB組件放置在現(xiàn)場(chǎng)。 BUFIO組件位于站點(diǎn)。每個(gè)BUFIO站點(diǎn)都有一組可以驅(qū)動(dòng)它的IOB。如果未使用這些IOB,則連接不可路由

2019-06-26 08:24:03

引言:本文我們介紹Xilinx 7系列FPGA收發(fā)器硬件設(shè)計(jì)主要注意的一些問(wèn)題,指導(dǎo)硬件設(shè)計(jì)人員進(jìn)行原理圖及PCB設(shè)計(jì)。本文介紹以下內(nèi)容:GTX/GTH收發(fā)器管腳概述GTX/GTH收發(fā)器時(shí)鐘

2021-11-11 07:42:37

.O u_fpga_dut_clk / rg3_bufg.O.34562錯(cuò)誤:[放置30-660]全局時(shí)鐘刺激超額訂閱。以下時(shí)鐘網(wǎng)絡(luò)需要在SLR 3中使用全局時(shí)鐘脊柱18:u_fpga

2018-10-24 15:27:38

RAM)的時(shí)延和抖動(dòng)都為最小。為了適應(yīng)復(fù)雜設(shè)計(jì)的需要,Xilinx的FPGA中集成的專(zhuān)用時(shí)鐘資源與數(shù)字延遲鎖相環(huán)(DLL)的數(shù)目不斷增加,最新的Virtex II器件最多可以提供16個(gè)全局時(shí)鐘輸入端口和8

2019-10-22 06:01:34

`1.我在UCF里進(jìn)行了時(shí)鐘約束,請(qǐng)問(wèn)這個(gè)時(shí)鐘是不是由FPGA晶振產(chǎn)生的?NET "clk" TNM_NET = clk;TIMESPEC TS_clk

2017-08-03 09:54:26

我在vivado 2016.3中看到了以下地方的錯(cuò)誤錯(cuò)誤:[放置30-675]支持全局時(shí)鐘的IO引腳和BUFG對(duì)的次優(yōu)放置。如果此子設(shè)計(jì)可接受此子優(yōu)化條件,則可以使用.xdc文件中

2018-11-09 11:37:33

嗨,大家好,我正在使用Vivado 2014.對(duì)于設(shè)計(jì),是使用BUFG或IBUF / OBUF原語(yǔ)到端口引腳還是工具將在分配PIN時(shí)自動(dòng)獲取緩沖區(qū)?我沒(méi)有為時(shí)鐘引腳A2YCLK0分配BUFG。在我

2019-04-03 13:28:08

在FPGA 上設(shè)計(jì)一個(gè)高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項(xiàng)巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡(luò)都是運(yùn)行在一個(gè)單一時(shí)鐘下。隨著FPGA 技術(shù)的發(fā)展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

你好假設(shè)有一個(gè)數(shù)據(jù)總線(寬度為16位)和位于Virtex 5中心列的存儲(chǔ)區(qū)的相應(yīng)時(shí)鐘,我想在輸入焊盤(pán)處捕獲數(shù)據(jù)。為此,我認(rèn)為將BUFIO與bank的CC_P引腳上的時(shí)鐘結(jié)合使用可能是一個(gè)想法,以便

2020-06-17 12:57:55

需要20個(gè)。任何人都可以建議如何在不使用BUFG的情況下從全局時(shí)鐘引腳轉(zhuǎn)換到FPGA邏輯?我已經(jīng)咨詢過(guò)UG382第30頁(yè)的一些想法,但仍然無(wú)法弄清楚如何避免BUFG。謝謝拉克蘭。Lachlan

2019-07-01 10:20:35

使用7系列FPGA,ISERDES的新時(shí)鐘方法出現(xiàn)了,至少我以前從未見(jiàn)過(guò)它:由BUFG驅(qū)動(dòng)的CLK,由不同的BUFG驅(qū)動(dòng)的CLKDIV您可以查看這兩個(gè)文檔以獲得更好的解釋?zhuān)?b class="flag-6" style="color: red">7系列:http

2020-07-16 09:42:53

]));那警告消失了,但我在BUFG之前需要變頻器。所以我猜測(cè)BUFG輸入端的逆變器是出于某種原因推過(guò)BUFG時(shí)鐘緩沖器(也許我錯(cuò)了,還有另一個(gè)問(wèn)題)。試(* keep =“true”*)wire

2018-10-19 14:38:55

我是學(xué)習(xí)Verilog的6小時(shí),我有Diglent的Spartan 3E板,我遇到了一個(gè)非常新的問(wèn)題。我試圖將電路板上的50MHz時(shí)鐘降低到3Hz(任何慢速值)并使LED閃爍。我可以這樣做的一種

2019-06-11 08:41:01

DS-180: 7 Series FPGAs Data Sheet: Overview 3.電氣接口標(biāo)準(zhǔn)、封裝方式、速度等級(jí)和溫度等級(jí) 電氣接口標(biāo)準(zhǔn): 數(shù)字電路的電氣接口標(biāo)準(zhǔn)非常多。在復(fù)雜

2020-12-23 17:21:03

我的問(wèn)題來(lái)自bank 1的差分時(shí)鐘(PinIO_L40P_GCLK11_1 / IO_L40N_GCLK10_1)通過(guò)IODELAY和BUFIO路由到PLL。問(wèn)題:xilinx ISE不允許我將輸出

2019-06-10 13:47:53

你好,我將使用Aptina圖像傳感器,其中27Mhz x 12 = 324 Mhz,SDR 324Mbit / s。 FPGA- Xilinx Spartan 6所以我需要反序列化因子12:1,數(shù)據(jù)

2020-03-09 09:26:29

本帖最后由 scratdqy 于 2015-8-17 11:06 編輯

向各位大神求助GTX問(wèn)題!!用xilinx的Vivado中的7 Series FPGAs Transceivers

2015-07-28 18:54:12

大家好,在我的設(shè)計(jì)中,我使用PLL為所有mylogic生成全局時(shí)鐘。我想使用相同的輸出時(shí)鐘來(lái)使用不同的BUFIO2為OSERDES原語(yǔ)生成時(shí)鐘。在地圖期間我收到此錯(cuò)誤:錯(cuò)誤:位置:1136 - 此

2019-08-02 07:05:22

報(bào)告顯示時(shí)鐘延遲遠(yuǎn)大于數(shù)據(jù)延遲,導(dǎo)致保持時(shí)間違規(guī)。我嘗試將BUFG / BUFIO或IBUF直接連接到iddr原語(yǔ),沒(méi)有一個(gè)可以滿足時(shí)序要求。可以幫我設(shè)計(jì)一個(gè)這樣的雙向具有tsu = th

2020-08-28 06:14:43

7系列有多少BUFG?我從報(bào)告中讀到有128個(gè),這是正確答案嗎?

2020-08-25 15:49:16

嗨!我想知道BUFIO2 + BUFG和ODDR2的解決方案是否用于時(shí)鐘路由在時(shí)鐘源上可以避免使用Spartan 6(使用直接賦值)已經(jīng)從外部緩沖了。我的意思是,而不是 bufio

2018-10-23 10:24:05

FPGAXCKU085FLVA1517-2-e的哪個(gè)引腳連接到系統(tǒng)時(shí)鐘?我們正在使用這個(gè)FPGA -https://www.xilinx.com/products/boards-and-kits

2019-10-11 06:34:46

嗨,我是

FPGA的新手(也是

Xilinx系列

FPGA的新手),所以我想知道

Xilinx Spartan-II(XC2S100)

FPGA板中是否有內(nèi)置/預(yù)編程的Verilog模塊或變量。這是因?yàn)槲艺?/div>

2019-06-04 12:36:34

我在這里感到非常困惑。 Xilinx的非凡文檔在這里失敗了。Spartan-6 FPGA時(shí)鐘資源指南UG382告訴我們四個(gè)器件有四個(gè)存儲(chǔ)區(qū),有八個(gè)BUFIO2時(shí)鐘區(qū):TL,TR,BL,BR,LT

2019-06-28 10:07:04

,即兩個(gè)BUFG站點(diǎn),其Y-index相差32的倍數(shù)不能用于同一時(shí)間RESETB_ibuf(BUFG.O)由clockplacer臨時(shí)放置在BUFGCTRL_X0Y70上(在SLR 2中)我正在使用xc7v2000tf1925-2系列fpga。它應(yīng)該是一個(gè)多SLR設(shè)備。那么如何手動(dòng)鎖定IBUFG,BUFG的位置謝謝,

2020-06-17 11:33:53

我有以下情況。 125MHz的輸入信號(hào)進(jìn)入FPGA并通過(guò)緩沖器“IBUFG”然后通過(guò)緩沖器“BUFIO2”。然后,我使用此信號(hào)采樣與此輸入時(shí)鐘同步的I / O觸發(fā)器輸入信號(hào)。但我還需要將時(shí)鐘用于其他

2019-06-24 12:23:40

,RXUSRCLK20和RXUSRCLK21生成時(shí)鐘信號(hào)。對(duì)于兩個(gè)TX,我使用了UG386(v2.2)中給出的設(shè)計(jì),第75頁(yè)的圖3-7,BUFIO2,DCM_SP和一些BUFG原語(yǔ)。要將四個(gè)GTPCLKOUT

2019-07-10 10:14:35

GX-FPGA-XC7A100T-SOM是北京革新創(chuàng)展科技有限公司開(kāi)發(fā)的一款基于XILINX ARTIX-7系列FGG484封裝類(lèi)型的芯片而開(kāi)發(fā)的高性能核心板。核心板具有高速度、高帶寬、高容量等特點(diǎn)

2022-03-09 11:33:24

Xilinx?7系列FPGA由四個(gè)FPGA系列組成,可滿足各種系統(tǒng)要求,從低成本、小尺寸、成本敏感的高容量應(yīng)用到超高端連接帶寬、邏輯容量和信號(hào)處理能力,以滿足最苛刻的高性能應(yīng)用

2022-08-30 17:04:09

Xilinx?7系列FPGA包括四個(gè)FPGA系列,可滿足整個(gè)系統(tǒng)要求,包括低成本,小尺寸,成本敏感的大批量應(yīng)用程序,可滿足最苛刻的超高端連接帶寬,邏輯容量和信號(hào)處理能力高性能的應(yīng)用程序。7系列

2022-11-10 15:11:11

一種FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探

2009-08-08 09:07:22 25

25 本文闡述了用于FPGA的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探討了FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案。

2010-08-06 16:08:45 12

12 本書(shū)系統(tǒng)地論述了Xilinx FPGA開(kāi)發(fā)方法、開(kāi)發(fā)工具、實(shí)際案例及開(kāi)發(fā)技巧,內(nèi)容涵蓋Xilinx器件概述、Verilog HDL開(kāi)發(fā)基礎(chǔ)與進(jìn)階、Xilinx FPGA電路原理與系統(tǒng)設(shè)計(jì)

2012-07-31 16:20:42 11268

11268

DLL在_FPGA時(shí)鐘設(shè)計(jì)中的應(yīng)用,主要說(shuō)明DLL的原理,在Xilinx FPGA中是怎么實(shí)現(xiàn)的。

2015-10-28 14:25:42 1

1 談到數(shù)字邏輯,談到FPGA設(shè)計(jì),每位工程師都離不開(kāi)時(shí)鐘。這里我們簡(jiǎn)單介紹一下xilinx 7 系列中的時(shí)鐘資源。時(shí)鐘設(shè)計(jì)的好壞,直接影響到布局布線時(shí)間、timing的收斂情況,FPGA的時(shí)鐘

2017-02-08 05:33:31 561

561

1. Xilinx 時(shí)鐘資源 xilinx 時(shí)鐘資源分為兩種:全局時(shí)鐘和第二全局時(shí)鐘。 1. 全局時(shí)鐘資源 Xilinx 全局時(shí)鐘采用全銅工藝實(shí)現(xiàn),并設(shè)計(jì)了專(zhuān)用時(shí)鐘緩沖與驅(qū)動(dòng)結(jié)構(gòu),可以到達(dá)芯片內(nèi)部

2017-02-09 08:43:41 1315

1315 普通IO可以通過(guò)BUFG再連到PLL的時(shí)鐘輸入上,但要修改PLL的設(shè)置 input clk的選項(xiàng)中要選擇"No Buffer";

2017-02-09 12:54:11 6825

6825

Spartan-6的時(shí)鐘布線網(wǎng)絡(luò)包括由BUFGMUX驅(qū)動(dòng)的全局時(shí)鐘網(wǎng)絡(luò)和由I/O時(shí)鐘緩沖器(BUFIO2)、PLL時(shí)鐘緩沖器(BUFPLL)驅(qū)動(dòng)的I/O區(qū)域時(shí)鐘網(wǎng)絡(luò)。

2017-02-11 08:42:11 658

658

樹(shù)結(jié)構(gòu) 針對(duì)不同類(lèi)型的器件,Xilinx公司提供的全局時(shí)鐘網(wǎng)絡(luò)在數(shù)量、性能等方面略有區(qū)別,下面以Virtex-4系列芯片為例,簡(jiǎn)單介紹FPGA全局時(shí)鐘網(wǎng)絡(luò)結(jié)構(gòu)。

2017-11-22 07:09:36 8891

8891

高扇出 net 是時(shí)序收斂的一個(gè)常見(jiàn)瓶頸。所以,除了傳統(tǒng)的降低扇出的方法之外,還可以將該 net 引入 BUFG,但前提是有可用的 BUFG。眾所周知,BUFG 是全局時(shí)鐘資源,在配置 MMCM 或 PLL 時(shí)會(huì)用到。

2018-04-10 18:06:00 4327

4327

FPGA本身是有專(zhuān)門(mén)的時(shí)鐘cell的,以xilinx FPGA為例,就是primitive庫(kù)中的BUFG。

2018-12-22 15:33:59 1588

1588 時(shí)鐘網(wǎng)絡(luò)反映了時(shí)鐘從時(shí)鐘引腳進(jìn)入FPGA后在FPGA內(nèi)部的傳播路徑。 報(bào)告時(shí)鐘網(wǎng)絡(luò)命令可以從以下位置運(yùn)行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2550

2550 時(shí)鐘篇 選用全局時(shí)鐘緩沖區(qū)(BUFG)作為時(shí)鐘輸入信號(hào),BUFG是最穩(wěn)定的時(shí)鐘輸入源,可以避免誤差。 只用一個(gè)時(shí)鐘沿來(lái)寄存數(shù)據(jù),使用時(shí)鐘的兩個(gè)沿是不可靠的,如果時(shí)鐘沿“漂移”,就會(huì)導(dǎo)致時(shí)序錯(cuò)誤

2020-12-11 10:26:44 1482

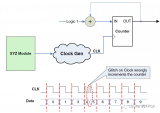

1482 組合邏輯生成的時(shí)鐘,在FPGA設(shè)計(jì)中應(yīng)該避免,尤其是該時(shí)鐘扇出很大或者時(shí)鐘頻率較高,即便是該時(shí)鐘通過(guò)BUFG進(jìn)入全局時(shí)鐘網(wǎng)絡(luò)。

2020-10-10 10:28:32 3639

3639

全局時(shí)鐘資源是一種專(zhuān)用互連網(wǎng)絡(luò),它可以降低時(shí)鐘歪斜、占空比失真和功耗,提高抖動(dòng)容限。Xilinx的全局時(shí)鐘資源設(shè)計(jì)了專(zhuān)用時(shí)鐘緩沖與驅(qū)動(dòng)結(jié)構(gòu),從而使全局時(shí)鐘到達(dá)CLB、IOB和BRAM的延時(shí)最小。

2020-12-29 16:59:35 8

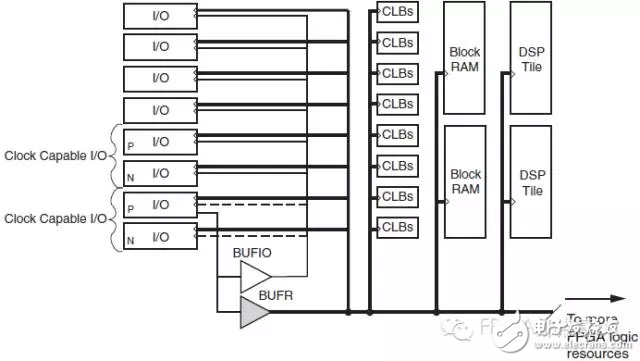

8 源同步接口設(shè)計(jì)特別有用。7系列器件中的I/O Bank與時(shí)鐘區(qū)域的大小相同。為了理解區(qū)域時(shí)鐘是如何工作的,理解區(qū)域時(shí)鐘信號(hào)的信號(hào)路徑是很重要的。7系列設(shè)備中的區(qū)域時(shí)鐘資源和網(wǎng)絡(luò)由以下路徑和組件組成: 時(shí)鐘輸入I/O I/O時(shí)鐘緩沖器:BUFIO 區(qū)域時(shí)

2021-03-22 09:47:30 4631

4631

引言:從本文開(kāi)始,我們陸續(xù)介紹Xilinx 7系列FPGA的時(shí)鐘資源架構(gòu),熟練掌握時(shí)鐘資源對(duì)于FPGA硬件設(shè)計(jì)工程師及軟件設(shè)計(jì)工程師都非常重要。本章概述7系列FPGA時(shí)鐘,比較了7系列FPGA時(shí)鐘

2021-03-22 10:25:27 4326

4326 晶振是數(shù)字電路設(shè)計(jì)中非常重要的器件,時(shí)鐘的相位噪聲、頻率穩(wěn)定性等特性對(duì)產(chǎn)品性能影響很大。本文基于可編程晶振SI570,就Xilinx FPGA收發(fā)器輸入?yún)⒖?b class="flag-6" style="color: red">時(shí)鐘的硬件設(shè)計(jì)及FPGA軟件設(shè)計(jì)給出設(shè)計(jì)案例,供大家參考。

2021-04-07 12:00:44 3914

3914

?xilinx 的 FPGA 時(shí)鐘結(jié)構(gòu),7 系列 FPGA 的時(shí)鐘結(jié)構(gòu)和前面幾個(gè)系列的時(shí)鐘結(jié)構(gòu)有了很大的區(qū)別,7系列的時(shí)鐘結(jié)構(gòu)如下圖所示。

2022-07-03 17:13:48 2592

2592 BUFIO是用來(lái)驅(qū)動(dòng)I/O列內(nèi)的專(zhuān)用時(shí)鐘網(wǎng)絡(luò),這個(gè)專(zhuān)用的時(shí)鐘網(wǎng)絡(luò)獨(dú)立于全局時(shí)鐘資源,適合采集源同步數(shù)據(jù)。BUFIO只能由位于同一時(shí)鐘區(qū)域的Clock-Capable I/O驅(qū)動(dòng)。一個(gè)時(shí)鐘區(qū)域

2023-05-11 16:16:36 1530

1530

Xilinx是一家專(zhuān)業(yè)的可編程邏輯器件(PLD)廠商,其產(chǎn)品包括FPGA、CPLD、SOC等。Xilinx的FPGA產(chǎn)品線有多個(gè)系列,其中7系列和Ultrascale系列是比較常見(jiàn)的兩種。那么,這兩個(gè)系列有什么區(qū)別呢?

2023-09-15 14:44:54 1776

1776

在Vivado中禁止自動(dòng)生成BUFG(Buffered Clock Gate)可以通過(guò)以下步驟實(shí)現(xiàn)。 首先,讓我們簡(jiǎn)要了解一下什么是BUFG。BUFG是一個(gè)時(shí)鐘緩沖器,用于緩沖輸入時(shí)鐘信號(hào),使其更穩(wěn)

2024-01-05 14:31:06 454

454 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論