導(dǎo)讀:

7系列FPGA包含最多24個(gè)CMT塊,CMT具體的分布和與其他時(shí)鐘資源的關(guān)系請(qǐng)參考本合集(FPGA應(yīng)用開發(fā))的上一篇文章。本文主要介紹CMT內(nèi)部MMCM和PLL的區(qū)別以及在實(shí)際開發(fā)中怎么使用CMT,怎么實(shí)現(xiàn)跨時(shí)鐘區(qū)域,第一次讀者最好先閱讀上一篇文章——解剖時(shí)鐘結(jié)構(gòu)篇。

MMCM和PLL的區(qū)別

在xilinx 7系列FPGA中,時(shí)鐘管理塊(CMT)包括混合模式時(shí)鐘管理器(MMCM)和鎖相環(huán)(PLL)。MMCM和PLL可用于廣泛范圍頻率的頻率合成器,用作外部或內(nèi)部時(shí)鐘的抖動(dòng)濾波器,并用于去斜時(shí)鐘。

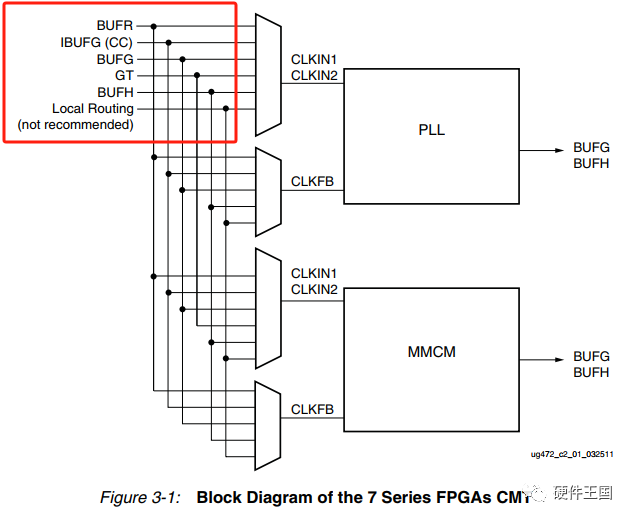

下圖顯示了各種時(shí)鐘輸入源與MMCM/PLL之間連接的高層次視圖。在7系列FPGA中,時(shí)鐘輸入允許多個(gè)資源(如紅框所示)提供參考時(shí)鐘給MMCM/PLL。

PLL與MMCM的區(qū)別:

在CMT中,PLL是MMCM功能的一個(gè)子集。PLL主要用于頻率合成,但不支持MMCM的一些高級(jí)功能,如直接連接到HPC(高性能時(shí)鐘)或BUFIO(緩沖器輸入輸出)等。MMCM是7系列FPGA中用于時(shí)鐘管理的核心。簡(jiǎn)單來說PLL適用于較簡(jiǎn)單的時(shí)鐘管理需求,而MMCM提供了更多高級(jí)功能,適用于更復(fù)雜的時(shí)鐘管理場(chǎng)景。其中MMCM支持的附加功能主要包括:

- 使用CLKOUT[0:3]直接連接到HPC或BUFR或BUFIO。

- 反相時(shí)鐘輸出(CLKOUT[0:3]B),即支持差分輸出。

- CLKOUT6(相比PLL多一路輸出)。

- CLKOUT4_CASCADE(級(jí)聯(lián)輸出,允許將一個(gè) MMCM 的輸出連接到另一個(gè) MMCM 的輸入)。

- CLKOUT0_DIVIDE_F的分?jǐn)?shù)分頻(用于進(jìn)行時(shí)鐘頻率合成時(shí)的分?jǐn)?shù)分頻,非整數(shù)倍時(shí)鐘頻率的設(shè)計(jì)有用)

- CLKFBOUT_MULT_F的分?jǐn)?shù)倍頻(用于進(jìn)行時(shí)鐘頻率合成時(shí)的倍頻設(shè)置)

- 微調(diào)相移

- 動(dòng)態(tài)相移

PLL和MMCM內(nèi)部結(jié)構(gòu)就不再這里詳述了,大家知道怎么用就足夠了,感興趣的讀者可以參考xilinx原文檔。

Clock IP和原語(yǔ)

怎么使用CMT?工程中可以選擇IP即預(yù)設(shè)計(jì)的時(shí)鐘管理模塊,也可以選擇原語(yǔ)硬件描述語(yǔ)言(如VHDL或Verilog)中的代碼自定義時(shí)鐘管理。

選用IP使用簡(jiǎn)單,有圖形用戶界面(GUI),可以通過可視化的方式配置參數(shù),如下圖所示。

選用原語(yǔ),自定義代碼可以更好地控制硬件資源的利用,減小資源占用。對(duì)于經(jīng)驗(yàn)較豐富的開發(fā)者,使用原語(yǔ)可能更為靈活;而對(duì)于初學(xué)者,使用IP更容易上手。

Clock IP:可選擇MMCM還是PLL

MMCM和PLL 原語(yǔ)

注:

MMCME2_BASE原語(yǔ)提供了對(duì)獨(dú)立MMCM的最常用功能的訪問。時(shí)鐘去斜、頻率合成、粗略相移和占空比編程都可以與MMCME2_BASE一起使用。MMCME2_ADV原語(yǔ)提供對(duì)所有MMCME2_BASE功能的訪問,以及用于時(shí)鐘切換、訪問動(dòng)態(tài)重配置端口(DRP)以及動(dòng)態(tài)精細(xì)相移的額外端口。PLL類似,不再細(xì)述。

實(shí)際用例

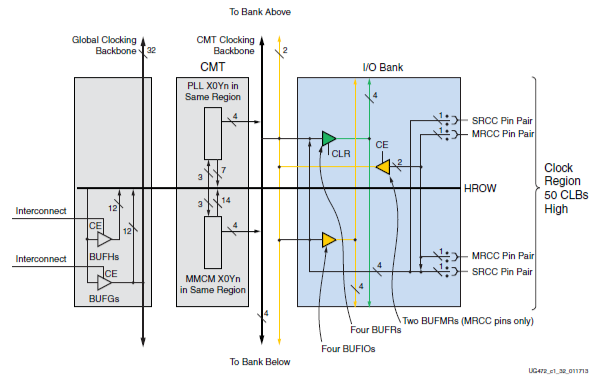

xilinx原文檔有描述,在不使用其他原語(yǔ)的情況下,進(jìn)入器件的時(shí)鐘信號(hào)(通過CCIO引腳)只能驅(qū)動(dòng)同一時(shí)鐘區(qū)域內(nèi)的BUFR或BUFIO。如果要驅(qū)動(dòng)其他時(shí)鐘區(qū)域的邏輯則必須使用BUFMR原語(yǔ),BUFMR原語(yǔ)是一種多區(qū)域時(shí)鐘緩沖器,允許輸入訪問進(jìn)入器件的時(shí)鐘信號(hào)所在時(shí)鐘區(qū)域上方和下方的BUFR和BUFIO。BUFMR可以跨越多個(gè)時(shí)鐘區(qū)域。每個(gè)時(shí)鐘區(qū)域中有兩個(gè)BUFMR。

然而,在某些情況下,我們可以通過經(jīng)過MMCM和BUFG等元素來實(shí)現(xiàn)跨時(shí)鐘區(qū)域的時(shí)鐘分配。BUFMR主要用于驅(qū)動(dòng)多個(gè)時(shí)鐘區(qū)域的一種特定情況,這是一種確保最小時(shí)鐘偏移和時(shí)鐘抖動(dòng)的方法。因?yàn)樗鼘榭鐣r(shí)鐘區(qū)域提供時(shí)鐘信號(hào)設(shè)計(jì)。

case1:使用BUFMR跨時(shí)鐘區(qū)域

外部時(shí)鐘從MRCC引腳(注:通過BUFMR跨多個(gè)時(shí)鐘區(qū)域時(shí),只能從MRCC引腳,SRCC引腳為單時(shí)鐘區(qū)域,不過也可以使用GT時(shí)鐘)送至BUFMR原語(yǔ),然后BUFMR被多個(gè)BUFR或BUFIO驅(qū)動(dòng)的邏輯分組為(最多三個(gè))子集,每個(gè)子集都有一個(gè)獨(dú)立的BUFR或BUFIO。使用Vivado設(shè)計(jì)工具對(duì)設(shè)計(jì)進(jìn)行布局和約束,以便將邏輯分配給各個(gè)BUFR和BUFIO。

case2:使用BUFG和MMCM跨時(shí)鐘區(qū)域

外部時(shí)鐘從CCIO引腳(MRCC或SRCC)送至BUFG(單端時(shí)鐘)或IBUFGDS(差分時(shí)鐘),經(jīng)過MMCM合成消抖后再連至BUFG,此時(shí)BUFG輸出時(shí)鐘則是全局時(shí)鐘,實(shí)現(xiàn)了跨時(shí)鐘區(qū)域的時(shí)鐘分配。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21947瀏覽量

613626 -

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

592瀏覽量

88428 -

Xilinx

+關(guān)注

關(guān)注

73文章

2181瀏覽量

124247 -

pll

+關(guān)注

關(guān)注

6文章

880瀏覽量

136010 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1875瀏覽量

132799

發(fā)布評(píng)論請(qǐng)先 登錄

XILINX FPGA IP之MMCM PLL DRP時(shí)鐘動(dòng)態(tài)重配詳解

Xilinx 7系列FPGA的時(shí)鐘結(jié)構(gòu)解析

請(qǐng)問如何設(shè)置動(dòng)態(tài)和實(shí)時(shí)改變Artix FPGA中MMCM時(shí)鐘的相移?

在7系列FPGA中,MMCM和PLL之間是否有專用的CMT路由?

Xilinx 7系列FPGA管腳是如何定義的?

xilinx公司的7系列FPGA應(yīng)用指南

Xilinx 7系列FPGA可配置邏輯塊的用戶指南

Xilinx 7系列FPGA時(shí)鐘資源

Xilinx7系列FPGA選擇資源用戶指南

Xilinx 7 系列FPGA中的Serdes總結(jié)

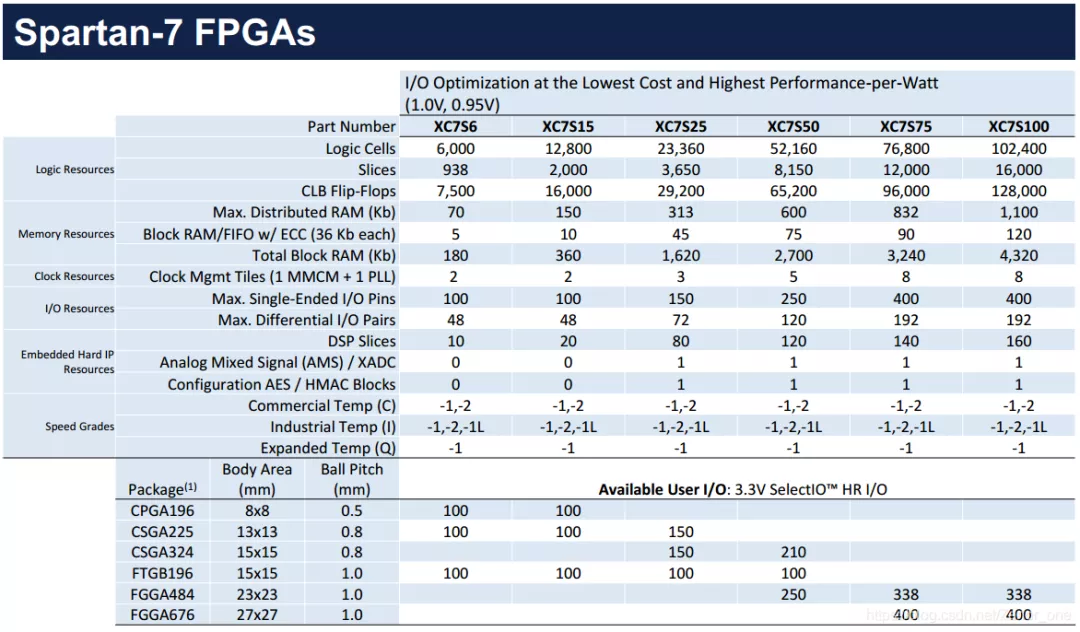

Xilinx 7系列FPGA簡(jiǎn)介--選型參考

Xilinx 7系列與Ultrascale系列FPGA的區(qū)別

簡(jiǎn)述Xilinx 7系列FPGA芯片相關(guān)知識(shí)

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

Xilinx 7系列FPGA中MMCM和PLL的區(qū)別

Xilinx 7系列FPGA中MMCM和PLL的區(qū)別

評(píng)論