賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設(shè)計人員在他們的FPGA設(shè)計中或多或少都會用到。不過對FPGA設(shè)計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 19707

19707

,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。賽靈思現(xiàn)有的FPGA中沒有一款同時包含這四種資源(見表1)。 這四大類中的每一種都針對特定的應(yīng)用。例如,數(shù)字時鐘管理器(DCM)適用于實(shí)現(xiàn)延遲鎖相環(huán)(DLL)、數(shù)字頻率綜合器、數(shù)字移相器或數(shù)字

2021-02-13 17:02:00 2014

2014

有些FPGA學(xué)習(xí)者,看Xilinx的Datasheet會注意到Xilinx的FPGA沒有PLL,其實(shí)DCM就是時鐘管理單元。

2022-07-08 09:48:07 1138

1138 7系列FPGA時鐘資源通過專用的全局和區(qū)域I/O和時鐘資源管理符合復(fù)雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

1276 “全局時鐘和第二全局時鐘資源”是FPGA同步設(shè)計的一個重要概念。合理利用該資源可以改善設(shè)計的綜合和實(shí)現(xiàn)效果;如果使用不當(dāng),不但會影響設(shè)計的工作頻率和穩(wěn)定性等,甚至?xí)?dǎo)致設(shè)計的綜合、實(shí)現(xiàn)過程出錯

2023-07-24 11:07:04 655

655

通過上一篇文章“時鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區(qū)域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

我的設(shè)計有32MHz輸入時鐘(DCM最小輸入)。由此我需要12.5MHz時鐘和6.25MHz時鐘。我顯然必須使用兩個獨(dú)立的DCM并行使用不同的除數(shù)來獲得輸出。這兩個輸出會同步嗎?如果沒有,有沒有辦法實(shí)現(xiàn)這一目標(biāo)?

2020-06-02 15:28:02

我希望從我的24MHz系統(tǒng)時鐘產(chǎn)生2MHz時鐘(除以12)。在Virtex-2庫中似乎沒有“Divide by 12”部分。此外,DCM(數(shù)字時鐘管理器)向?qū)⒉辉试S我從DCM創(chuàng)建除以12的輸出

2020-05-28 06:57:53

我在DCM時鐘頻率方面遇到了一些麻煩。我創(chuàng)建了兩個具有相同時鐘輸入的相同DCM,我使用這些DCM的clk0輸出作為兩個相同模塊的輸入。但是,當(dāng)我更改clkfx_multiply或

2019-01-25 09:04:04

求助大神們,由晶振產(chǎn)生的30Mhz時鐘使用DCM輸出108Mhz時鐘,用示波器檢測輸出波形,周期沒問題,但是上升和下降邊緣都有很大的過沖,幅值占到脈沖本身的50%,請問下有什么辦法能消除呢?

2013-05-25 22:10:51

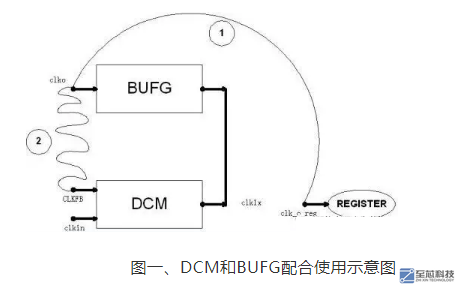

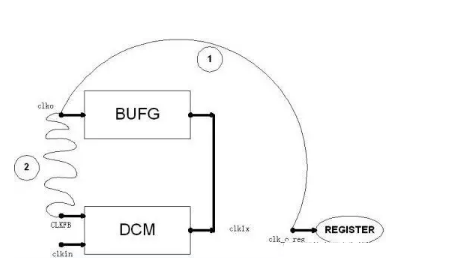

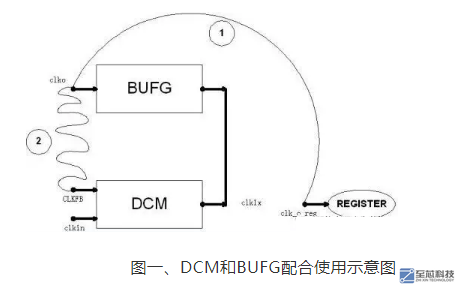

管理單元(DCM)的日益完善,目前BUFGDLL的應(yīng)用已經(jīng)逐漸被DCM所取代。 8. DCM即數(shù)字時鐘管理單元,主要完成時鐘的同步、移相、分頻、倍頻和去抖動等。DCM與全局時鐘有著密不可分的聯(lián)系

2015-03-09 19:48:54

DCM就是數(shù)字時鐘管理單元( Digital Clock Manager)。DCM 當(dāng)中包含一個 DLL(延遲鎖定電路 Delay-Locked Loop),可以提供對時鐘信號的二倍頻和分頻功能

2018-08-31 09:08:22

嗨, 我在使用DCM時遇到了問題。我的要求實(shí)際上是將clk信號的頻率從50MHz降低到20MHz。在10個時鐘脈沖之后,dcm的輸出會顯示出來。我使用的是ISE版本12.1。FPGA系列

2019-01-30 08:59:50

您好,我正在分析使用Xilinx ISE 9.2 Service Pack 4為Spartan 3 FPGAT合成的現(xiàn)有設(shè)計的時序約束。該設(shè)計具有20 MHz的單時鐘輸入(sys_clk),用于

2020-05-01 15:08:50

FPGA的DCM模塊,40MHz時鐘輸入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。對40MHz時鐘添加了約束,系統(tǒng)不是會自動對三個輸出時鐘進(jìn)行約束

2017-05-25 15:06:47

說說專用時鐘引腳,它的出現(xiàn)具體原因可以說是FPGA自身的實(shí)現(xiàn)結(jié)構(gòu)引起的,FPGA實(shí)現(xiàn)時,具體的時鐘大概有外部供給FPGA的工作時鐘,由DCM或者PLL產(chǎn)生的時鐘,和FPGA輸入輸出數(shù)據(jù)的隨路時鐘;再說

2019-07-09 08:00:00

有內(nèi)部的時鐘管理單元可用(通常是有)?它的輸入頻率范圍(需要查看器件手冊進(jìn)行確認(rèn))?●盡可能選擇專用的時鐘輸入引腳。(特權(quán)同學(xué),版權(quán)所有)●時鐘走線盡可能短,有條件最好做包地處理,確保外部輸入時鐘信號干凈、穩(wěn)定。(特權(quán)同學(xué),版權(quán)所有) Xilinx FPGA入門連載

2019-04-12 01:15:50

嗨,我是FPGA的新手。我想知道我是否可以有一個設(shè)計,我的FPGA的外部時鐘周期性地打開和關(guān)閉。我知道Xilinx FPGA使用數(shù)字時鐘管理器(DCM)和相位鎖(或使用觸發(fā)器延遲鎖定)。因此,我

2019-01-10 10:59:04

大家好,我的FPGA設(shè)計運(yùn)行在可編程外部時鐘上。外部時鐘輸入PLL_BASE / DCM_SP,產(chǎn)生主時鐘。該設(shè)計必須以兩種不同的主時鐘速率運(yùn)行 -79.8 MHz或66.5 MHz。我正在將外部

2019-07-16 07:37:45

您好,我的名字是Bontor。我正在嘗試在Digilent Atlys板上實(shí)現(xiàn)我的HDL設(shè)計(fft模塊),該板使用Spartan 6作為FPGA內(nèi)核。你的電路板提供100 MHz時鐘,而我

2018-10-17 14:28:54

00. 目錄文章目錄00. 目錄01. 時鐘概述02. HSE時鐘03. HSI時鐘04. PLL配置05. LSE時鐘06. LSI時鐘07. 系統(tǒng)時鐘 (SYSCLK)選擇08. 附錄09.

2021-08-11 08:31:23

時鐘信號從普通IO管腳輸入怎么進(jìn)行處理,時鐘從普通IO管腳進(jìn)入FPGA后能進(jìn)入全局時鐘網(wǎng)絡(luò)嗎?因為只有全局時鐘管腳后面連接有IBUFG/IBUFGDS緩沖單元,如果差分時鐘信號從普通IO管腳進(jìn)入后

2012-10-11 09:56:33

的所有可配置單元(CLB)、I/O 單元(IOB)和選擇性塊 RAM(Block Select RAM)的時延和抖動都為最小。為了適應(yīng)復(fù)雜設(shè)計的需要,Xilinx 的 FPGA 中集成的專用時鐘資源

2014-11-24 17:58:10

輸入。 DCM僅用于相移(用于處理源同步輸入數(shù)據(jù))。這8個DCM時鐘輸入來自ADC,它采用內(nèi)部重新驅(qū)動的輸入時鐘,以便將數(shù)據(jù)時鐘提供給FPGA。FPGA中的PLL提供ADC輸入時鐘(它們很常見)。八個

2019-07-26 13:04:49

為148.5 MHz max Clk)我使用單個DCM從兩個外部時鐘(74.25 MHz和74.25 / 1.001 MHz)產(chǎn)生所有必需的Clk速率。對于一個新項目,我使用的是Spartan 6,并且想考慮

2019-07-23 14:02:15

在Vivado 2016.1和Kintex-7 FPGA中,我可以使用名為“Clocking Wizard v5.3”的IP來配置為我的項目輸出系統(tǒng)時鐘的MMCM。自定義此IP后,將自動為IP生成

2019-08-02 09:54:40

本帖最后由 lpc2292 于 2013-2-27 20:24 編輯

“部分 I: 用 Spartan-3 系列 FPGA 進(jìn)行設(shè)計”第 1 章 “概述”第 2 章 “使用全局時鐘資源”第 3

2013-02-27 20:20:10

嗨,我試圖從50Mhz外部時鐘信號到FPGA獲得1.25Mhz時鐘信號,以運(yùn)行一個自由運(yùn)行的二進(jìn)制計數(shù)器。為此,我可以使用2個DCM并使用第一個來將clk頻率除以16,將下一個頻率除以5嗎?還是有

2019-02-14 12:04:24

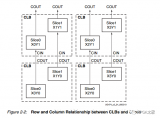

或2 個)相同的Slice 和附加邏輯構(gòu)成,每個CLB 模塊不僅可以用于實(shí)現(xiàn)組合邏輯、時序邏輯,還可以配置為分布式RAM 和分布式ROM。3. 數(shù)字時鐘管理模塊(DCM)業(yè)內(nèi)大多數(shù) FPGA 均提供

2012-03-08 11:03:49

大家好。BUFG資源和DCM / PLL模塊在許多FPGA線路上使用專用時鐘布線資源。對于SerDes應(yīng)用,我們使用BUFIO2來獲得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

IPcore LPDDR控制器帶有自己的時鐘緩沖器。其余的FPGA邏輯也需要DCM。當(dāng)我將相同的輸入時鐘連接到LPDDR控制器而另一個DCM時,我得到了錯誤Xst:2035 - 港口有非法連接。此

2019-08-06 08:02:26

嗨,我有兩個關(guān)于FPGA的問題......1)奇數(shù)頻率 - 使用DCM,它很容易產(chǎn)生100MHz,25MHz等頻率。但是如何生成11.6MHz,13.2MHz等奇數(shù)時鐘頻率?我可能需要什么原語?2

2019-02-25 11:13:27

你好!我是FPGA設(shè)計的新手。我想在我的項目中使用DCM,但是,在我執(zhí)行Xilinx時鐘向?qū)е螅瑳]有生成響應(yīng)的vhdl文件。我想知道我該怎么生成這個vhdl文件。我還有其他步驟嗎?謝謝你的考慮

2019-01-15 10:22:23

在我們的系統(tǒng)中,我們使用外部時鐘源,頻率為54MHz。我們希望獲得133MHz的時鐘,因此我們在DCM中使用以下方法:(54MHz * 22)/ 9 = 132MHz在用DCM提到上述處理之后,我

2019-01-25 09:03:06

,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。賽靈思現(xiàn)有的FPGA中沒有一款同時包含這四種資源(見表1)。 這四大類中的每一種都針對特定的應(yīng)用。例如,數(shù)字時鐘管理

2020-04-25 07:00:00

FPGA全局時鐘資源一般使用全銅層工藝實(shí)現(xiàn),并設(shè)計了專用時鐘緩沖與驅(qū)動結(jié)構(gòu),從而使全局時鐘到達(dá)芯片內(nèi)部的所有可配置單元(CLB)、I/O單元(IOB)和選擇性塊RAM(Block Select

2019-10-22 06:01:34

我將源時鐘除以2,然后嘗試將其輸入DCM(首先通過緩沖區(qū))。但我得到的錯誤是我無法解釋的:錯誤:NgdBuild:455- 邏輯網(wǎng)絡(luò)'clk25'有多個驅(qū)動程序:塊clk25上的引腳Q,類型為FDC

2018-10-18 14:22:42

我知道我可以使用DCM來創(chuàng)建相對于彼此具有90度相移的4個時鐘。但我想創(chuàng)建4個時鐘,每個時鐘相對于彼此具有60度相移。是否可以使用一個DCM(我想使用只有2個DCMS的144tqg軟件包)?該手冊

2019-05-13 12:26:10

嗨,我正在嘗試從FPGA向另一個設(shè)備輸出一個時鐘信號(10MHz)來驅(qū)動一個50歐姆的端接負(fù)載。我試著用DDR來輸出這個時鐘。我從主振蕩器時鐘輸入(50MHz)到virtex板生成此信號。我使用DCM以5來獲得10Mhz。然后我把它運(yùn)行到DDR。到目前為止,我沒有運(yùn)氣。有人可以給我指點(diǎn)嗎?謝謝。

2020-06-15 08:40:22

>時鐘輸出引腳。如果我進(jìn)行這樣的連接,則占空比變?yōu)榇蠹s56%:時鐘輸入引腳 - > DCM- >輸出引腳。為什么DCM的職責(zé)修正功能不起作用?如何使XC3S200 FPGA以理想

2019-05-09 12:44:41

大家好..我是xilinx的新手。實(shí)際上我需要知道如何使用DCM減少時鐘偏差,我還需要知道如何使用DCM來增加時鐘。謝謝和關(guān)心JITHESH A R

2020-06-09 09:09:29

需要生成一個低速單端時鐘來測試非常慢的serdes通道(長篇故事為什么它如此低和單端)。我試圖在低頻模式下使用V5 DCM接受2.5MHz的輸入時鐘并產(chǎn)生15MHz-17.5MHz。當(dāng)我使用GUI

2020-06-15 16:11:09

我想從DCM創(chuàng)建兩個同步時鐘,19.2MHz和38.4MHz。必須使用CLKFX生成其中一個時鐘(比如說38.4MHz時鐘)。由于DCM沒有CLKFX / 2輸出,我必須使用另一個DCM來產(chǎn)生

2019-05-17 13:03:29

嗨,我想在S6SLX9 FPGA上從4MHz輸入時鐘獲得80MHz時鐘。首先,我嘗試實(shí)例化一個主要工作但導(dǎo)致錯誤的DCM_SP。我假設(shè)這些錯誤是由DCM_SP最小輸入頻率5 MHz引起的,如定時警告

2019-07-22 11:51:05

大家好, 任何人都可以幫我找到“Zynq(7系列FPGA-XC7Z045FFG900)DCM中DCM的最小相位分辨率?如果有人知道,請幫忙!

2020-08-27 16:17:41

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設(shè)計策略的基礎(chǔ)。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設(shè)計人員在他們的FPGA設(shè)計中或多或少都會用到。不過對FPGA設(shè)計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

我有一個內(nèi)部生成的時鐘,我想用它作為DCM的輸入。目標(biāo)是使用CLOCK_STOPPED信號。合成失敗并說:實(shí)例化“DCM”焊盤的端口“I”未連接到chipI / O引腳。有誰知道如何解決這個問題?謝謝

2019-08-09 08:34:45

。問題是,有時由于HV產(chǎn)生的噪聲,我不再能夠讀取寄存器,并且我讀取所有寄存器地址的相同值。即便在這一刻,20MHz時鐘仍能正常工作。我想這個問題是由于48MHz DCM凍結(jié),因為重置fpga一切都恢復(fù)正常

2019-07-19 12:49:34

你好在DCM中有一個RESET輸入引腳。我已將RESET引腳指定為分配RESET = ~LOCKED // DCM鎖定,希望這將使RESET從開始起至少保持三個時鐘周期。當(dāng)我使用這種類型的賦值

2019-06-06 07:23:45

將這個時鐘放在FPGA引腳上,然后使用單個DCM,我可以產(chǎn)生一個40 MHz的時鐘。然后,我將這個時鐘從FPGA發(fā)送到我必須測試的ASIC芯片。問題是輸出clk(clk_40)看起來像一個正弦波,而我

2019-05-22 14:43:40

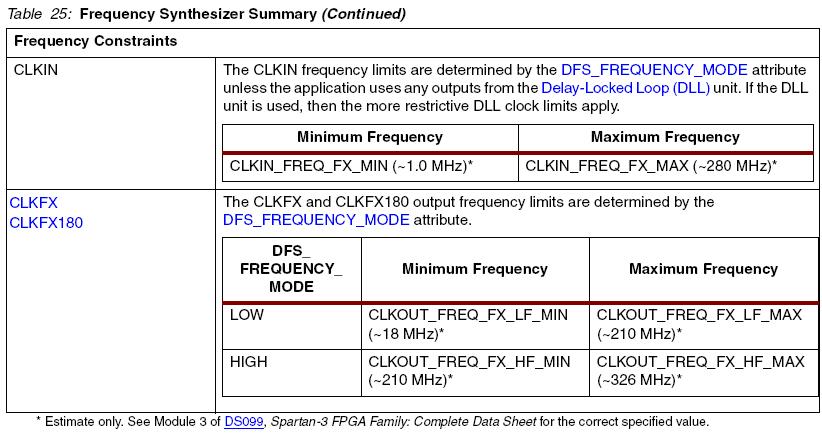

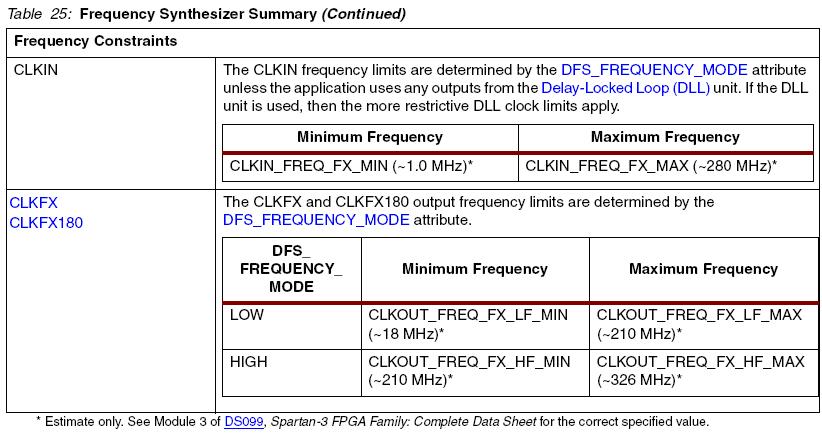

嗨,我正在嘗試使用DCM單元的DFS模式使用50MHz晶振生成300MHz差分時鐘。我使用邏輯內(nèi)核生成了這個單元,并根據(jù)需要初始化了參數(shù)。我只是在這個設(shè)計中使用CLKFX和CLKFX180

2019-05-14 11:21:57

你好,我寫了一個簡單的代碼,由兩個計數(shù)器組成,從15開始倒計時。兩個時鐘都按計劃運(yùn)行。接下來我想在代碼中實(shí)現(xiàn)DCM,以便將時鐘信號相移90度并在32MHz下運(yùn)行它們。我已成功將DCM代碼實(shí)現(xiàn)到現(xiàn)有

2019-02-27 10:24:57

實(shí)現(xiàn)頂層設(shè)計是不可能的,因為我想生成一個時鐘來驅(qū)動FPGA邏輯和使用DCM的OPAD。以下是ERROR消息。錯誤:位置:1206- 此設(shè)計包含一個全局緩沖區(qū)實(shí)例,驅(qū)動網(wǎng)絡(luò),驅(qū)動以下(前30個)非時鐘

2019-07-03 09:33:36

是否有評估板的外部(FPGA外部)時鐘分頻器而不是使用DCM或PLL?問候,半

2020-03-16 09:11:44

如果xilinx V5板子 程序中使用外部輸入時鐘,clk=36.15MHz,現(xiàn)在需要使用36.15*6=216.9MHz的時鐘進(jìn)行運(yùn)算,如何生成該時鐘?求指導(dǎo)。ucf文件中已定義NET "

2014-12-16 16:12:31

上圖是我的系統(tǒng)結(jié)構(gòu),FPGA使用AD產(chǎn)生的120M差分時鐘作為時鐘,通過一個DCM生成120M,240M的時鐘,使用DCM生成的時鐘作為AD采樣時鐘來采樣并行14bit差分?jǐn)?shù)據(jù)。每次修改了FPGA

2016-08-14 16:58:50

電源管理電源管理概述配置電源管理鎖電源管理概述ESP-IDF 中包含的電源管理算法可以根據(jù)應(yīng)用組件的要求調(diào)整 APB 頻率,CPU 頻率,并使芯片進(jìn)入 light sleep 模式,以盡可能低的功耗

2021-10-29 07:11:32

嗨,我在級聯(lián)模式下使用Xilinx DCM(數(shù)字時鐘管理器),使用6.144 MHz時鐘生成48 kHz時鐘。但是,由于我的設(shè)計相當(dāng)大(在區(qū)域內(nèi)),這種配置無法滿足時序約束并對整個設(shè)計產(chǎn)生影響。因此

2019-03-25 14:09:18

鎖定信號的上升沿是否與virtex-4 FPGA中DCM生成時鐘的上升沿對齊?

2020-07-13 09:50:56

和CLKIN同步(同相)。STATUS則指示DLL和PS的狀態(tài)。 DCM_BASE DCM_BASE是基本數(shù)字時鐘[url=]管理[/url]模塊的縮寫,是相位和頻率可配置的數(shù)字鎖相環(huán)電路,常用于FPGA系統(tǒng)中

2015-09-24 15:04:16

為了應(yīng)用FPGA中內(nèi)嵌的數(shù)字時鐘管理(DCM)模塊建立可靠的系統(tǒng)時鐘。首先對DCM的工作原理進(jìn)行分析,然后根據(jù)DCM的工作原理給出了一種DCM動態(tài)重配置的設(shè)計方法。DCM動態(tài)重配置設(shè)計是利

2010-07-28 17:03:52 28

28 基于FPGA的SoftSerdes設(shè)計與實(shí)現(xiàn)

0 引言

在高速源同步應(yīng)用中,時鐘數(shù)據(jù)恢復(fù)是基本的方法。最普遍的時鐘恢復(fù)方法是利用數(shù)字時鐘模塊(DCM)

2009-12-28 09:23:40 920

920

DCM主要功能1. 分頻倍頻:DCM可以將輸入時鐘進(jìn)行multiply或者divide,從而得到新的輸出時鐘。2. 去skew:DCM還可以消除clock的skew,所謂skew就是由于傳輸引起的同一時鐘到達(dá)

2010-06-05 11:48:09 7865

7865

DCM概述??? DCM內(nèi)部是DLL(Delay Lock Loop(?)結(jié)構(gòu),對時鐘偏移量的調(diào)節(jié)是通過長的延時線形成的。DCM的參數(shù)里有一個PHASESHIFT(相移),可以從0變到255。所以我們可以假設(shè)

2010-06-05 12:09:07 2419

2419

FPGA全局時鐘資源一般使用全銅層工藝實(shí)現(xiàn),并設(shè)計了專用時鐘緩沖與驅(qū)動結(jié)構(gòu),從而使全局時鐘到達(dá)芯片內(nèi)部的所有可配置單元(CLB)、I/O單元(IOB)和選擇性塊RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 在FPGA設(shè)計中,為了成功地操作,可靠的時鐘是非常關(guān)鍵的。設(shè)計不良的時鐘在極限的溫度、電壓下將導(dǎo)致錯誤的行為。在設(shè)計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3472

3472

本文介紹了XiLinx FPGA中DCM的結(jié)構(gòu)和相關(guān)特性,提出了一種基于XiLinx FPGA的DCM動態(tài)重配置的原理方法,并給出了一個具體的實(shí)現(xiàn)系統(tǒng)。系統(tǒng)僅通過外部和......

2012-05-25 13:42:50 39

39 低功耗時鐘門控算術(shù)邏輯單元在不同FPGA中的時鐘能量分析

2015-11-19 14:50:20 0

0 DCM:即 Digital Clock Manager 數(shù)字時鐘管理,關(guān)于DCM的作用: 顧名思義DCM的作用就是管理,掌控時鐘的專用模塊。

2017-02-11 11:30:40 1270

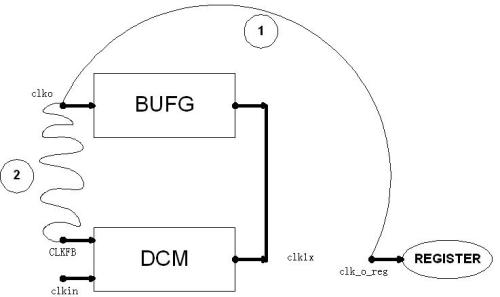

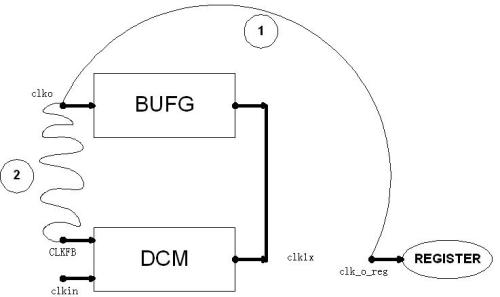

1270 在 Xilinx 系列 FPGA 產(chǎn)品中,全局時鐘網(wǎng)絡(luò)是一種全局布線資源,它可以保證時鐘信號到達(dá)各個目標(biāo)邏輯單元的時延基本相同。其時鐘分配樹結(jié)構(gòu)如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 8891

8891

設(shè)計的主時鐘,以達(dá)到最低的時鐘抖動和延遲。 FPGA全局時鐘資源一般使用全銅層工藝實(shí)現(xiàn),并設(shè)計了專用時鐘緩沖與驅(qū)動結(jié)構(gòu),從而使全局時鐘到達(dá)芯片內(nèi)部的所有可配置單元(CLB)、I/O單元(IOB)和選擇性塊RAM(Block Select RAM)的時延和抖動都為

2018-03-26 11:43:57 11

11 什么叫DCM(Digital Clock Management)? DCM內(nèi)部是DLL(Delay Lock Loop(?)結(jié)構(gòu),對時鐘偏移量的調(diào)節(jié)是通過長的延時線形成的。DCM的參數(shù)里有一個PHASESHIFT(相移),可以從0變到255。

2018-07-15 11:28:00 4759

4759 FPGA看上去就是一個四方形。最邊緣是IO Pad了。除去IO Pad,內(nèi)部還是一個四方形。四個角上各趴著一個DCM。上邊緣和下邊緣中間則各趴著一個全局Buffer的MUX。這樣的好處是四個DCM的輸出可以直接連接到全局Buffer的入口。

2018-05-05 10:38:00 5276

5276

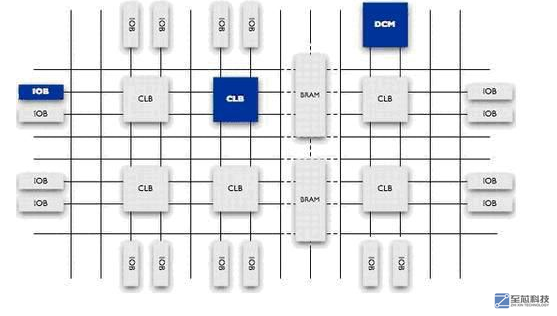

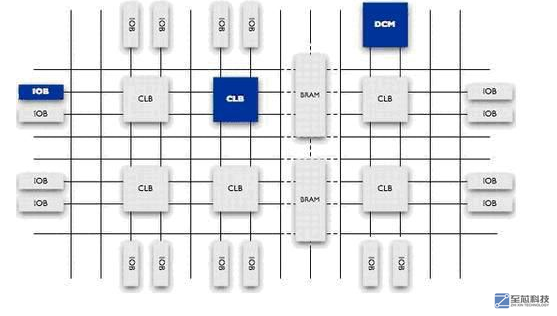

(ASIC型)模塊。如圖所示,FPGA芯片主要由7部分組成,分別為:可編程輸入輸出單元(IOB)、基本可編程邏輯單元(CLB)、完整的時鐘管理(DCM)、嵌入式塊RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。 1.可編程輸入輸出單元(IOB) 可編程

2018-05-25 14:11:47 8558

8558

有些FPGA學(xué)習(xí)者,看Xilinx的Datasheet會注意到Xilinx的FPGA沒有PLL,其實(shí)DCM就是時鐘管理單元。 1、DCM概述 DCM內(nèi)部是DLL(Delay Lock Loop結(jié)構(gòu)

2018-05-25 15:43:53 7884

7884

了解如何描述Spartan-6 FPGA中的全局和I / O時鐘網(wǎng)絡(luò),描述時鐘緩沖器及其與I / O資源的關(guān)系,描述Spartan-6 FPGA中的DCM功能。

2018-11-22 06:10:00 4862

4862 。 不要隨意將內(nèi)部信號作為時鐘,如門控時鐘和分頻時鐘,而要使用CLKDLL或者DCM產(chǎn)生的時鐘,或者可以通過建立時鐘使能或者DCM產(chǎn)生不同的時鐘信號。 FPGA盡量采取同步設(shè)計,也就是所有時鐘都是同一個源頭,如果使用兩個沒有相位關(guān)系的異步時鐘,必須

2020-12-11 10:26:44 1482

1482 區(qū)域(Region):每個FPGA器件被分為多個區(qū)域,不同的型號的器件區(qū)域數(shù)量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA

2020-12-09 14:49:03 20

20 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 一個fpga主要是由可編程輸入輸出單元(圖中的IOB模塊),可編程邏輯單元(CLB模塊),塊RAM(圖中的BRAM,也屬于內(nèi)嵌硬件),數(shù)字時鐘管理(DCM,也屬于內(nèi)嵌硬件),還有一些內(nèi)嵌的專用的硬件模塊(DSP),IOB寄存器就在圖中的IOB模塊中。

2020-12-28 17:13:11 19

19 一個fpga主要是由可編程輸入輸出單元(圖中的IOB模塊),可編程邏輯單元(CLB模塊),塊RAM(圖中的BRAM,也屬于內(nèi)嵌硬件),數(shù)字時鐘管理(DCM,也屬于內(nèi)嵌硬件),還有一些內(nèi)嵌的專用的硬件模塊(DSP),IOB寄存器就在圖中的IOB模塊中。

2020-12-28 17:13:09 9

9 引言:從本文開始,我們陸續(xù)介紹Xilinx 7系列FPGA的時鐘資源架構(gòu),熟練掌握時鐘資源對于FPGA硬件設(shè)計工程師及軟件設(shè)計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 4326

4326 FPGA-DCM使用詳解(通信電源技術(shù)期刊編輯部電話)-該文檔為FPGA-DCM使用詳解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,

2021-09-28 11:22:17 6

6 現(xiàn)代FPGA的體系結(jié)構(gòu)包括CLB陣列、塊RAM、乘法器、DSP、IOB和數(shù)字時鐘管理器(DCM)。延遲鎖定環(huán)(DLL)用于賦值具有均勻時鐘偏移的時鐘。XILINX SPARTAN系列FPGA的平面圖如下圖所示。

2022-03-22 09:48:38 2672

2672 將硬件實(shí)時時鐘 (RTC) 和篡改管理單元 (TAMP) 與 STM32 微控制器一起使用

2022-11-21 08:11:18 1

1 我們知道FPGA由LUT、IO接口、時鐘管理單元、存儲器、DSP等構(gòu)成,我覺得最能代表FPGA特點(diǎn)的就是LUT了。當(dāng)然不同廠家、同一廠家不同階段FPGA的LUT輸入數(shù)量是不同的,隨著技術(shù)的發(fā)展,LUT的輸入數(shù)量也在增加。

2023-05-25 09:29:18 2444

2444

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設(shè)計策略的基礎(chǔ)。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設(shè)計人員在他們的FPGA設(shè)計中或多或少都會用到。

2023-10-30 11:47:55 523

523

電子發(fā)燒友App

電子發(fā)燒友App

評論