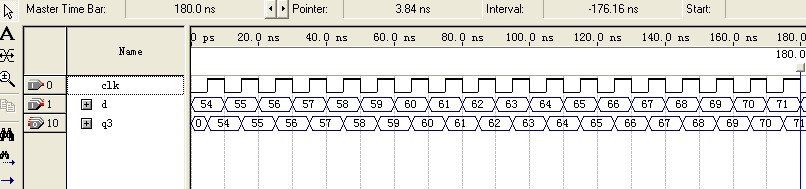

原文鏈接:學verilog 一個月了,在開發板上面寫了很多代碼,但是始終對一些問題理解的不夠透徹,這里我們來寫幾個例子仿真出阻塞和非阻塞的區別,我們先上代碼module LED ?(??? CLK, RSTn,??? scan,??? flag ,??? c,??? ,one,two,three,four);???? input CLK;???? input RSTn;???? input scan;???? output flag,c;???? output [3:0] one,two,three,four;/***********************************************************/??????? reg F1,F2;??? reg a,b;??? reg [3:0] one,two,three,four;?/********************信號傳遞之間的非阻塞賦值***************************************/??? always @ ( posedge CLK or negedge RSTn ) ??//????? if( !RSTn )???????? begin?????????? F1 <= 1'b1;?????????? F2 <= 1'b1;????? end????? else??begin???F1 <= scan;???F2 <= F1;????? end?/*******************信號傳遞之間的阻塞賦值****************************************/??? always @ ( posedge CLK or negedge RSTn ) ??//????? if( !RSTn )???????? begin?????????? a = 1'b1;?????????? b = 1'b1;????? end????? else??begin???a = scan;???b = a;????? end?/******************數據加? 非阻塞賦值? 先判斷后計數*****************************************/??????always @ ( posedge CLK or negedge RSTn )?? //one <=??if( !RSTn )???begin????one<=0;???end??else??begin???if(one==14)???????one<=0;???else ?????????one<=one+1;??end/***************數據加? 非阻塞賦值? 先計數后判斷********************************************/ ???always @ ( posedge CLK or negedge RSTn )??? //? two<=??if( !RSTn )???begin????two<=0;???end??else??begin???two<=two+1;???if(two==14)????two<=0;??end?/**************數據加? 阻塞賦值? 先判斷后計數*********************************************/?always @ ( posedge CLK or negedge RSTn ) ?//three =??if( !RSTn )???begin????three=0;???end??else??begin???if(three==14)????three=0;???else????three=three+1;??end/*************數據加? 阻塞賦值? 先計數后判斷**********************************************/?always @ ( posedge CLK or negedge RSTn ) ?//four =??if( !RSTn )???begin????four=0;???end??else??begin???four=four+1;???if(four==14)????four=0;??end????????????/****************信號之間傳遞***********************/?assign flag = F2 & !F1;assign c ?= b? & !a;/***************************************/?endmodule ?????2、我使用modesim 仿真,下面為我的? test bench?`timescale 1 ps/ 1 psmodule LED_vlg_tst();// constants??????????????????????????????????????????// general purpose registersreg eachvec;// test vector input registersreg CLK;reg RSTn;reg scan;// wires??????????????????????????????????????????????wire c;wire flag;wire [3:0]? four;wire [3:0]? one;wire [3:0]? three;wire [3:0]? two;// assign statements (if any)?????????????????????????LED i1 (// port map - connection between master ports and signals/registers???.CLK(CLK),?.RSTn(RSTn),?.c(c),?.flag(flag),?.four(four),?.one(one),?.scan(scan),?.three(three),?.two(two));/*initial???????????????????????????????????????????????begin?????????????????????????????????????????????????// code that executes only once???????????????????????// insert code here --> begin???????????????????????????????????????????????????????????????????????????????// --> end????????????????????????????????????????????$display("Running testbench");??????????????????????end???????????????????????????????????????????????????always????????????????????????????????????????????????// optional sensitivity list??????????????????????????// @(event1 or event2 or .... eventn)?????????????????begin?????????????????????????????????????????????????// code executes for every event on sensitivity list??// insert code here --> begin???????????????????????????????????????????????????????????????????????????????@eachvec;?????????????????????????????????????????????// --> end????????????????????????????????????????????end???????????????????????????????????????????????????endmodule*/initial beginCLK = 0;forever#10 CLK = ~CLK;?endinitial beginscan = 0;forever#100 scan = ~scan;?endinitial beginRSTn = 0;#1000 RSTn =? 1;#1000;#1000;#1000;#1000;#1000;#1000;#1000;#1000;$stop;endendmodule?主要就是初始化一個CLK 和scan的信號,然后就是初始化一下復位,最后就是設置仿真時間,這樣modesim 就不會一直處于仿真狀態,消耗資源,也可以方便仿真。?其中quartus? 與modesim? 互相調用調試,可以關注我的博客,這里我就不具體講解了!?3、modesim 波形圖??大家注意到紅線框內的數據變化,就能很清楚的理解 阻塞與非阻塞了!??微觀分析 阻塞與非阻塞1、上代碼,具體觀察,a,b,c與F1,F2,flage 的變化?module LED??(??? CLK, RSTn,??? scan,??? flag ,??? a,b,c,F1,F2,);???? input CLK;???? input RSTn;???? input scan;???? output flag,a,b,c;???? output F1,F2;/***********************************************************/??????? reg F1,F2;??? reg a,b;?/***********************************************************/??? always @ ( posedge CLK or negedge RSTn ) ??//????? if( !RSTn )???????? begin?????????? F1 <= 1'b1;?????????? F2 <= 1'b1;????? end????? else??begin???F1 <= scan;???F2 <= F1;????? end?/***********************************************************/??? always @ ( posedge CLK or negedge RSTn ) ??//????? if( !RSTn )???????? begin?????????? a = 1'b1;?????????? b = 1'b1;????? end????? else??begin???a = scan;???b = a;????? end?/***********************************************************/??????assign flag = F2 & !F1;assign c ?= b? & !a;/***************************************/?endmodule ????代碼涵義就不講解了?2、test bench 代碼,與上面相同,這里不重復了?3、上圖?? 看波形

深入分析verilog阻塞和非阻塞賦值

- Verilog(109207)

- 阻塞(8028)

- 非阻塞(2154)

相關推薦

FPGA基礎篇(一):阻塞與非阻塞賦值,不只是比原始信號差一個時鐘周期的問題!(深入剖析)

阻塞與非阻塞賦值 首先從名字上理解,阻塞賦值即賦值沒完成,后邊的語句將無法執行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續程序的執行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看

2017-09-19 18:32:43 11967

11967

11967

11967Verilog語言中阻塞和非阻塞賦值的不同

來源:《Verilog數字系統設計(夏宇聞)》 阻塞和非阻塞賦值的語言結構是Verilog 語言中最難理解概念之一。甚至有些很有經驗的Verilog 設計工程師也不能完全正確地理解:何時使用非阻塞

2021-08-17 16:18:17 6000

6000

6000

6000Verilog HDL語言編程的誤區與經驗

Verilog的兩個誤區:使用Reg類 型還是Net類型:Reg類 型只在過程塊中被賦值;而Net類型則在過 程塊外面被賦值或者驅動.阻塞賦值和非阻塞賦值:Verilog中競爭發生的條件:兩個或多個

2019-03-26 08:00:00

Verilog阻塞和非阻塞原理分析

Verilog阻塞和非阻塞原理分析在Verilog語言最難弄明白的結構中“非阻塞賦值”要算一個。甚至是一些很有經驗的工程師也不完全明白“非阻塞賦值”在仿真器(符合IEEE標準的)里是怎樣被設定執行

2009-11-23 12:02:57

Verilog中阻塞賦值和非阻塞賦值的正確使用

[table][tr][td] Verilog中有兩種為變量賦值的方法。一種叫做連續賦值,另一種叫做過程賦值。過程賦值又分為阻塞賦值和非阻塞賦值。阻塞性賦值使用“=”為變量賦值,在賦值結束前不可以進行其他操作,在賦值結束之后繼續后面的操作。這個過程就好像阻斷了程序的運行。非阻塞賦值使用“

2018-07-03 03:06:04

Verilog流水線加法器always塊中應該采用阻塞賦值(=),還是非阻塞賦值(<=)?

圖一圖二圖三圖四最近寫了一個16位二級流水線加法器,并進行了一下仿真。發現在always塊中采用阻塞賦值(=)和非阻塞賦值(

2016-09-09 09:18:13

Verilog過程賦值語句提問

時,dreg還是變成了areg這樣不就是延時3個時鐘周期了嗎?為什么不是這樣呢?另外,阻塞型賦值語句,規定是,順序執行語句,每種狀態一個接一個執行,非阻塞型賦值語句,規定是,并行賦值語句,當執行語句時同事計算

2017-09-20 15:10:01

verilog 非阻塞賦值的綜合

剛學verilog,試了一下非阻塞賦值,代碼如下, 很簡單module test(clk,in,out);input clk;input in;output reg out;always @(posedge clk)out

2012-10-30 09:20:14

verilog中的阻塞和非阻塞

這個是非阻塞賦值,b的值為0,仿真結果也是0module TOP(input clk,input rst,output reg b );reg a,c;always@(posedge clk or negedge rst)beginif(~rst)begina

2015-09-13 15:55:05

阻塞與非阻塞I/O

里面,因為硬件資源獲得的同時往往伴隨著一個中斷。 注意:驅動程序需要提供阻塞(等待隊列,中斷)和非阻塞方式(輪詢,異步通知)訪問設備。 休眠(被阻塞)的進程處于一個特殊的不可執行狀態。這點非常重要,否則

2018-07-09 08:19:59

阻塞與非阻塞I/O詳解

里面,因為硬件資源獲得的同時往往伴隨著一個中斷。 注意:驅動程序需要提供阻塞(等待隊列,中斷)和非阻塞方式(輪詢,異步通知)訪問設備。 休眠(被阻塞)的進程處于一個特殊的不可執行狀態。這點非常重要,否則

2018-07-04 07:23:24

阻塞(=)與非阻塞(<=)介紹

語句的執行,延遲后才執行賦值,這種賦值語句是不可綜合的,在需要綜合的模塊設計中不可使用這種風格的代碼。 非阻塞賦值操作符用小于等于號(即

2018-07-03 10:23:19

阻塞(=)與非阻塞(<=)介紹

語句的執行,延遲后才執行賦值,這種賦值語句是不可綜合的,在需要綜合的模塊設計中不可使用這種風格的代碼。 非阻塞賦值操作符用小于等于號(即

2018-07-09 05:08:55

非阻塞賦值容易錯語法點討論

本帖最后由 eehome 于 2013-1-5 10:05 編輯

非阻塞賦值容易錯語法點討論請教下大家!我發現光盤里的例程有一段是這樣子的:always @(dac_sta

2012-12-22 09:53:14

非阻塞分配是如何按順序或并行執行的?

嗨!我不明白非阻塞分配是如何按順序或并行執行的?永遠@(posedge clk)開始x = 2;y = x;結束VS永遠@(posedge clk)叉子x = 2;y = x;加入VS賦值x = 2

2019-04-22 10:02:08

FPGA在阻塞賦值中說是前邊賦值阻塞后邊賦值,但是看波形是同時變化

1,在阻塞賦值中,說是前邊賦值阻塞后邊賦值,但是看波形明明是同時變化,這是為什么?2,在if ,else if, else語句中說是順序執行,是時鐘跳一個周期判斷一次嗎,還是同時判斷,如果是同時判斷為什么說是順序執行?3,是組合邏輯中用=,非組合邏輯中用

2019-05-29 01:09:27

Linux設備驅動中的阻塞與非阻塞I/O

阻塞與非阻塞I/O阻塞操作是指在執行設備操作時若不能獲得資源則掛起進程,直到滿足可操作的條件后再進行操作。因為阻塞的進程會進入休眠狀態,因此,必須確保有一個地方能夠喚醒休眠的進程。喚醒進程的地方最大

2012-02-21 10:53:35

fpga基礎篇(一):阻塞與非阻塞賦值

`阻塞與非阻塞賦值首先從名字上理解,阻塞賦值即賦值沒完成,后邊的語句將無法執行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續程序的執行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看

2017-04-05 09:53:11

linux串口通信阻塞與非阻塞問題。

一般情況下串口通信中read()函數都是阻塞的。當然也可以通過設置文件等方法把串口設為非阻塞的。這里就有一個問題,當串口設置為阻塞狀況下,如果讀不到數據程序應該掛起。這種所謂的讀不到數據是指讀不到

2011-07-14 15:57:26

tcpclient_sample.c中設置recv非阻塞接收時出錯是何原因

,數據收發都已經正常實現。但是示例中recv是阻塞接收recv函數中flags傳參是0按照示例flags傳入0阻塞接收,程序運行沒有問題,但是將flags傳入MSG_DONTWAIT,希望實現非阻塞接收

2022-10-11 12:01:35

【FPGA學習】Verilog HDL的過程性賦值如何寫

語句完成執行;? 非阻塞性過程賦值:對目標的賦值是非阻塞的(因為時延),但可預定在將來某個時間發生。阻塞性過程賦值用操作符“=”完成,例如下面的實例:always@ (A or B or Cin

2018-09-26 09:16:55

【FPGA開源教程連載】第六章 阻塞賦值與非阻塞賦值

阻塞賦值與非阻塞賦值原理分析實驗目的:掌握阻塞賦值與非阻塞賦值的區別實驗平臺:無實驗原理:阻塞賦值,操作符為“=”,“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后

2016-12-25 01:51:24

【分享】Verilog中阻塞與非阻塞語句

移位寄存器:如果把上述代碼中的兩個賦值語句相互交換,如下所示,結果和上面是一樣的。所以在一個begin---end中的非阻塞語句并不會因為放置的位置不同,出現不同的結果。關于非阻塞的例子,分析的貌似蠻

2016-11-03 20:26:38

【工程源碼】 阻塞賦值與非阻塞賦值原理分析

的賦值語句會阻斷其后語句的正常執行,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。而且阻塞賦值可以看成是一步完成的,即:計算等號右邊的值并同時賦給左邊變量。非阻塞賦值,操作符為“

2020-02-24 20:09:13

【技巧分享】FPGA至簡設計-阻塞賦值與非阻塞賦值

阻塞與非阻塞作者:小黑同學一、 概述1、阻塞賦值對應的電路往往與觸發沿沒有關系,只與電平的變化有關系。阻塞賦值符號“=”。2、非阻塞賦值對應的電路結構往往與邊沿觸發有關系,只有在觸發沿時才有可能發生賦值的情況。非阻塞賦值符號“

2020-04-24 14:49:45

【夢翼師兄今日分享】 賦值語句的運用

立即學習>>夢翼師兄FPGA培訓(純視頻),手把手帶你入門FPGA寫在前面的話開發過程中,我們用的最多的恐怕就是賦值語句了,我們常用的賦值方式有兩種:阻塞賦值和非阻塞賦值。夢翼師兄剛開始

2019-12-22 14:21:37

【連載視頻教程(六)】小梅哥FPGA設計思想與驗證方法視頻教程之例解阻塞賦值與非阻塞賦值

,主要通過簡單的例子對比了Verilog語法中阻塞賦值和非阻塞賦值的區別,通過證明非阻塞賦值多種賦值順序生產電路的唯一性,與非阻塞賦值多種賦值書序生成電路的不確定性,來展示使用非阻塞賦對設計可預測性

2015-09-24 14:02:15

【鋯石科技】關于 Verilog HDL 語言的一些關鍵問題解惑【免費下載】

設計③ 如何給端口選擇正確的數據類型④ Verilog語言中latch的產生⑤ 組合邏輯反饋環⑥ 阻塞賦值與非阻塞賦值的不同⑦ FPGA的靈魂狀態機⑧ 代碼風格的重要性[hide][/hide]

2016-08-17 05:56:55

使用非阻塞的方式來處理并發的情況

如果我們要處理的情況符合下面的幾種之一,我們可以考慮一下使用非阻塞的方式來處理并發的情況。有多線程的情況要處理,但是很少出現并發沖突的,比如以讀取為主的涉及到的并發邏輯非常復雜,希望可以減低并發代碼

2021-08-24 08:11:32

關于阻塞性賦值與非阻塞性賦值的困惑

@ (posedge GlobalClk)RegC = RegB;由于過程性賦值立即發生,即沒有任何時延,所以根據首先執行哪一條always語句,RegC取不同的值,這就產生了競爭。書上說使用非阻塞性賦值可以避免產生競爭狀態,為什么??求助...

2013-11-07 10:16:34

關于串口讀寫阻塞,沒有設置非阻塞標志,為什么還能繼續打印

我打開這個串口的時候沒有設置非阻塞的標志,應該是默認阻塞的吧,但是上位機不向串口發送東西,也就是read沒有讀到東西的時候下面的printf還是會一直打印。我理解的阻塞就是程序一直等待在阻塞的地方,是不是我理解的有問題

2017-03-15 16:51:06

初學者讀夏宇聞老師書上一個問題,是關于阻塞賦值和非.....

阻塞賦值操作符用等號(即 = )表示。為什么稱這種賦值為阻塞賦值呢?這是因為在賦值時先計算等號右手方向(RHS)部分的值,這時賦值語句不允許任何別的 Verilog 語句的干擾,直到現行的賦值

2013-10-28 15:44:13

在verilog語句中,非阻塞賦值和小于等于均使用符號“<=”,如何區分<=所表示的含義?

)中,\"<=\"作為非阻塞賦值的一部分。

verilog中,一個語法結構不可能同時允許“表達式”和“語句”,

如果某處可以出現表達式,那么就不允許出現語句;

如果

2023-08-08 09:32:07

芯靈思Sinlinx A33開發板 Linux內核等待隊列poll ---阻塞與非阻塞

阻塞:阻塞調用是指調用結果返回之前,當前進程程會被掛起(休眠)。函數只有在得到結果之后才會返回。默認情況下,文件都是以這種方式打開。非阻塞:指在不能立刻得到結果之前,該函數不會阻塞當前進程程,而會

2019-02-12 16:08:52

請問如何從阻塞過渡到非阻塞I2C?

使用 _IT 函數轉移到一個非阻塞系統。只是將傳輸命令從 HAL_I2C_Master_Transmit 更改為 HAL_I2C_Master_Transmit_IT 突然將我所有的結果變成了屏幕上的亂碼,而不是像我以前那樣漂亮的文本。我需要做什么才能從阻塞 I2C 命令變為非阻塞 I2C 命令?

2023-02-06 06:00:18

基站阻塞和基站失步的概念區分及處理方法

本文簡單介紹了基站阻塞和基站失步兩個不同的概念,分析了兩者產生的原因,同時還詳細介紹了如何處理基站阻塞和基站失步問題的一些方法。基站阻塞和基站因空中失步產生

2009-08-01 16:16:56 17

17

17

17Java非阻塞通信研究

本文針對Java NIO 的特性做出分析與闡述,對網絡應用中阻塞通信與非阻塞通信、NIO的非阻塞工作機制以及網絡通信中非阻塞套接字的實現等問題進行了研究和探討,提出了系統地

2009-08-10 10:15:22 18

18

18

18verilog中阻塞賦值和非阻塞賦值

阻塞和非阻塞語句作為verilog HDL語言的最大難點之一,一直困擾著FPGA設計者,即使是一個頗富經驗的設計工程師,也很容易在這個點上犯下一些不必要的錯誤。阻塞和非阻塞可以說是血脈相連,但是又有著本質的差別

2011-03-15 10:57:34 6892

6892

6892

6892Verilog非阻塞賦值仿真

原標題:Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill! ATTN:所有括號內外注為理解方便或有疑問的地方,原文里并沒有。所有翻譯都是為遵循共同進步的理想但并沒有去努力得

2011-03-29 16:25:53 0

0

0

0Verilog HDL阻塞屬性探究及其應用

本文通過Verilog事件處理機制,詳細討論了阻塞與非阻塞賦值的區別、聯系及其應用示例。由本文可知,阻塞與非阻塞賦值靈活多變,底層實現也差異甚大。因而在數字電路設計時,依據

2011-08-28 17:59:19 575

575

575

575

Verilog編碼中的非阻塞性賦值

One of the most misunderstood constructs in the Verilog language is the nonblockingassignment. Even

2012-01-17 11:28:13 0

0

0

0Verilog HDL阻塞屬性簡介

VerilogHDL 中,有兩種過程賦值方式,即阻塞賦值(blocking)和非阻塞賦值(nonblocking)。阻塞賦值執行時,RHS(righthandstatement)估值與更新LHS(lefthandstatement)值一次執行完成,計算完畢,立即更新。

2012-05-23 09:55:51 1192

1192

1192

1192

veriolg中阻塞賦值與非阻塞賦值區別

在一開始學到阻塞和非阻塞的時候,所被告知的兩者的區別就在于阻塞是串行的,非阻塞是并行的。但是雖然知道這個不同點,有些時候還是很難真正區分用兩者電路的區別,下載資料內以一個簡單的串行流水線寄存器為例進行了分析。

2017-09-16 09:34:07 4

4

4

4FPGA學習系列:5.阻塞賦值與非阻塞賦值

設計背景: 阻塞 (=)和非阻塞(=)一直是在我們FPGA中討論的問題,資深的學者都是討論的是賦值應該發生在上升下降沿還是在哪里,我們在仿真中看的可能是上升下降是準確的,但是在時間電路中這就

2018-05-31 11:40:14 6358

6358

6358

6358

阻塞賦值和非阻塞賦值的用法一篇文章就夠了

對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2020-01-30 17:41:00 20977

20977

20977

20977verilog中阻塞賦值和非阻塞賦值到底有什么區別

1、阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。而且阻塞賦值可以看成是一步完成的,即:計算等號右邊的值并同時賦給左邊變量。

2020-04-25 08:00:00 0

0

0

0IEEE Verilog阻塞賦值和非阻塞賦值的區別

阻塞賦值對應的電路往往與觸發沿沒有關系,只與輸入電平的變化有關系。非阻塞賦值對應的電路結構往往與觸發沿有關系,只有在觸發沿時才有可能發生賦值的情況。

2020-06-17 11:57:41 10885

10885

10885

10885

VerilogHDL語言:清阻塞賦值和非阻塞賦值

對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微

2020-11-19 15:48:56 927

927

927

927基于阻塞賦值和非阻塞賦值的多級觸發器級聯實例

下面給出一個基于阻塞賦值和非阻塞賦值的多級觸發器級聯實例,要求將輸入數據延遲 3 個時鐘周期再輸出,并給出對應的 RTL 級結構圖和仿真結果。 (1)基于 D觸發器的阻塞賦值語句代碼如下

2021-05-08 14:47:05 1799

1799

1799

1799

簡述阻塞賦值和非阻塞賦值的可綜合性

阻塞賦值和非阻塞賦值的可綜合性 Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進程管理的術語。由于Verilog團隊是從C語言發展

2021-05-12 09:45:09 2398

2398

2398

2398

簡述Verilog HDL中阻塞語句和非阻塞語句的區別

? 在Verilog中有兩種類型的賦值語句:阻塞賦值語句(“=”)和非阻塞賦值語句(“=”)。正確地使用這兩種賦值語句對于Verilog的設計和仿真非常重要。 Verilog語言中講的阻塞賦值

2021-12-02 18:24:36 5005

5005

5005

5005

Verilog進行組合邏輯設計時的注意事項

由于賦值語句有阻塞賦值和非阻塞賦值兩類,建議讀者使用阻塞賦值語句“=”,原因將在“阻塞賦值和非阻塞賦值”中(現在還沒有寫)進行說明。

2022-03-15 10:40:20 1669

1669

1669

1669Verilog設計過程中的一些經驗與知識點

“ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括塊語句、阻塞賦值和非阻塞賦值 以及結構說明語句(initial, always, task, function)。”

2022-03-15 12:19:31 2064

2064

2064

2064時序邏輯中的阻塞和非阻塞

Verilog HDL的賦值語句分為阻塞賦值和非阻塞賦值兩種。阻塞賦值是指在當前賦值完成前阻塞其他類型的賦值任務,阻塞賦值由=來完成;非阻塞賦值在賦值的同時,其他非阻塞賦值可以同時被執行,非阻塞賦值由《=來完成。

2022-03-15 13:53:08 2524

2524

2524

2524在時序邏輯中使用阻塞賦值會怎么樣?

如例6.1所述,在多個“Always” 進程中使用阻塞賦值。程序塊“Always”在時鐘的正邊緣觸發,綜合器推斷時序邏輯。如前所述,所有阻塞賦值都在活動隊列中進行計算和更新。讀者請參閱之前分享的分層事件隊列一文。

2022-09-06 09:44:02 3306

3306

3306

3306verilog中阻塞賦值和非阻塞賦值的區別

阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。

2022-12-19 16:49:28 4607

4607

4607

4607Verilog中阻塞和非阻塞賦值金規

對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2023-06-01 09:21:57 514

514

514

514阻塞與非阻塞通信的區別 阻塞和非阻塞應用場景

阻塞通信(Blocking Communication):當進行阻塞通信時,調用者在發起一個I/O操作后會被阻塞,直到該操作完成返回才能繼續執行后續代碼。

2023-06-15 17:32:21 3580

3580

3580

3580虹科分享|關于阻塞函數和非阻塞函數

關于阻塞函數和非阻塞函數在CAN和LIN相關的開發庫里,不可避免的會出現“收”和“發”的函數。如何快速有效的處理數據,是開發中重要的事項。

2022-07-05 14:38:43 692

692

692

692

網絡IO模型:阻塞與非阻塞

阻塞 IO 模型 在Linux ,默認情況下所有的 socket 都是阻塞的,一個典型的讀操作流程如圖所示。 阻塞和非阻塞的概念描述的是用戶線程調用內核 IO 操作的方式:阻塞是指 IO 操作需要

2023-10-08 17:16:51 427

427

427

427

什么是阻塞?怎么設計才能滿足阻塞指標?

阻塞就是外部有阻塞干擾信號的時候,設備還可以正常運行。一般分為帶內阻塞和帶外阻塞,由于直放站都是做寬帶設備,一般只提帶外阻塞。

2023-10-10 11:22:37 546

546

546

546verilog同步和異步的區別 verilog阻塞賦值和非阻塞賦值的區別

Verilog是一種硬件描述語言,用于設計和模擬數字電路。在Verilog中,同步和異步是用來描述數據傳輸和信號處理的兩種不同方式,而阻塞賦值和非阻塞賦值是兩種不同的賦值方式。本文將詳細解釋

2024-02-22 15:33:04 202

202

202

202 電子發燒友App

電子發燒友App

評論