阻塞賦值和非阻塞賦值的可綜合性

Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進程管理的術語。由于Verilog團隊是從C語言發(fā)展,所以基于的C的術語和概念出現(xiàn)在EDA中,原本是一個“誤打誤撞”,但歷史造成的現(xiàn)實則是:必須理解和正確掌握它們的用法。

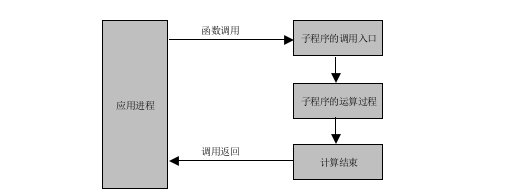

軟件中阻塞進程,是指調用返回之前,應用進程一直等待:

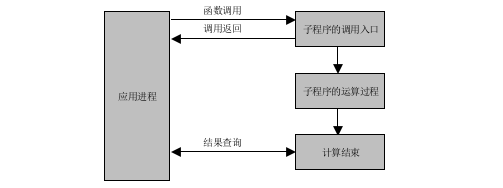

為了保證應用進程的效率,不至于被子程序的運算過程“掛起”。非阻塞進程得到應用:

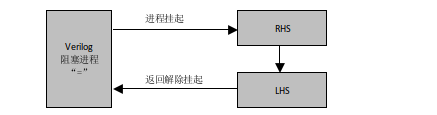

在非阻塞賦值進程中,無論子程序是否返回,不影響應用進程的正常運行。C語言的阻塞和非阻塞概念被Verilog團隊引用,Verilog的阻塞賦值:

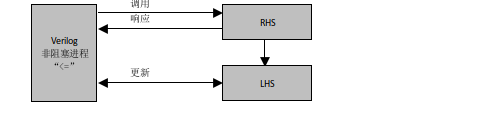

Verilog的非阻塞賦值:

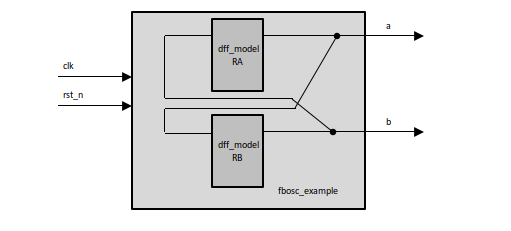

關于阻塞和非阻塞爭議中,有一個辯論雙方都引用的電路模型:反饋震蕩器:

其中,復位信號rst_n初始化RA(a)為0, RB(b)為1。觀察其物理連接,在時鐘沿作用下,兩個寄存器將互相交換數據。(同時交換)

為以上電路模型進行驗證,在循環(huán)行為體并分別使用阻塞賦值和非阻塞賦值。并驗證其前仿和后仿,觀察對比真實性。

應該得到的結論:

使用阻塞賦值:前仿不真實(沒有發(fā)生兩個寄存器的交換),后仿真實(發(fā)生交換)

使用非阻塞賦值:前仿真實(交換),后仿真實(交換)

基于以上結論:

“倒阻派”認為,沒有使用阻塞賦值的必要,必須在行為語句賦值中全部使用非阻塞。

“挺阻派”認為,基于電平敏感賦值用阻塞,沿敏感賦值用非阻塞,阻塞語句是必要的。

2000年以后,進入從“綜合為王”進入“驗證為王”的時代。同樣的Verilog代碼需要回到電腦中,用于非綜合目的。驗證代碼中的賦值驅動與軟件編寫概念相同,帶來非常大的便利。這就是“阻塞”賦值的反轉。

編輯:jq

-

非阻塞賦值

+關注

關注

0文章

11瀏覽量

10063 -

阻塞

+關注

關注

0文章

24瀏覽量

8244

原文標題:FPGA學習:阻塞賦值和非阻塞賦值的可綜合性

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

“串口阻塞”你真的會用嗎?

簡述阻塞賦值和非阻塞賦值的可綜合性

簡述阻塞賦值和非阻塞賦值的可綜合性

評論