【數(shù)字實驗室】在時序邏輯中使用阻塞賦值會怎么樣?

阻塞賦值的使用

如之前介紹所述,建議使用阻塞賦值來描述組合邏輯設計。但是,如果在編碼時序邏輯行為時使用阻塞賦值,會發(fā)生什么?這是需要解決的最重要的問題之一,對后續(xù)討論很重要。

如果阻塞賦值用于編碼時序邏輯的行為,則可以觀察到綜合結果不是正確的功能設計意圖。

接下來介紹使用阻塞賦值對時序電路設計進行編碼的幾個設計方案。

阻塞賦值和多個“Always”進程

如例6.1所述,在多個“Always” 進程中使用阻塞賦值。程序塊“Always”在時鐘的正邊緣觸發(fā),綜合器推斷時序邏輯。如前所述,所有阻塞賦值都在活動隊列中進行計算和更新。讀者請參閱之前分享的分層事件隊列一文。

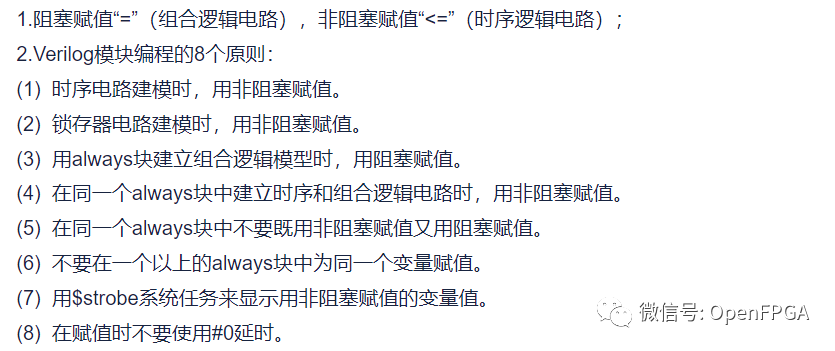

如例6.1所述,這兩個“Always” 進程并行執(zhí)行,并以兩位串行輸入串行輸出移位寄存器的形式生成輸出。首先,always進程生成一個輸出“b_in”從第一個“Always” 進程生成的輸出被另一個“Always” 進程用作輸入。因此,綜合器將其推斷為兩位串行輸入串行輸出移位寄存器。

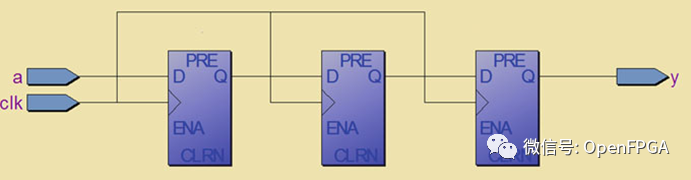

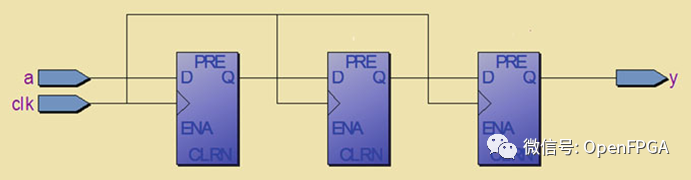

示例6.1的綜合邏輯如圖6.1所示,并具有輸入“a_in”,“clk”和輸出“y_out”

例6.1在多個always塊中阻塞賦值

圖6.1多個always塊中阻塞賦值的綜合邏輯

同一“always”進程中的阻塞賦值

如果阻塞賦值用于描述時序邏輯,并且在同一“always”程序塊中使用多個分配,則預期需求可能與綜合邏輯匹配,也可能與綜合邏輯不匹配。原因是,在阻塞分配中,所有后續(xù)語句(下一個立即數(shù))都被阻塞,除非直到當前語句被執(zhí)行。這將導致硬件截斷,并可能推斷出不需要的綜合輸出。

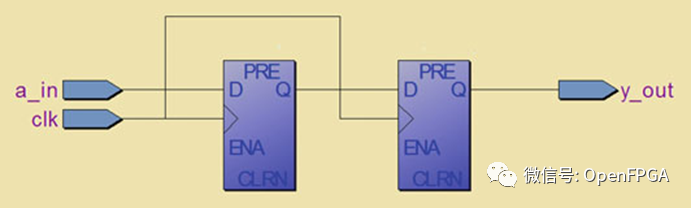

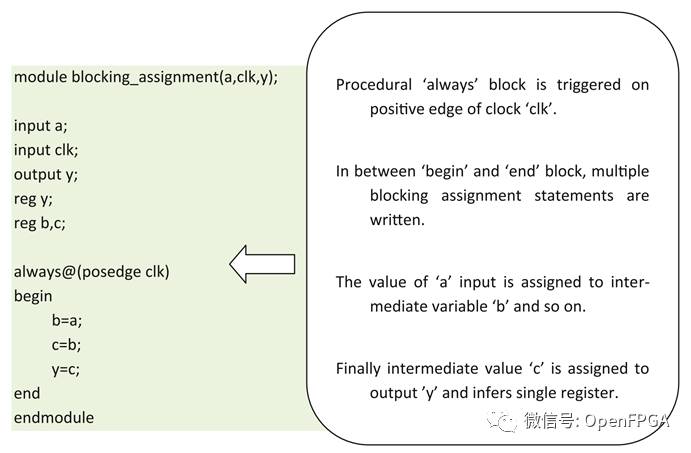

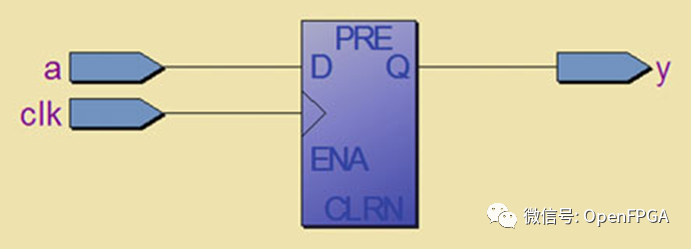

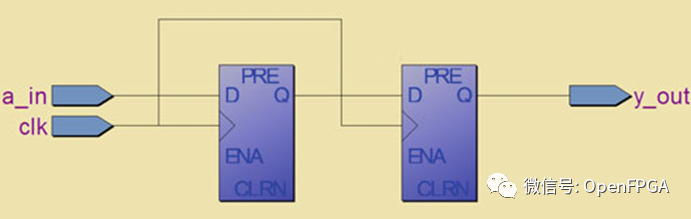

考慮在示例6.2中描述的設計場景,其意圖是創(chuàng)建三位串行輸入和串行輸出移位寄存器,但是在綜合示例6.2之后,它推斷為單個觸發(fā)器。

可綜合邏輯如圖6.2所示,其輸入為“a”、“clk”和輸出為“y”。所需的功能是串行輸入、串行輸出移位寄存器,但上述示例由于使用阻塞賦值而推斷出單個觸發(fā)器。因此,建議在為時序功能編碼或描述RTL時使用非阻塞賦值。

例6.2在always”進程中的阻塞賦值

圖6.2同一always進程中阻塞賦值的綜合邏輯

阻塞賦值示例

考慮在示例6.3中描述的設計場景,其意圖是創(chuàng)建三位串行輸入和串行輸出移位寄存器,并且由于塊“begin” 和 “end”中使用的阻塞賦值語句,它順序生成三位串行輸入串行輸出移位寄存器。

綜合邏輯如圖6.3所示,其輸入為“a”、“clk”和輸出“y”。所需的功能是串行輸入串行輸出移位寄存器,它推斷串行輸入串行輸出移位寄存器。因此,需要記住的重要一點是,程序“always”塊中的阻塞賦值語句的順序是綜合中的決定性因素。

例6.3同一always塊中的阻塞賦值(排序)

圖6.3阻塞賦值重新排序后的可綜合邏輯

非阻塞賦值

如之前介紹的“分層事件隊列”一文所述,非阻塞賦值在活動事件隊列中評估,并在NBA隊列中更新。非阻塞賦值用于描述時序邏輯。這些指定在程序塊“always”中使用,以獲得所需的綜合結果。所有非阻塞賦值在“always”塊內并行執(zhí)行。

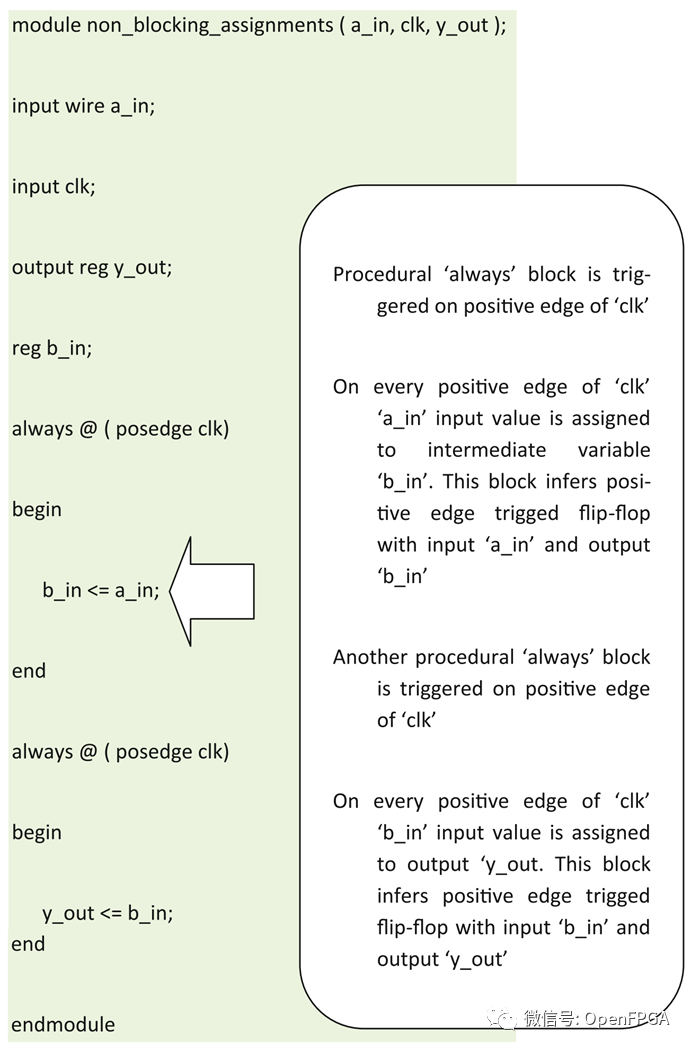

如例6.4所述。非阻塞賦值用于多個“always”塊。程序塊“always”在時鐘的正邊沿觸發(fā),綜合器推斷時序邏輯。綜合邏輯如圖6.4所示。

例6.4不同always塊中的非阻塞賦值

圖6.4不同always塊中的非阻塞賦值的綜合邏輯

非阻塞賦值示例

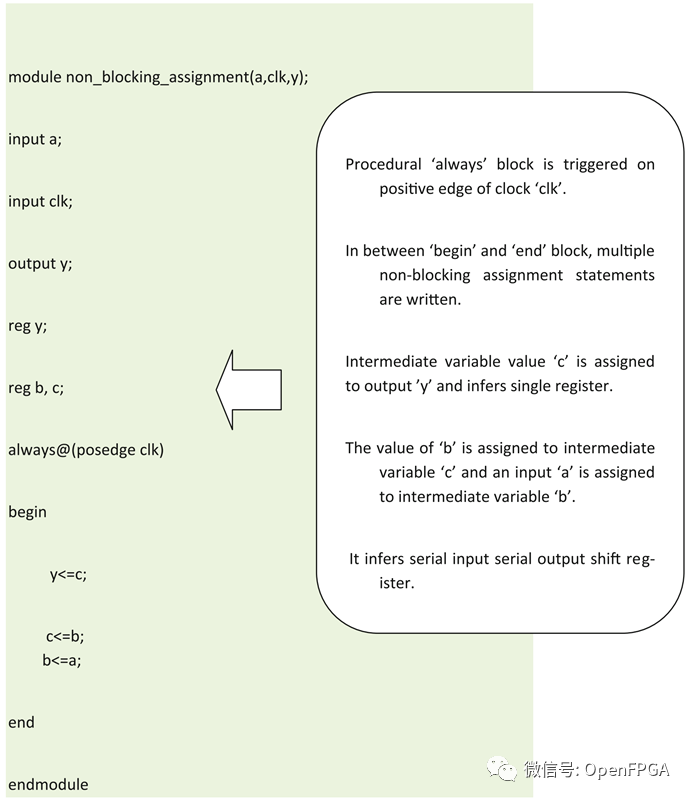

如果使用非阻塞賦值來描述時序邏輯,并且在同一“always”程序塊中使用多個賦值,則綜合器始終推斷出所需的預期邏輯。原因是,在非阻塞賦值中,“begin-end”塊中寫入的所有語句都是“并行”執(zhí)行的,這就產生了時序邏輯。

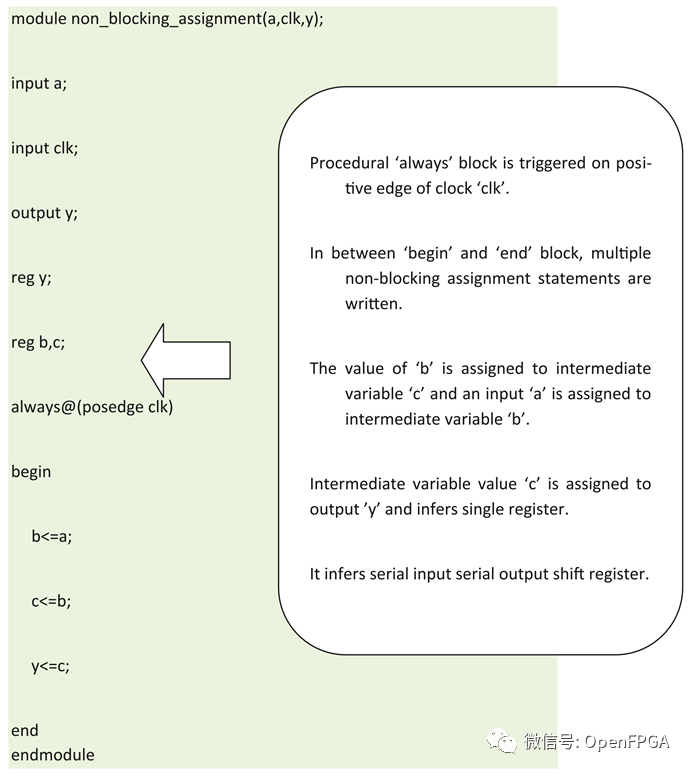

考慮示例6.5中描述的設計場景,意圖是創(chuàng)建三位串行輸入和串行輸出移位寄存器,使用非阻塞賦值。

綜合邏輯如圖6.5所示,其輸入為“a”、“clk”和輸出“y”。所需的功能是串行輸入串行輸出移位寄存器,它推斷串行輸入串行輸出移位寄存器。

例6.5同一always塊中的非阻塞賦值

圖6.5同一always塊中非阻塞賦值的綜合邏輯

非阻塞賦值的排序

考慮在示例中描述的設計方案,其意圖是創(chuàng)建三位串行輸入和串行輸出移位寄存器,并使用非阻塞賦值。

上一節(jié)中的實例,在本例6.6中重新排序。

綜合邏輯如圖6.5所示,其輸入為“a”、“clk”和輸出“y”。所需的功能是串行輸入串行輸出移位寄存器,它推斷串行輸入串行輸出移位寄存器。所以,重要的一點是要記住,過程“always”塊中非阻塞賦值語句的順序不是推斷邏輯的決定性因素。

例6.6在同一always塊中具有順序更改的非阻塞賦值

總結

不總結了,例子很多建議自己測試。

審核編輯 :李倩

-

寄存器

+關注

關注

31文章

5421瀏覽量

123319 -

電路設計

+關注

關注

6698文章

2518瀏覽量

211157 -

時序邏輯

+關注

關注

0文章

39瀏覽量

9340

原文標題:【數(shù)字實驗室】在時序邏輯中使用阻塞賦值會怎么樣?

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

在時序邏輯中使用阻塞賦值會怎么樣?

在時序邏輯中使用阻塞賦值會怎么樣?

評論