對于需要高動態范圍的應用,通常使用∑-Δ轉換器。這些應用主要可以在化學分析、醫療保健和體重管理領域找到。但是,其中許多模塊無法快速轉換。

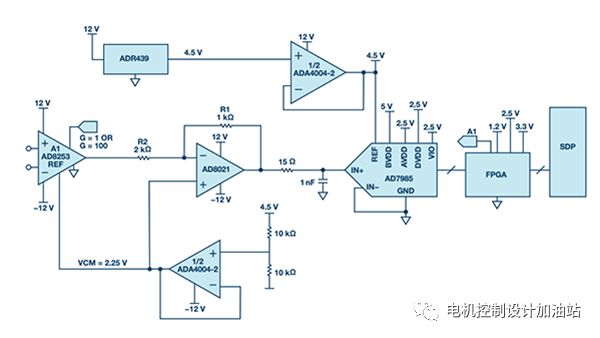

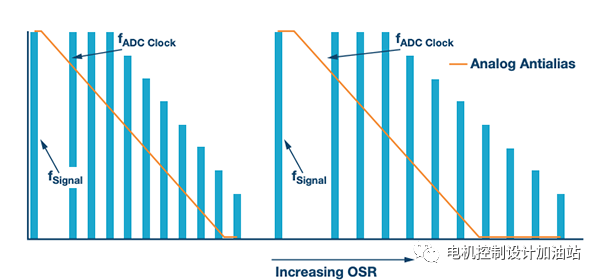

圖1中的電路顯示了帶有2.5 MSPS和上游可編程儀表放大器的16位SAR轉換器,它將增益設置為1或100。通過在FPGA中進行過采樣和數字信號處理,該電路可實現大于125 dB的動態范圍,并且仍然非常安靜。高動態范圍是通過AD8253的自動切換和過采樣實現的,其中信號的采樣速率遠高于奈奎斯特頻率。根據經驗,采樣頻率加倍可在原始信號帶寬下將信噪比(SNR)提高約3 dB。在圖1所示的電路中,仍然在FPGA中應用數字濾波,以消除高于目標信號帶寬的噪聲。原理如圖2所示。

圖1. 具有自動增益調節功能的SAR轉換器。

為了獲得最大動態范圍,在輸入端使用儀表放大器將極低信號放大100倍。有關噪聲的一些注意事項如下:

對于>126 dB的動態范圍要求,在3 V (6 V p-p)輸入信號時產生的最大噪聲級為1 μV rms。AD7985是具有2.5 MSPS的16位SAR轉換器。如果它以600 kSPS(低功率損耗為11 mW)和72過采樣系數運行,則產生大約8 kSPS的采樣率,因此帶寬為4 kHz。在這些條件下,將產生最大15.8 nV/√Hz的噪聲密度(ND)。該值對于選擇正確的儀表放大器很重要。ADC通常具有89 dB的SNR,而系數為72的過采樣會額外增加18 dB,因此仍需要大約20 dB才能達到126 dB的目標,這是儀表放大器的任務。AD8253的增益為100時,其值為11 nV/√Hz。下方用作ADC驅動器和用于電平調節的AD8021又增加了2.1 nV/√Hz的噪聲。

圖2. 過采樣的增加消除了部分噪聲。

模擬信號鏈由基準電壓ADR439(或REF194)以及ADA4004-2完成,作為基準緩沖區和驅動器,用于產生偏移電壓。

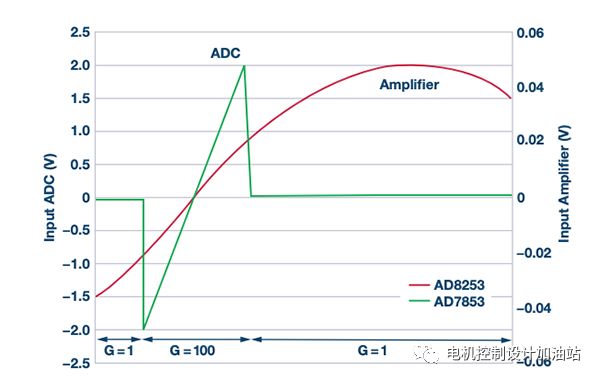

除模擬路徑中的組件外,FPGA(或處理器)對電路性能也很重要。關鍵任務是將儀表放大器的增益從1切換為100。為此,對許多閾值進行了編程以確保ADC不飽和。因此,AD8253在輸入電壓高達20 mV左右時以100為增益運行,這使得ADC輸入端的最大電壓達2.0 V。然后,FPGA將AD8253的增益降至1且沒有延遲,以防止過載(見圖3)。

圖3. 增益開關示例。

電路的變化可通過AD7980(16位、1 MSPS)、AD7982(18位、1 MSPS)或AD7986(18位、2 MSPS)等其他ADC操作。同樣,不使用增益為1、10、100和1000的AD8253,而改用具有較低范圍的AD8251等儀表放大器(增益為1、2、4和8)。基準電壓的選擇也可能會改變。

-

ADI

+關注

關注

148文章

46022瀏覽量

258576 -

pga

+關注

關注

1文章

107瀏覽量

41881

原文標題:采用PGA的SAR轉換器可實現125 dB的動態范圍

文章出處:【微信號:motorcontrol365,微信公眾號:電機控制設計加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

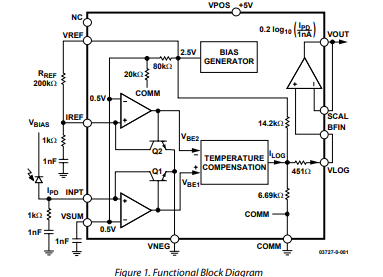

AD8305 100 dB范圍(10nA-1mA)對數轉換器技術手冊

ADL5310 120 dB范圍(3 nA-3 mA)雙通道對數轉換器技術手冊

ADL5306 60 DB范圍(100 NA-100 μ A)低成本對數轉換器技術手冊

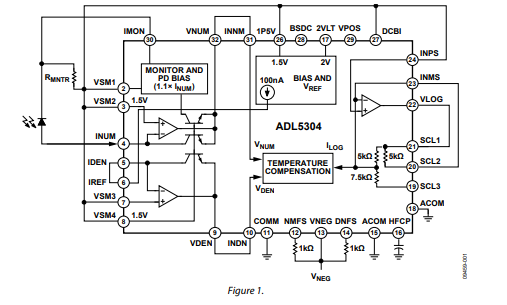

ADL5304高速、200 DB范圍對數轉換器技術手冊

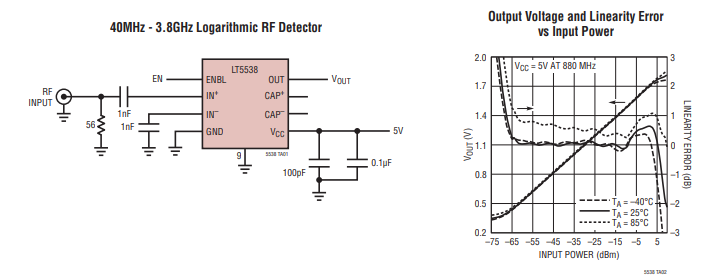

LT5538具75dB動態范圍的40MHz至3.8GHz RF功率檢波器技術手冊

AN-1279: 如何過采樣5 MSPS、18/16位精密SAR轉換器以便增加動態范圍

請問有沒有滿足-2V~+2V這個信號范圍的ADC模數轉換器?

什么是無雜散動態范圍 (SFDR)?為什么 SFDR 很重要?

ADS1218精密、寬動態范圍、模數(A/D)轉換器數據表

ADS1252精密、寬動態范圍、模數(A/D)轉換器數據表

ADS1253精密、寬動態范圍、模數(A/D)轉換器數據表

ADS1251精密、寬動態范圍、模數(A/D)轉換器數據表

ADS1240和ADS1241精密、寬動態范圍、模數轉換器數據表

ADS850高動態范圍、14位模數轉換器(ADC)數據表

技術 | 采用PGA的SAR轉換器可實現125 dB的動態范圍

技術 | 采用PGA的SAR轉換器可實現125 dB的動態范圍

評論