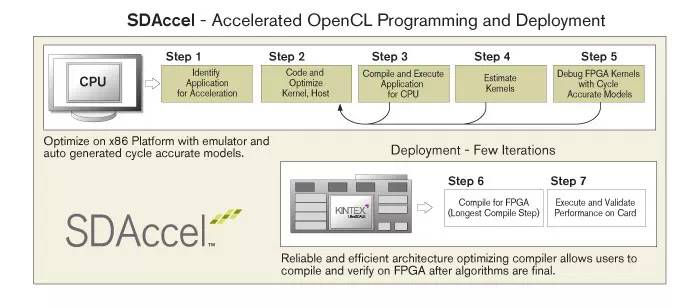

All Programmable 技術和器件的全球領先企業(yè)賽靈思公司(Xilinx, Inc. ( NASDAQ:XLNX ))今天宣布推出面向 OpenCL、C 和 C++ 的2015.1 版本SDAccel 開發(fā)環(huán)境。SDAccel是面向系統(tǒng)和軟件工程師而打造的 SDx 系列開發(fā)環(huán)境成員之一,可將利用FPGA實現(xiàn)數(shù)據(jù)中心應用加速的性能功耗比提升高達 25 倍之多。新版 SDAccel 開發(fā)環(huán)境增強了 SDAccel 集成開發(fā)環(huán)境(IDE)的特性,擴展了 OpenCL 標準合規(guī)性,并擁有了一個由 SDAccel 認證聯(lián)盟成員所組成的更強大的生態(tài)系統(tǒng),用以提供平臺、庫和設計服務。

SDAccel開發(fā)環(huán)境增強功能

SDAccel 開發(fā)環(huán)境 2015.1 版本新增了調試和特性分析功能,讓基于 Eclipse 的 IDE 變得更簡單易用,可加速 OpenCL、C 和 C++ 內核的開發(fā)與部署。此外,新版 SDAccel 開發(fā)環(huán)境擴展了 SDAccel 的 Khronos 標準合規(guī)性,現(xiàn)可支持新的 OpenCL ICD (Installable Client Driver)客戶端驅動程序。擴展 ICD 支持后,OpenCL 的多種實現(xiàn)方案可在同一系統(tǒng)中共存,從而使應用開發(fā)人員能夠在CPU、GPU和FPGA之間實時切換,加速運行時間并降低功耗。

“ Bitfusion 通過硬件加速器、獨特的軟件抽象化和各種庫的完美組合,最大限度地提升了現(xiàn)有數(shù)據(jù)中心應用的性能。我們支持即插即用加速,同時也高度依賴于底層廠商的硬件和工具來提供高級性能。作為賽靈思 Kintex UltraScale FPGA 和 SDAccel 開發(fā)環(huán)境的用戶,我們非常高興能夠借助賽靈思所提供的不斷發(fā)展演進的設計環(huán)境和強大支持,面向生物信息、科學計算、搜索、計算機視覺和媒體編碼等領域的應用展示我們行業(yè)領先的 OpenCL FPGA加速器。”

——Subbu Rama, BitFusion.io 公司 CEO

不斷向平臺、庫和設計服務供應商擴展的生態(tài)系統(tǒng)

在2014年11月宣布推出的 SDAccel認證生態(tài)系統(tǒng)基礎上,賽靈思已經(jīng)迎來更多提供開發(fā)板、特定市場專用庫和設計服務的新聯(lián)盟成員。新的開發(fā)板包括賽靈思 Kintex UltraScale KCU105 評估套件、支持混合儲存立方體( HMC)的美光( Micron) Pico Computing SB-850 開發(fā)板, Alpha Data ADM-PCIE-KU3 開發(fā)板和 4DSP CES820 現(xiàn)成商用(COTS)小型嵌入式系統(tǒng)。

全新的和更新的賽靈思最佳庫包括 OpenCV、BLAS 和Auviz Systems 提供的機器學習深度神經(jīng)網(wǎng)絡(DNN)庫。此外,新聯(lián)盟成員 ArrayFire 也提供了機器學習庫。

“ ArrayFire 素以快速發(fā)展的 GPU 計算軟件庫聞名。ArrayFire 庫只需幾行就能取代原始代碼數(shù)十行,能節(jié)約寶貴的時間,降低開發(fā)成本。我們已經(jīng)與賽靈思合作,在 SDAccel 開發(fā)環(huán)境上充分利用我們在特定領域的 Arrayfire 專業(yè)技術,為數(shù)據(jù)中心基于 FPGA 的 OpenCL 應用加速打造了一個機器學習庫和各種設計服務。”

——John Melonakos, ArrayFire 公司 CEO

除了加速終端應用開發(fā)所需的算法、庫和 FPGA 內核外,賽靈思還打造了一個由設計服務聯(lián)盟成員構成的全球生態(tài)系統(tǒng),幫助全球設計團隊推動 OpenCL、C 和 C++ 應用的 FPGA 加速。

新的設計服務成員包括:

ArrayFire

Cluster Technology Limited

Impulse Accelerated Technologies

Instigate Design,Irish Centre for High-End Computing (ICHEC)

MulticoreWare

關于賽靈思

賽靈思是All Programmable器件、SoC和3D IC的全球領先供應商,其行業(yè)領先的產(chǎn)品與新一代設計環(huán)境以及IP核完美地整合在一起,可滿足客戶對可編程邏輯乃至可編程系統(tǒng)集成的廣泛需求。

-

生態(tài)系統(tǒng)

+關注

關注

0文章

707瀏覽量

20975 -

集成開發(fā)環(huán)境

+關注

關注

0文章

69瀏覽量

17872

發(fā)布評論請先 登錄

【AD新聞】賽靈思新CEO訪華繪藍圖,7nm ACAP平臺要讓CPU/GPU難企及

工廠生產(chǎn)系統(tǒng)能效的生態(tài)系統(tǒng)優(yōu)化設計

PlatformIO物聯(lián)網(wǎng)開發(fā)生態(tài)系統(tǒng)簡介

Xilinx 發(fā)布數(shù)據(jù)中心生態(tài)系統(tǒng)投資計劃

Xilinx拓展生態(tài)系統(tǒng)和平臺強化嵌入式視覺和工業(yè)物聯(lián)網(wǎng)產(chǎn)品組合

java微服務生態(tài)系統(tǒng)模型解讀

賽靈思擴大生態(tài)系統(tǒng),重塑嵌入式視覺、工業(yè)物聯(lián)網(wǎng)系統(tǒng)設計的未來

賽靈思擁有更強大平臺、庫和設計服務生態(tài)系統(tǒng)

賽靈思擁有更強大平臺、庫和設計服務生態(tài)系統(tǒng)

評論