臺積電此次揭露 3D IC 封裝技術成功,正揭開半導體工藝的新世代。目前業界認為,此技術主要為是為了應用在5納米以下先進工藝,并為客制化異質芯片鋪路,當然也更加鞏固蘋果訂單。

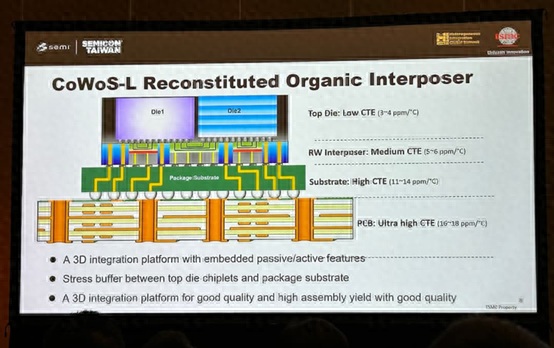

臺積電近幾年推出的 CoWoS 架構及整合扇出型封狀等原本就是為了透過芯片堆棧摸索后摩爾定律時代的路線,而真正的3D封裝技術的出現,更加強化了臺積電垂直整合服務的競爭力。尤其未來異質芯片整合將會是趨勢,將處理器、數據芯片、高頻內存、CMOS 影像傳感器與微機電系統等整合在一起。

臺積電強調,CoWoS及整合扇出型封裝(InFO)仍是2.5D IC封裝,為了讓芯片效能更強,芯片業花了相當的時間,開發體積小、功能更復雜的3D IC,這項技術需搭配難度更高的矽鉆孔(TSV)技術,以及晶圓薄化、導電材質填孔、晶圓連接及散熱支持。

封裝不同工藝的芯片將會是很大的市場需求,半導體供應鏈的串聯勢在必行。所以令臺積電也積極投入后端的半導體封裝技術,預計日月光、矽品等封測大廠也會加速布建3DIC封裝的技術和產能。不過這也并不是容易的技術,需搭配難度更高的工藝,如硅鉆孔技術、晶圓薄化、導電材質填孔、晶圓連接及散熱支持等,將進入新的技術資本競賽。

臺積電總裁魏哲家表示,盡管半導體處于淡季,但看好高性能運算領域的強勁需求,且臺積電客戶組合將趨向多元化。不過目前臺積電的主要動能仍來自于 7 納米工藝,2020年6納米才開始試產,3D封裝等先進技術屆時應該還只有少數客戶會采用,業界猜測蘋果手機處理器應該仍是首先引進最新工藝的訂單。更進一步的消息,要等到5月份臺積大會時才會公布。

-

傳感器

+關注

關注

2562文章

52560瀏覽量

763675 -

芯片

+關注

關注

459文章

52169瀏覽量

436125 -

臺積電

+關注

關注

44文章

5740瀏覽量

168943

原文標題:臺積電完成全球首顆 3D IC 封裝,預計明年量產

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

消息稱臺積電完成CPO與先進封裝技術整合,預計明年有望送樣

西門子擴大與臺積電合作推動IC和系統設計

臺積電先進封裝產能加速擴張

臺積電封裝,新規劃

臺積電完成全球首顆 3D IC 封裝

臺積電完成全球首顆 3D IC 封裝

評論