隨著電路設計日趨復雜和高速,如何保證各種信號(特別是高速信號)完整性,也就是保證信號質量,成為難題。此時,需要借助傳輸線理論進行分析,控制信號線的特征阻抗匹配成為關鍵,不嚴格的阻抗控制,將引發相當大的信號反射和信號失真,導致設計失敗。常見的信號,如PCI 總線、PCI-E 總線、USB、以太網、DDR 內存、LVDS 信號等,均需要進行阻抗控制。阻抗控制最終需要通過 PCB 設計實現,對 PCB 板工藝也提出更高要前期我司有推出關于阻抗計算則及基礎知識等技術文檔,為滿足部分客戶的需求,以下將介紹我司常規的4 層板各種板厚的疊層結構及部分常見阻抗計算結果,有需求的客戶可根據以下建議參數設計阻抗線寬、間距:

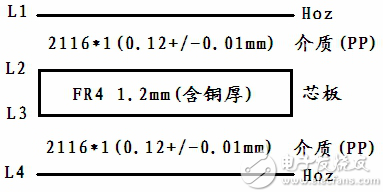

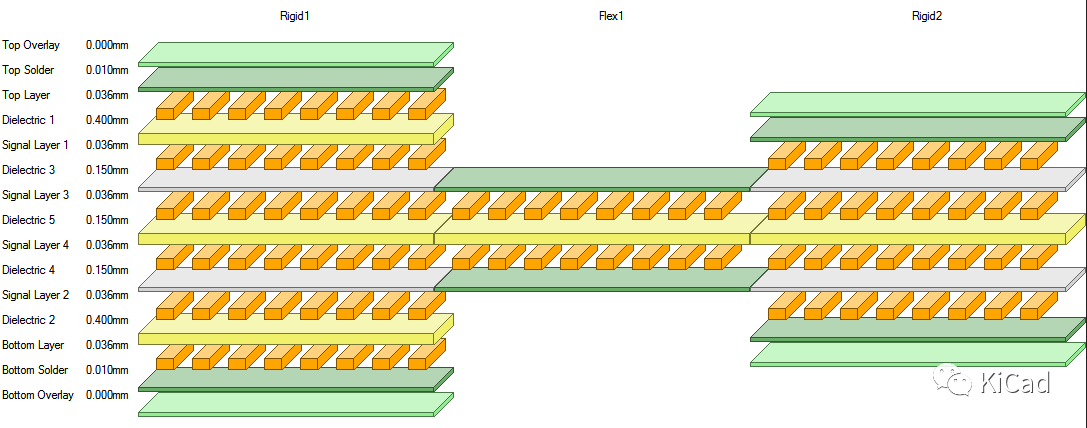

1. 成品板厚 1.6mm(疊層結構):

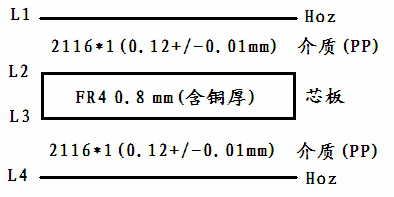

2. 成品板厚 1.2mm(疊層結構):

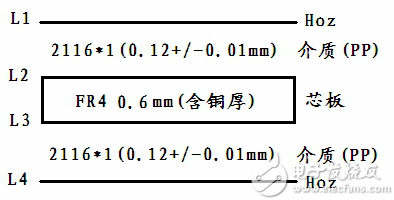

3. 成品板厚 1.0mm(疊層結構):

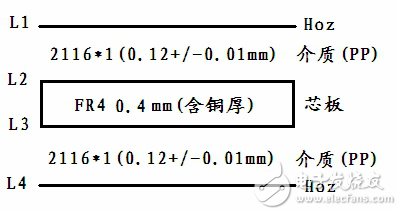

4.成品板厚0.8mm(疊層結構):

以上四種層壓結構為我司4 層板常規壓合疊層結構,從圖中可以看出,常規壓合結構中用的 PP 均為 2116,厚度約為 0.12mm。

針對我司常規的壓合結構,常規的阻抗線(如 L1 層阻抗線參考 L2 層 & L4 層阻抗線參考 L3 層)參數可參考以下計算結果:

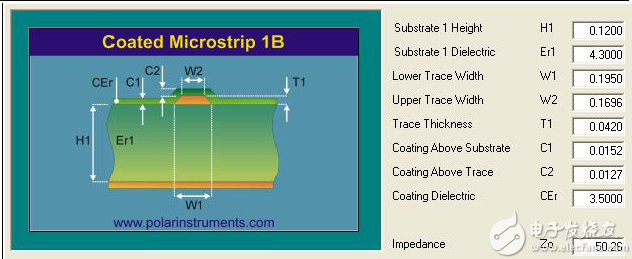

1.外層線寬 0.195mm,控制單端阻抗 50+/-10%歐姆(L1 Ref L2 層,L4 層 Ref L3層)

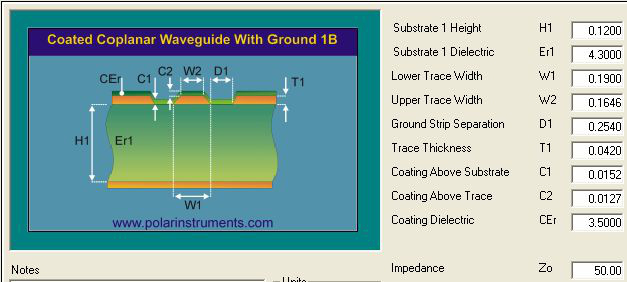

2. 雙面線寬 0.19mm,線到銅皮間距 0.254mm,控制單端共面阻抗 50+/-10%歐姆(L1 Ref L2 層,L4 層 Ref L3 層)

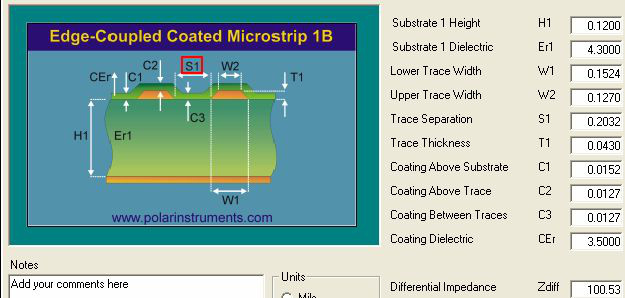

3. 雙面線寬 0.1524mm,線距 0.2032mm,控制差分阻抗 100+/-10%歐姆(L1 Ref L2 層,L4 層 Ref L3 層)

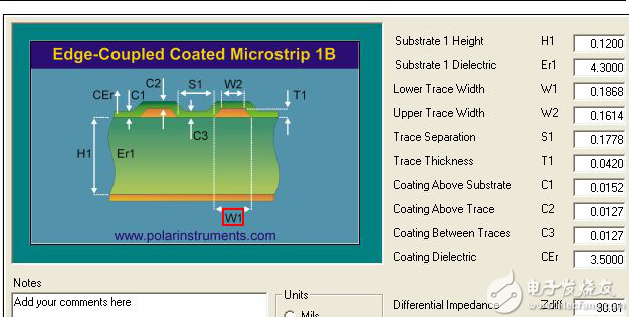

4. 雙面線寬 0.1868mm,線距 0.1778mm,控制差分阻抗 90+/-10%歐姆(L1 Ref L2 層,L4 層 Ref L3 層)

-

pcb

+關注

關注

4356文章

23438瀏覽量

407152 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43767

發布評論請先 登錄

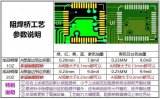

Allegro Skill封裝原點-優化焊盤

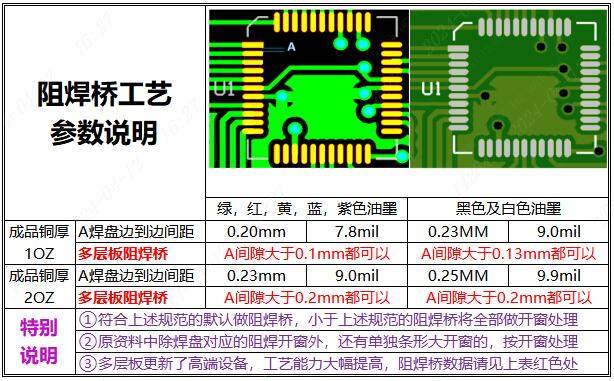

PCB四層板常規層壓結構及設計阻焊是怎樣的

PCB四層板常規層壓結構及設計阻焊是怎樣的

評論