通常,我們優先解決建立時間違例。Setup slack與邏輯延遲、布線延遲、時鐘歪斜和時鐘不確定性有關。因此,首先要明確這幾個因素中哪個因素對建立時間違例起關鍵作用。具體的衡量標準可由如下幾個數值確定。這也是ug1292第三頁的主題。

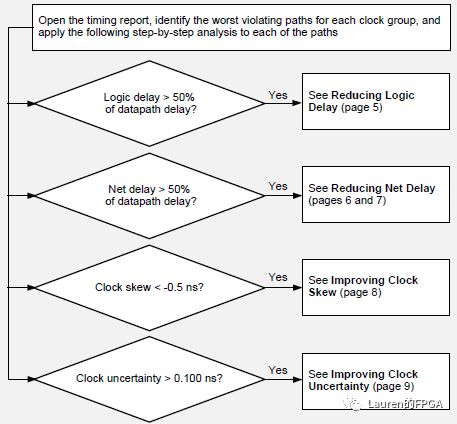

ug1292第三頁也給出了建立時間違例分析流程,如下圖所示。當邏輯延遲占比超過50%時,要著重降低邏輯延遲;當布線延遲占比超過50%時,要把焦點放在布線延遲上;同時,也要關注一下時鐘歪斜和時鐘不確定性。當時鐘歪斜小于-0.5ns或時鐘不確定性大于0.1ns時,兩者將成為時鐘違例的主要“貢獻者”。

圖片來源, page 3, ug1292

上述四個數值,無論是在timing report(通過report_timing_summary生成)還是design analysis report(通過report_design_analysis生成)中都有所體現。以timingreport為例,如下圖所示,可清晰地顯示上述四個數值。

圖片來源, page 3, ug1292

注:上述數據只針對UltraScale系列芯片。

-

時鐘

+關注

關注

11文章

1879瀏覽量

132836 -

邏輯

+關注

關注

2文章

834瀏覽量

29694

原文標題:深度解析ug1292(3)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片設計進階之路—從CMOS到建立時間和保持時間

DC綜合建立時間的關鍵路徑分析的問題?

建立時間和保持時間討論

快速建立時間的自適應鎖相環

時延和建立時間在ADC電路中的區別

ug1292深度解析

UG1292使用之初始設計檢查使用說明

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

UltraFast設計方法時序收斂快捷參考指南(UG1292)

深度解析ug1292建立時間違例分析流程

深度解析ug1292建立時間違例分析流程

評論