寄存器以及建立保持時間,傳輸延遲的介紹

寄存的圖標一般如下圖(忽略復位端)。

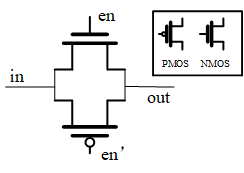

這里先介紹一下傳輸門。CMOS傳輸門如下圖所示。由一個PMOS和一個NMOS組成。en接NMOS的G端,en的反向en’ 接PMOS的G端。我們知道,NMOS的G端為高電平時,NMOS管兩端導通;PMOS的G端為低電平時,PMOS管兩端導通。故當en為高時,PMOS和NMOS管都導通,輸入in可以傳輸到out端;否則,傳輸門關閉。

問題:為什么要用兩個管子,一個PMOS和一個NMOS來實現傳輸門,而不只用一個NMOS管,或者PMOS來實現傳輸門?

答案:前面講CMOS實現與或門時已經提過。

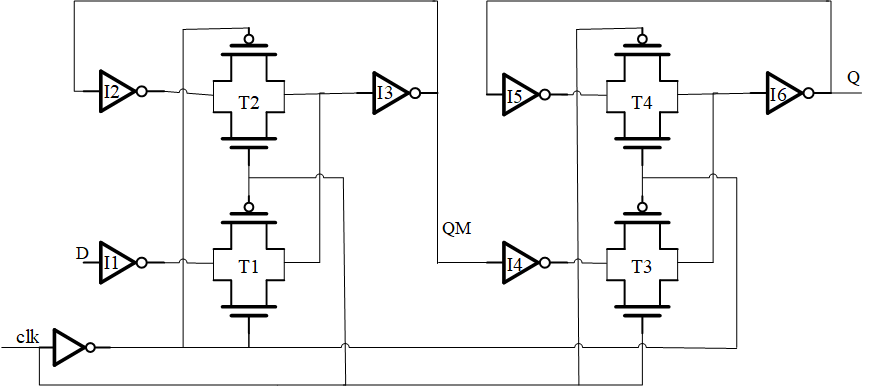

下面給出主從上升沿觸發的寄存器MOS級電路圖。可以看到,前后兩級電路一致,就是傳輸門的clk接法相反,故叫主從式。

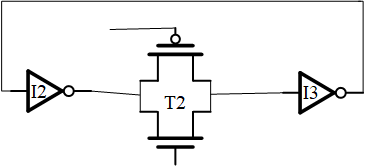

當時鐘信號為低電平時,傳輸門T1導通,數據經過反相器I1,傳輸門T1,反相器I3,傳到QM端。此時T2,T3傳輸門為關閉狀態。T4為導通狀態,故此時后面半部分的電路結構如下。相當于兩個反相器首尾相連,這就是一個瑣存結構,維持數據Q不變。

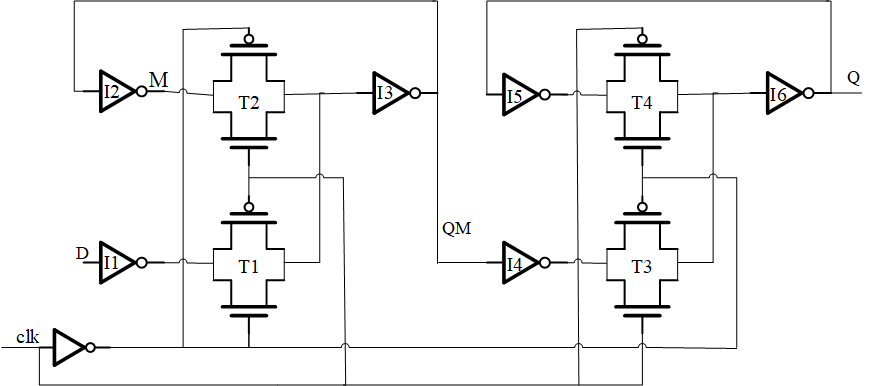

當時鐘clk由低電平變成高電平之后,T3導通,原本在clk為低電平時傳到QM的數據被傳輸到后面的Q端。此時T4是關閉的。但是前半部分電路當clk變成高電平之后傳輸門T1關閉,新的數據D進不來了。而此時T2導通,結構如下,也是一個瑣存結構,此時維持低電平時送進來的數據不變。

由上面的分析可得,當clk為低電平時,T1導通,新的數據被送到第一級,但是T3不導通,傳不到Q端,T4導通構成一個瑣存結構,維持Q的輸出不變;當clk由低變成高電平之后,T1關閉,新的數據不會再傳進來;同時T2導通,構成一個鎖存器維持數據QM不變;同時T3導通,QM傳輸到Q端;T4不導通,原先瑣存的數據不會對Q造成影響。因此整體實現的就是當clk上升沿來到時,數據D才會被更新到Q端。

經過上面的分析我們再來看建立時間與保持時間以及傳輸延時。

建立時間(tsetup):既數據D至少需要提到于clk上升沿多長時間到來,數據的采集才不會出錯。

從電路分析可知,在時鐘上升沿到來之前數據必須要被送到第一級電路的鎖存器里面,即M端。見下圖。

為什么呢?

因為如果上升沿到來時,數據沒有被送到M端,當時鐘上升沿一來,此時T2右端與M端的信號就會不一致;M端為舊數據,T2右端為新數據,那么舊數據可能會將新數據沖掉。

故在clk上升沿到來時,數據要被傳到M端,需經過I1,T1,I3, I2 。故在時鐘上升沿到來前 tsetup = tI1 + tT1 + tI3 + tI2時間數據D就必須送到寄存器輸入端,這個時間就是三個反相器加一個傳輸門的延時。

保持時間(thold):就是時鐘上升沿之后,數據D還需要維持多長時間不變,才不會對輸出Q造成影響。

從電路可以看到,當時鐘上升沿一來,T1就關閉了,就算關閉具有延遲,上升沿一到,數據立即就變化了,還是要經過一個反相器I1才能傳到T1,故不擔心數據會被送進去,因此保持時間可以為零。當然這是對于這個主從式結構的寄存器而言,其他的寄存器的保持時間不一定為零。

傳輸延時(tcq):既時鐘上升沿來了之后,數據還需要多久才能傳到Q端。

從電路分析,當時鐘上升沿來了之后,數據還需要經過T3,I6才能傳到Q端,故這個寄存器的傳輸延時tcq =tI6+tT3 。

這里只是以主從式上升沿觸發寄存器為例介紹深入介紹了一下為什么寄存器會有建立時間,保持時間要求,以及傳輸延時的概念。對于后面如果利用EDA工具做靜態時序分析時,這些參數都是由器件或者工藝庫直接給出的。

接下來我們會繼續探討時鐘同步電路的時序問題與時序優化。

-

CMOS

+關注

關注

58文章

6021瀏覽量

238825 -

寄存器

+關注

關注

31文章

5433瀏覽量

124417 -

反相器

+關注

關注

6文章

317瀏覽量

44258

原文標題:寄存器以及建立保持時間,傳輸延遲的介紹

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片設計進階之路—從CMOS到建立時間和保持時間

FPGA實戰演練邏輯篇51:建立時間和保持時間

保持時間與建立時間

數字 IC 筆試面試必考點(9)建立時間以及保持時間 精選資料分享

為什么觸發器要滿足建立時間和保持時間

建立時間和保持時間(setup time 和 hold time)

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

為什么寄存器會有建立時間,保持時間要求,以及傳輸延時的概念

為什么寄存器會有建立時間,保持時間要求,以及傳輸延時的概念

評論