在時序電路設(shè)計中,建立時間/保持時間可以說是出現(xiàn)頻率最高的幾個詞之一了,人們對其定義已經(jīng)耳熟能詳,對涉及其的計算(比如檢查時序是否正確,計算最大頻率等)網(wǎng)上也有很多。但拋開這些表面,建立時間/保持時間到底是如何產(chǎn)生的,了解的人卻不是很多。本篇文章就透過現(xiàn)象看本質(zhì),打開觸發(fā)器的“黑盒子”,來了解一下到底什么是建立時間/保持時間。

01

先來看一下建立時間/保持時間的定義:

建立時間(setup time):觸發(fā)器的時鐘信號上升沿到來以前,數(shù)據(jù)需要保持穩(wěn)定的時間。

保持時間(hold time):觸發(fā)器的時鐘信號上升沿到來之后,數(shù)據(jù)需要保持穩(wěn)定的時間。

值得注意的是,建立/保持時間的概念是針對觸發(fā)器的特性來說的。但是不僅觸發(fā)器有建立/保持時間,鎖存器也有,而且觸發(fā)器的建立/保持時間還是基于鎖存器的特性得來的。為此,先來了解一下鎖存器。

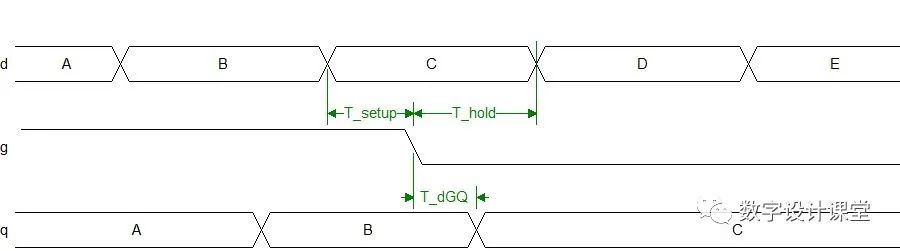

圖1 鎖存器的符號表示

典型的鎖存器如圖1所示,包括三個端口:數(shù)據(jù)輸入端D,使能輸入端G和數(shù)據(jù)輸出端Q。當使能端為高電平時,輸出Q隨輸入D變化;當使能端為低電平時,輸出保持不變。鎖存器的時序如圖2所示。

圖2 鎖存器的時序特性

在使能端由高電平向低電平變化過程中,為了使鎖存器正確鎖存住數(shù)據(jù),需要對輸入數(shù)據(jù)的時間加以約束,因此便有了鎖存器的建立時間和保持時間,即圖2中的T_setup 和T_hold 。鎖存器的這兩個時序特性定義跟觸發(fā)器很相似,不同的是在鎖存器上這兩個時序約束條件發(fā)生在使能端由高電平向低電平轉(zhuǎn)化時。圖2中的T_dGQ為使能端到輸出端的延時。

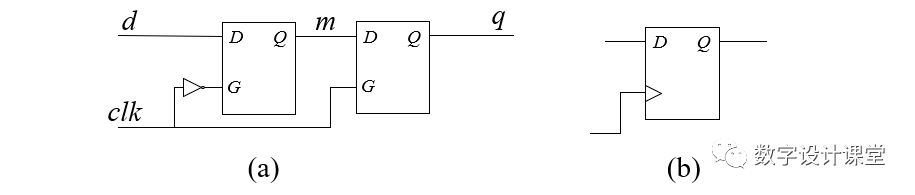

鎖存器在使能信號為高電平時相當于透明,而如何組合鎖存器,使其變成只在使能信號邊沿鎖存數(shù)據(jù)的觸發(fā)器呢?答案是兩個鎖存器串聯(lián)。如圖3(a)所示,串聯(lián)的前一個鎖存器使能端為低電平觸發(fā)(即反向使能),稱為主鎖存器,后一個鎖存器稱為從鎖存器。在clk為低電平時,使能主鎖存器,主鎖存器的輸出信號m隨輸入d變化,此時因為從鎖存器未被使能,所以輸出信號q無變化;在clk從低電平變?yōu)楦唠娖綍r,m采樣輸入信號d并且保持,與此同時從鎖存器打開,輸出端輸出被主鎖存器鎖存的信號值。觸發(fā)器的符號表示如圖3(b)。

圖3 (a)兩個鎖存器組成的觸發(fā)器 (b)觸發(fā)器符號表示

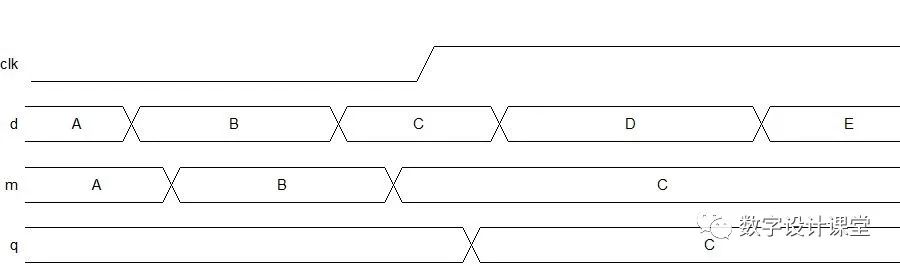

為了進一步了解主從鎖存器的工作原理,示例的波形圖如圖4所示。可以看到,當clk為低時,m跟隨d變化;當clk由低變高,主鎖存器鎖存輸入值,中間m停止變化,此時從鎖存器打開,經(jīng)過一段延遲后將中間信號送至輸出。

圖4 兩個鎖存器組成的觸發(fā)器時序波形

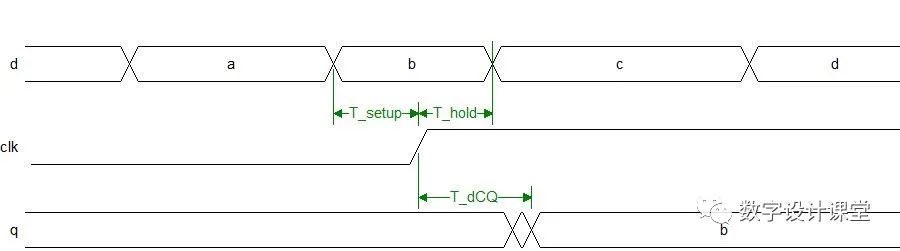

為了不引起混淆,圖4在重畫的波形圖上給出觸發(fā)器的時序特性表示。其中T_dCQ為觸發(fā)器從clk端到Q端的延遲。需要注意的是,在clk上升后到Q端穩(wěn)定以前,Q端可能會變化多次,T_dCQ 則是取從clk變化到穩(wěn)定輸出之間的延遲。

圖5 觸發(fā)器的時序特性表示

鎖存器的時序特性和觸發(fā)器的時序特性該如何對應呢?仔細一想就會得到答案:觸發(fā)器的建立時間和保持時間其實就是主鎖存器的建立時間和保持時間,而觸發(fā)器的clk到q端的延遲T_dCQ就是從鎖存器的延遲T_dGQ。

到這里我們已經(jīng)打開了觸發(fā)器的第一層“黑盒子”,但是建立時間和保持時間究竟是如何產(chǎn)生的呢?這就需要打開第二層“黑盒子”——觸發(fā)器的門電路表示。

02

構(gòu)成鎖存器的電路多種多樣,這里我們選擇使用傳輸門和三態(tài)門構(gòu)建的CMOS鎖存器,電路如圖6所示。

圖6 鎖存器電路

當G為高電平時,傳輸門Ug打開,信號從D端輸入,經(jīng)過Ug、U2、U4到達輸出端Q,此時三態(tài)反相器為關(guān)閉狀態(tài);當G端變?yōu)榈碗娖綍r,傳輸門關(guān)閉,U3打開,此時U2、U3構(gòu)成雙穩(wěn)態(tài)器件將輸入信號保持,輸出端Q也穩(wěn)定輸出雙穩(wěn)態(tài)器件保持的信號。

現(xiàn)在來探討鎖存器的建立時間和保持時間。在G為高電平時,輸入D變化后為了能輸出正確的值,存儲器——即雙穩(wěn)態(tài)器件必須存儲到正確的輸入值。這意味著要想使輸出正確,在G下降前輸入值必須經(jīng)過U2。由此得出建立時間

T_setup = Tg + T2

其中Tg和T2分別為傳輸門和反相器U2的延遲。

當G變?yōu)榈碗娖胶螅斎胫敌枰趥鬏旈T關(guān)閉之前保持不變,否則輸入值就會穿過傳輸門,從而無法鎖存正確的值。傳輸門的關(guān)閉信號需要經(jīng)過U1,所以得出保持時間

T_hold = T1

其中T1為反相器U1的延遲。

接下來算一下T_dGQ。G由高變低后,G的變化經(jīng)過反相器U1到達傳輸門Ug,使傳輸門關(guān)閉,輸入的信號再經(jīng)過Ug、U2、U4到達輸出端。所以

T_dGQ = T1 + Tg + T2 + T4

從輸入端到輸出端,信號經(jīng)過了Ug、U2、U4,所以輸入到輸出的延遲

T_dDQ = Tg + T2 + T4

因為在觸發(fā)器中T_dDQ意義不大,所以在此也不做過多贅述。

有了單個鎖存器的基礎(chǔ),接下來進行觸發(fā)器的探討也會變得容易很多。

03

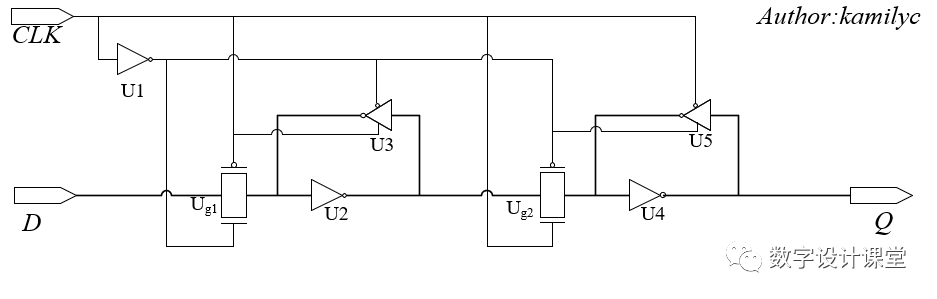

由第一段分析可知,觸發(fā)器是由兩個鎖存器串聯(lián)而組成的,由傳輸門和三態(tài)反相器構(gòu)成的觸發(fā)器如圖7所示:

圖7 觸發(fā)器電路

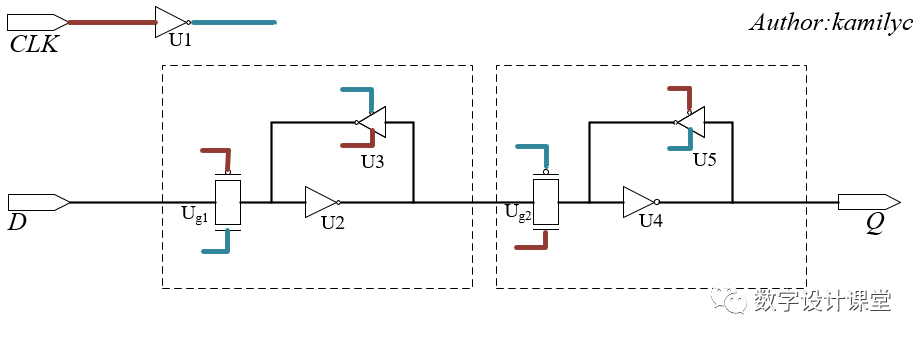

可以看到在觸發(fā)器電路中,Ug1、U2、U3構(gòu)成了主鎖存器,Ug2、U4、U5構(gòu)成了主鎖存器。為了更直觀的展示觸發(fā)器的原理,將圖7中的時鐘信號用彩色的連線代替,得到圖8:

圖8 觸發(fā)器的原理圖的直觀表示

在圖8中,主鎖存器和從鎖存器分別用虛線框出,紅色連線為clk信號,藍色連線為經(jīng)過反相器U1后的clk信號。

觸發(fā)器的建立時間和保持時間與主鎖存器的相同:

T_setup = Tg1 + T2

T_hold = T1

觸發(fā)器的clk到Q端延遲則為從鎖存器的延遲,分析方法與鎖存器的分析方法相同:

T_dCQ = T1 + Tg2 + T4

-

反相器

+關(guān)注

關(guān)注

6文章

315瀏覽量

44019 -

時序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

21868 -

鎖存器

+關(guān)注

關(guān)注

8文章

922瀏覽量

42089 -

門電路

+關(guān)注

關(guān)注

7文章

200瀏覽量

40582 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2031瀏覽量

61845

發(fā)布評論請先 登錄

靜態(tài)時序之建立時間和保持時間分析

芯片設(shè)計進階之路—從CMOS到建立時間和保持時間

FPGA時序分析-建立時間和保持時間裕量都是inf怎么解決呢?

淺析D觸發(fā)器的建立時間和保持時間物理含義

建立時間和保持時間討論

FPGA實戰(zhàn)演練邏輯篇51:建立時間和保持時間

保持時間與建立時間

數(shù)字 IC 筆試面試必考點(9)建立時間以及保持時間 精選資料分享

為什么觸發(fā)器要滿足建立時間和保持時間

SOC設(shè)計中的建立時間和保持時間

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

關(guān)于建立時間和保持時間的測量方法

到底什么是建立時間/保持時間?

到底什么是建立時間/保持時間?

評論