文章來源:學習那些事

原文作者:小陳婆婆

本文主要講述芯片制造中的對準技術。

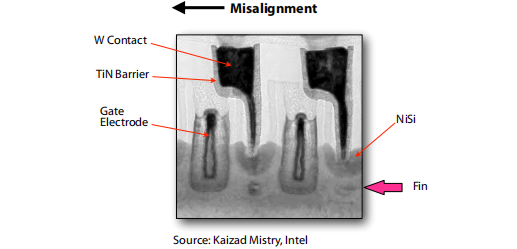

三維集成電路制造中,對準技術是確保多層芯片鍵合精度、實現高密度TSV與金屬凸點正確互聯的核心技術,直接影響芯片性能與集成密度,其高精度可避免互連失效或錯誤,并支持更小尺寸的TSV與凸點以節約面積。

主流量產采用“對準與鍵合分離”方案,先在專用設備完成高精度對準再轉移鍵合,有效規避溫度變化、硅片翹曲等因素干擾,同時通過分解鍵合前對準誤差與鍵合滑移誤差優化工藝,提升設備利用率。影響精度的關鍵因素包括鍵合方式(直接鍵合滑移小、精度高,高分子鍵合易滑移)、材料特性(CTE差異導致翹曲,臨時鍵合中玻璃載片翹曲控制是重點)及表面形貌等;對準方法分直接與間接:透明材料(如去襯底SOI器件層)可通過雙顯微鏡直接觀測參考點對準,不透明材料則需間接對準(先固定一層參考點再調整另一層,精度稍低)。

當前主流技術涵蓋晶圓級(紅外/光學透視)、倒裝芯片(光學系統定位)及自組裝對準,其中SOI的創新應用通過透明結構實現光刻級高精度對準,推動3D IC向更小、更快、更集成方向演進。

紅外對準

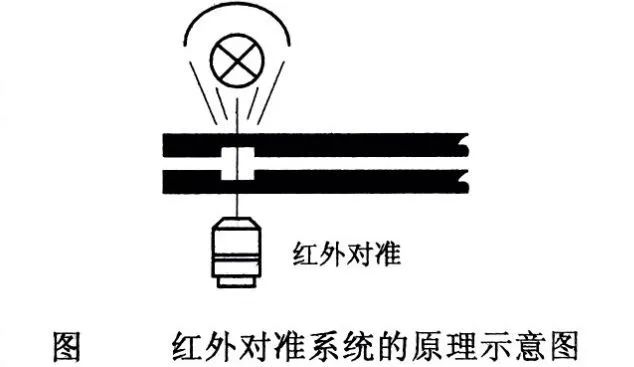

紅外對準技術作為三維集成電路鍵合工藝中的核心手段,憑借硅材料對近紅外光(1.1-1.3eV)的透明特性,通過1.2μm波長左右的紅外光源穿透硅片,實現上下層對準標記的精準定位,是早期鍵合對準的代表性技術。

其原理在于:紅外光從晶圓底部照射,經由CCD或紅外顯微鏡捕捉透射圖像,通過調整兩層硅片的相對位置完成對準,隨后直接鍵合,有效避免了分離式對準中溫度變化和硅片翹曲帶來的誤差。該技術設備結構簡單、調整靈活,且支持原位對準,但受材料限制顯著——硅氧化物(SiO?)、氮化物(Si?N?)及金屬互連層對紅外光的吸收與反射會干擾成像,需通過預留對準窗口或采用雙面拋光的高等級晶圓(厚度≤300μm)來優化透過率,同時需控制硅片電阻率(>0.01Ω·cm)以避免紅外吸收率過高。

精度方面,紅外對準的分辨率受波長、鏡頭放大倍數及機械系統控制精度影響,通常采用最短可用紅外波長以提升可視度,并通過減小兩層硅片間隙、將對準標記置于相對表面來降低偏差。近年來,推出的近紅外顯微鏡系統(如MIR400)進一步優化了光學設計,支持900-1700nm波段、0.8μm分辨率的透射成像,結合長工作距離物鏡(15mm)與高精度電動平臺(重復定位精度0.5μm),實現了鍵合過程的實時監控與閉環控制,顯著提升了工藝穩定性。

應用場景上,紅外對準主要適用于晶圓級鍵合(W2W),在芯片級倒裝(D2D)中因對準窗口尺寸大、互連布局干擾等問題應用受限,但通過絕緣體上硅(SOI)技術去除襯底后,器件層與玻璃輔助晶圓的透明化處理,可擴展其應用范圍。材料與工藝層面,除晶圓拋光外,新型紅外穿透塑料(如PC、PMMA)通過模具精度優化(表面粗糙度Ra<0.01μm)與注塑工藝改進,已實現90%以上的紅外透過率,有效減少了表面散射對成像的干擾;同時,鍵合工藝參數(如超聲功率110-120DAC、接觸力25-35gf)的優化,提升了金絲鍵合的拉力值與信號傳輸可靠性,進一步保障了紅外對準后的鍵合質量。

行業最新進展顯示,紅外對準技術正與機器視覺及AI深度融合,例如通過近紅外圖像的多光譜融合與深度學習算法,可自動識別復雜背景下的對準標記,降低人工干預需求;此外,中波紅外(MWIR)傳感器技術的突破(如非制冷量子點探測器、二維材料異質結),為未來更高精度的紅外對準設備提供了性能更優、成本更低的檢測組件,推動該技術向更微小尺寸TSV與更高密度3D集成方向發展。

光學對準

光學對準技術作為三維集成電路鍵合工藝中實現高精度定位的核心手段,憑借其抗干擾能力強、適配性廣及精度可控等優勢,已成為量產設備的主流對準方案,有效彌補了紅外對準在復雜材料環境下的性能局限。其核心原理在于通過可見光或特定波段光學系統直接觀測上下層硅片的對準標記,結合精密機械調整實現位置匹配,過程直觀且調整靈活。

早期代表性技術為背面對準方法,主要用于MEMS雙面光刻領域。該技術通過將兩層硅片面對背放置,使對準標記均朝向光學顯微鏡方向,利用間接位置調整完成對準,隨后轉移至鍵合機固定。其特點是對準標記朝向一致,但硅片物理方向相反,操作相對簡單,但精度受限于標記間接調整的誤差累積。

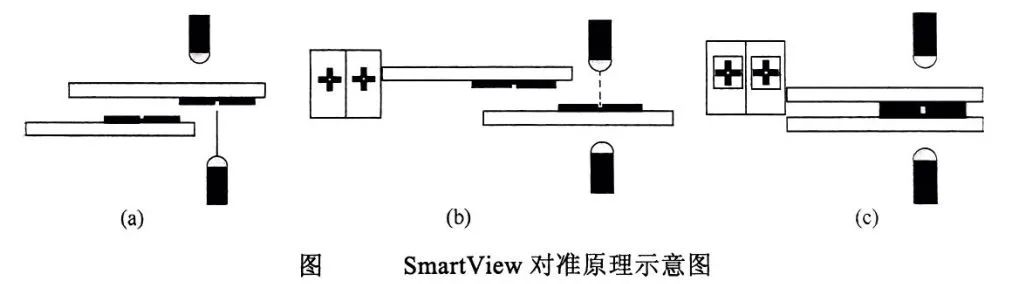

為進一步提升精度,推出SmartView技術,采用雙顯微鏡雙向觀測系統:先固定第一層硅片并記錄其物理位置,再通過上方顯微鏡捕捉第二層標記,計算兩層相對位置差異后調整,實現面對面放置的高精度對準。盡管設備復雜度增加,但標記間距縮小顯著提升了平移與旋轉誤差的控制能力,尤其適用于需要微米級調整的場景。

進一步突破開發片間對準(ISA)技術,通過分光鏡將光學系統伸入兩硅片間隙,同步觀測上下層標記并融合圖像,直接調整相對位置。該技術邏輯簡單、觀測直觀,且面對面標記設計大幅降低間隙影響,早期精度達±2μm,近年隨精密光學與機械控制技術升級(如真空環境輔助、壓膜阻尼優化),已實現深亞微米級精度,成為高精度鍵合的首選方案。

對準標記的設計是精度優化的關鍵,通常采用游標式與十字形結合結構:游標設計細化平移誤差判斷,長間距并列標記則通過增大基線距離抑制旋轉誤差。材料層面,低粗糙度雙面拋光晶圓(表面粗糙度Ra<0.5nm)與高透光率薄膜(如SiO?/Si?N?優化層)可減少光散射,提升標記成像清晰度;工藝上,動態閉環控制算法(如實時誤差反饋)與AI圖像識別技術(如深度學習標記定位)的集成,進一步降低了人為干預需求,提高了生產效率。

目前,SmartView NT系統通過多光譜融合與亞像素級圖像處理,將對準精度提升至0.1μm以下;Suss的ISA技術結合真空環境與低振動平臺,有效抑制了接觸過程中的漂移現象;同時,新型納米級對準標記(如200nm線寬圖形)與超薄晶圓(厚度<50μm)的應用,正推動光學對準向更微小尺寸TSV與更高密度3D集成方向發展,為先進封裝技術的持續演進提供關鍵支撐。

倒裝芯片

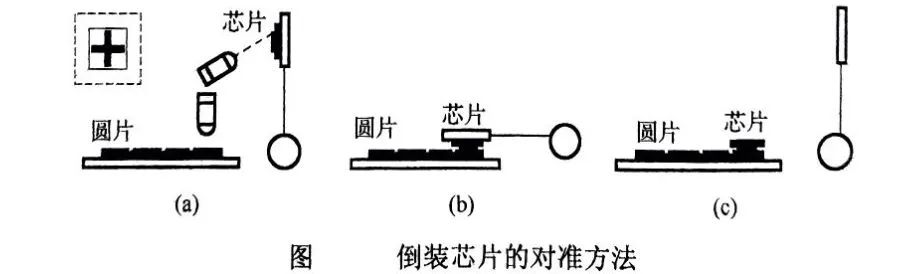

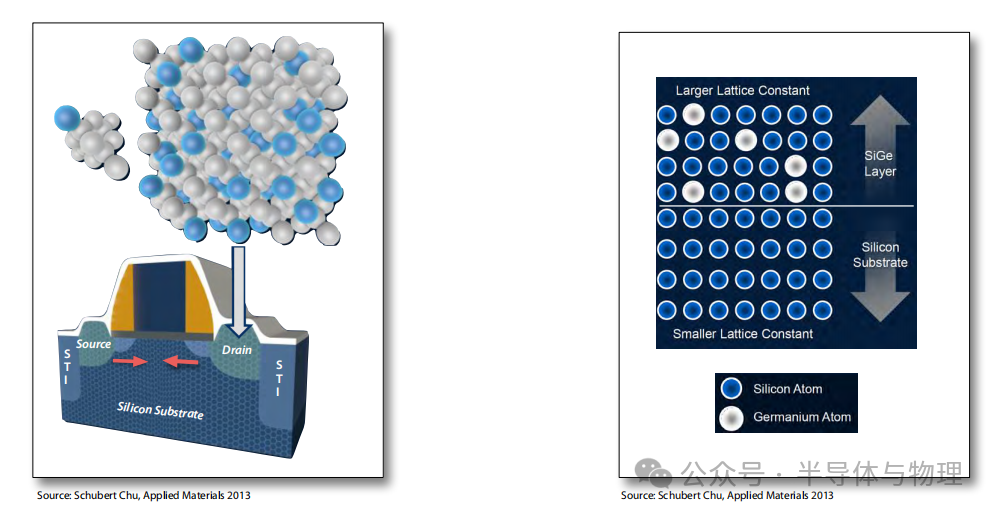

倒裝芯片技術作為三維集成電路中實現芯片級互連的核心手段,憑借其直接金屬凸點鍵合與高密度集成優勢,已成為D2D(芯片到芯片)與D2W(芯片到晶圓)對準的關鍵工藝。

其基本流程為:下層芯片固定于高精度工作臺,上層芯片通過機械臂吸附并調整姿態,光學成像系統同步捕捉上下層對準標記(如十字形或游標式圖形),通過亞微米級運動平臺調整位置,隨后施加可控壓力(利用杠桿原理加載重物)并加熱實現金屬凸點熔融鍵合。傳統設備的對準精度受限于機械調整速度與熱壓工藝穩定性,通常在1-20μm范圍內,且精度與生產效率呈負相關——更高精度需延長對準時間,導致單點鍵合周期增加。

早期倒裝芯片設備以封裝應用為主,強調生產效率而非極致精度,其集成化設計(對準與鍵合模塊一體)雖簡化流程,但在三維集成中暴露出局限性:串行操作模式導致多層鍵合效率低下,且多次熱循環易引發熱應力累積,影響器件可靠性。此外,傳統擺臂式結構在D2D對準中難以兼顧大范圍調整與微米級精度,限制了其在高密度3D IC中的應用。

材料與工藝層面,新型低熔點金屬合金(如Sn-Ag-Cu無鉛焊料)與納米級凸點(直徑<10μm)的應用,進一步降低了鍵合溫度與壓力需求;而AI驅動的圖像識別系統(如深度學習對準標記定位)與數字孿生技術,則通過實時誤差預測與補償,減少了人工干預,提升了良率。行業數據顯示,采用高精度倒裝芯片設備的3D IC產線,其TSV密度已突破105/cm2,互連電阻降低30%以上,為先進封裝(如CoWoS、HBM)的持續演進提供了關鍵支撐。

芯片自組裝對準

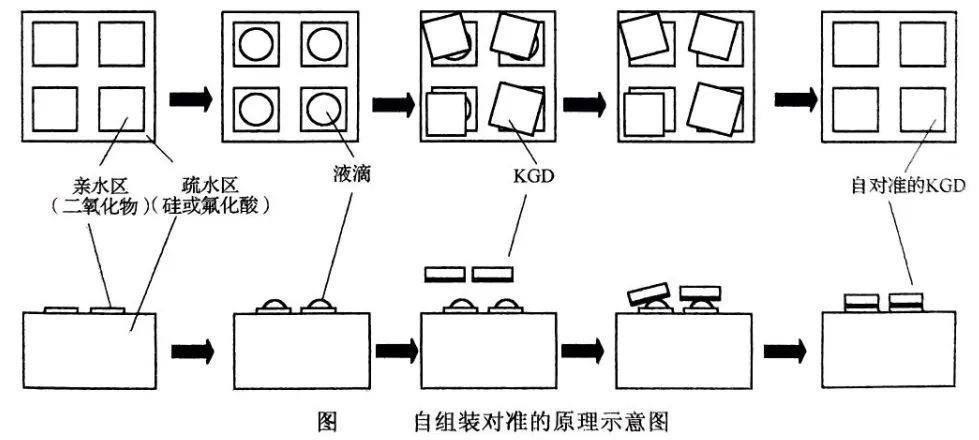

芯片自組裝對準技術作為三維集成電路制造中的創新方案,憑借其獨特的流體動力學機制與高效率特性,正在小尺寸器件集成領域展現顯著優勢。

該技術核心原理在于利用液體表面張力驅動的物理特性實現精準定位:通過在基底表面構建親水與疏水區域的差異(如SiO?沉積結合光刻刻蝕工藝),配合低熔點焊料、環氧樹脂或丙烯酸酯等流體介質,使液滴僅停留在預設親水區,隨后將待對準芯片放置于液滴表面,借助表面張力的自動調整功能完成位置與角度的校正。

自組裝技術的突出優勢在于其超高速與高精度特性——單芯片對準可在0.06秒內完成,精度達±1μm級,且支持并行處理模式,百顆芯片同步對準的時間與單顆芯片無顯著差異,極大提升了生產效率。相較于傳統倒裝芯片技術,其非接觸式調整機制避免了機械磨損,同時流體介質的緩沖作用降低了熱應力風險,有利于提升垂直互連密度與器件可靠性。然而,該技術也存在局限性:需對芯片表面進行親水處理(如涂覆特定材料),增加了工藝復雜度;液體環境可能對含MEMS懸空結構或傳感器的芯片造成粘連風險;多層堆疊時,已鍵合層表面的親疏水區域二次處理難度較高;正方形芯片還需初始方向預對準以避免旋轉偏差。

模版對準

模板對準技術作為三維集成電路制造中的創新物理結構對準方案,由美國倫斯勒理工學院與清華大學聯合開發,憑借其高效率、強適應性及工藝簡化優勢,在D2W(芯片到晶圓)鍵合領域展現出獨特價值。該技術核心在于通過底層晶圓深槽與上層芯片垂直臺階的機械接觸實現精確定位,規避了傳統光學對準對復雜成像系統的依賴,同時支持鍵合設備內原位對準,有效避免了轉移過程中的位置偏移風險。

其工藝流程分為三步:首先在底層晶圓表面旋涂低應力苯并環丁烯(BCB)有機聚合物,通過等離子體干法刻蝕構建各向異性深槽結構,頂角與側壁精確定義芯片的x/y方向坐標。此步驟需優化刻蝕參數(如功率、壓強、氣體成分比),以最小化橫向刻蝕導致的定位偏差,確保深槽底部清潔無殘留;第二步在上層芯片邊緣刻蝕垂直臺階,采用干法刻蝕替代傳統砂輪切割以提升側壁平整度(表面粗糙度Ra<10nm),臺階高度需略大于深槽深度以避免懸空接觸;最后通過倒裝設備將芯片翻轉裝載至深槽內,借助離心力(高速旋轉晶圓)使臺階側壁與深槽側壁緊密貼合,完成亞微米級對準。

該技術優勢顯著:物理接觸式定位不受光學系統分辨率限制,可在鍵合腔體內直接完成對準-鍵合流程,支持D2D、D2W及W2W多種鍵合模式,并兼容MEMS與傳感器器件(避免液體環境導致的結構粘連)。然而,其局限性在于需對芯片襯底進行刻蝕,犧牲部分面積提升成本,且多層堆疊時上層深槽的參照標記易受下層工藝影響,導致對準精度逐層衰減(通常3層以上精度下降超30%)。

-

集成電路

+關注

關注

5430文章

12139瀏覽量

368907 -

晶圓

+關注

關注

53文章

5181瀏覽量

130087 -

芯片制造

+關注

關注

11文章

695瀏覽量

29810

原文標題:芯片制造——對準技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Techwiz LCD:基板未對準分析

Techwiz LCD 3D應用:基板未對準分析

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

芯片制造全流程及詳解

無線鏈路部署中如何改善天線對準?

高精度光電傳感器在芯片定位及對準檢測方面的應用

自對準硅化物工藝詳解

芯片制造中的鍵合技術詳解

芯片制造中的對準技術詳解

芯片制造中的對準技術詳解

評論