文章來源:學習那些事

原文作者:小陳婆婆

本文主要講述芯片制造中的鍵合技術。

鍵合技術

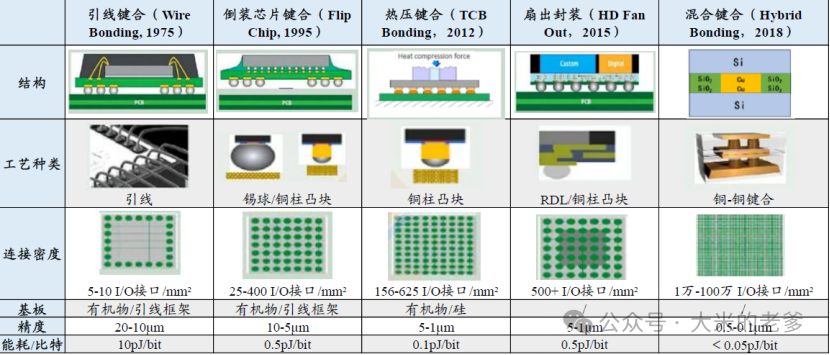

鍵合技術是通過溫度、壓力等外部條件調控材料表面分子間作用力或化學鍵,實現不同材料(如硅-硅、硅-玻璃)原子級結合的核心工藝,起源于MEMS領域并隨SOI制造、三維集成需求發展,涵蓋直接鍵合(如SiO?融合)與中間層鍵合(如高分子、金屬)兩類,其溫度控制、對準精度等參數直接影響芯片堆疊、光電集成等應用的性能與可靠性,本質是通過突破納米級原子間距實現微觀到宏觀的穩固連接。

本文分述如下:

SiO?融合鍵合

金屬鍵合

高分子鍵合

SiO?融合鍵合

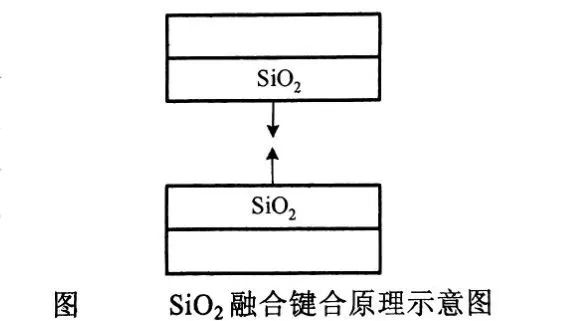

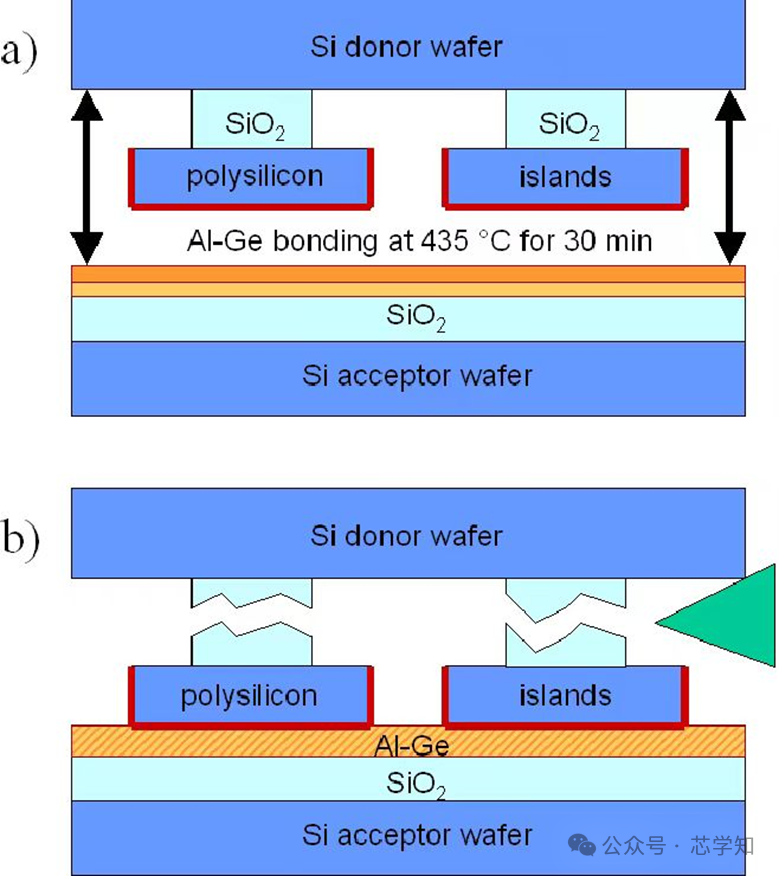

SiO?融合鍵合作為三維集成電路制造中的關鍵技術之一,通過直接利用SiO?介質層間的分子作用力實現無中間層的高精度鍵合,其技術本質源于親水性SiO?表面在室溫接觸時羥基(-OH)的氫鍵相互作用,通過水分子縮合形成初始鍵合界面,再經高溫退火促進Si-O-Si共價鍵重構以提升鍵合強度。

該工藝最早由IBM應用于SOI圓片面對背鍵合,通過去除SOI襯底層將埋氧層直接鍵合至另一圓片的SiO?介質層,現已成為三維堆疊芯片制造的核心工藝。其鍵合質量高度依賴表面處理工藝,包括化學機械拋光(CMP)實現的亞納米級表面粗糙度控制、超潔凈化學清洗以及預致密化處理,以消除鍵合空洞缺陷。

盡管700℃以上退火可顯著增強Si-O-Si共價鍵形成,但受限于三維集成電路中已成型器件的熱預算,實際工藝中退火溫度通常控制在400℃以下,此時鍵合強度仍能滿足集成需求。該技術的核心優勢在于室溫預鍵合階段即可通過分子間作用力鎖定對準精度,有效避免傳統金屬熱壓鍵合因熱膨脹系數(CTE)失配導致的滑移問題,實測300℃退火4小時后對準偏差小于0.4μm,配合硅片變形補償圖形技術可實現優于180nm的對準精度。

針對無金屬互連的挑戰,行業已發展出混合鍵合解決方案,如Ziptronix公司授權Tezzaron使用的DBI(Direct Bond Interconnect)技術,通過埋置Cu TSV或鍵合凸點并經CMP平坦化,實現SiO?介質層與金屬互連的同步鍵合,盡管該工藝需精確控制金屬凸點高度且鍵合溫度提升至400℃,但已成為當前三維集成領域最具競爭力的互連方案之一。

近期研究聚焦于低溫鍵合強化技術,通過優化SiO?層應力控制及新型表面活化工藝,進一步降低熱處理需求,推動SiO?融合鍵合在先進封裝領域的規模化應用。

金屬鍵合

金屬鍵合作為三維集成電路中實現電學互連與機械固定的核心技術,貫穿于芯片堆疊的全流程,其核心在于通過金屬材料的物理或化學作用建立穩定連接。

該工藝主要分為金屬熱壓鍵合與金屬共晶鍵合兩大類,二者在機理、材料選擇及工藝控制上存在顯著差異,共同支撐著三維集成的可靠性需求。

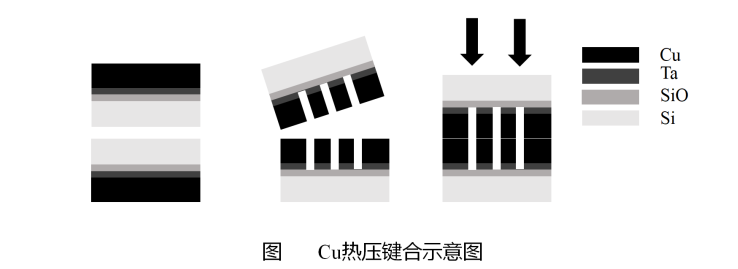

金屬熱壓鍵合以同種金屬(如Cu-Cu、W-W、Au-Au)為對象,通過高溫高壓促使金屬原子擴散并重構晶粒結構,最終形成一體化的鍵合界面。以Cu熱壓鍵合為例,其工藝流程涵蓋圖形化、金屬沉積、平坦化及熱壓鍵合等關鍵步驟:首先在圓片表面圖形化出鍵合窗口,通過PVD或電鍍沉積Cu凸點(厚度<2μm時采用PVD,>2μm時結合PVD種子層與電鍍工藝),隨后經CMP處理去除多余金屬并平整化表面;最終在真空環境下施加300~400℃溫度與一定壓力,促使Cu原子擴散及晶粒再生長,形成無界面的單層Cu結構。該工藝的鍵合強度可達3.2J/m2,界面電阻極低,但需嚴格控制表面污染與氧化物,否則易在鍵合界面形成空洞,引發電遷移或剝離失效。為提升可靠性,常通過輔助鍵合區(僅用于增強機械強度)彌補電互連凸點面積不足的問題。

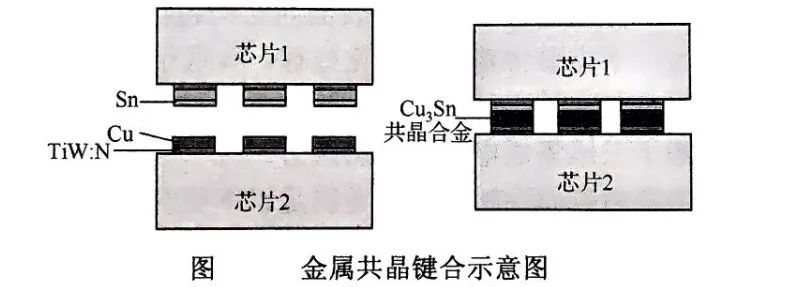

金屬共晶鍵合則依托不同金屬間的共晶反應,利用低溫相變實現連接,其典型代表為Cu-Sn-Cu體系的SLID(固液間擴散)工藝。該工藝通過加熱使低熔點金屬(如Sn)熔化為液相,與高熔點金屬(如Cu)擴散形成金屬間化合物(如Cu?Sn?),其熔點高于鍵合溫度,從而避免后續工藝中的熱失效。反應過程分兩階段:液相Sn與Cu快速擴散形成初始化合物層,隨后Cu通過化合物層緩慢擴散,最終液相Sn被完全消耗并固化。工藝中需控制低熔點金屬厚度(通常1~5μm),防止過度消耗高熔點金屬導致黏附性下降,同時需在4%氫氣與惰性氣體混合環境中施加低壓(<大氣壓),保證界面充分接觸。相較于熱壓鍵合,共晶鍵合的鍵合溫度更低(通常<300℃),更適配多層堆疊中下層金屬的熱預算限制,但需精確控制反應進程以避免空洞或裂縫。

實際應用中,金屬鍵合常結合TSV(硅通孔)或RDL(再布線層)實現互連:TSV直接鍵合利用電鍍凸出的Cu柱實現短路徑連接,成本低且電阻低,但熱壓過程中可能因Cu變形導致TSV退縮;RDL微凸點則通過額外布線層提高布線靈活性,尤其適用于非對齊TSV的跨層連接,可靠性更高。

近年來,行業聚焦于低溫化與高精度化發展,例如納米級Cu凸點技術通過減小特征尺寸降低熱壓變形風險,混合鍵合技術(如DBI)將金屬鍵合與SiO?融合鍵合結合,進一步解決了互連與對準精度的矛盾,成為先進封裝領域的熱點方向。

高分子鍵合

高分子鍵合作為三維集成電路中實現芯片堆疊的關鍵技術之一,依托高分子材料的黏附與內聚特性構建機械連接,其工藝特性與材料選擇深度影響集成系統的性能與可靠性。該技術的核心優勢在于低溫(通常<200℃)、低壓(<1MPa)的工藝條件,顯著降低對已成型器件的熱應力損傷,與CMOS工藝高度兼容;同時,高分子層可有效填補硅片表面微米級起伏(粗糙度<50nm),無需額外平坦化處理,大幅簡化前道工藝。然而,其對準精度(通常>1μm)受限于材料軟化引發的層間滑移,且低熱導率(<0.5W/m·K)易導致堆疊層間熱積累,成為制約高性能計算芯片散熱的瓶頸。

當前主流高分子鍵合材料聚焦于熱固性樹脂體系,其中苯并環丁烯(BCB)與聚酰亞胺(PI)憑借優異的熱穩定性(玻璃化轉變溫度>350℃)、低吸濕性(<1%)及良好的黏附性占據主導地位,而硅氧烷基光敏材料SINR則通過光刻兼容性簡化了圖形化流程。材料選擇需綜合考量玻璃化轉變溫度與鍵合溫度的匹配性、內聚強度(>50MPa)及氣體釋放量(<1ppm),以確保鍵合界面無空洞缺陷。工藝實施中,液態前驅體通過旋涂(均勻性<5%)或噴涂(均勻性<7.5%)形成微米級薄膜(厚度1-10μm),經低溫固化(150-250℃)后,通過干法刻蝕或光敏曝光實現金屬互連區域的圖形化;固態高分子薄膜因無需溶劑揮發,近年來在均勻性控制(厚度偏差<2%)與工藝穩定性方面展現出更大潛力。

對準誤差控制是高分子鍵合的核心挑戰,其來源包括鍵合前初始偏差、上下層CTE失配(<2ppm/℃)引發的熱膨脹差異,以及鍵合過程中高分子軟化導致的層間滑移(5-10μm)。為緩解滑移效應,行業正探索納米級表面紋理化技術,通過增加機械互鎖提升層間摩擦力;同時,混合鍵合方案(如高分子-金屬復合鍵合)通過局部引入金屬凸點,在保證整體柔性的同時提升關鍵區域的對準精度(<500nm)。最新研究還聚焦于高熱導率高分子材料開發,例如氮化硼納米管填充的復合樹脂,其熱導率已突破2W/m·K,較傳統材料提升300%。

此外,AI驅動的工藝參數優化系統通過實時監測涂覆厚度與固化曲線,將鍵合良率提升至99.5%以上,推動高分子鍵合在先進封裝領域的規模化應用。

-

集成電路

+關注

關注

5430文章

12139瀏覽量

368916 -

芯片制造

+關注

關注

11文章

695瀏覽量

29812 -

鍵合

+關注

關注

0文章

83瀏覽量

8121

原文標題:芯片制造——鍵合技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片制造中的鍵合技術詳解

芯片制造中的鍵合技術詳解

評論