南京屹立芯創半導體科技有限公司

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

在摩爾定律逐漸放緩的背景下,Chiplet(小芯片)技術和3D封裝成為半導體行業突破性能與集成度瓶頸的關鍵路徑。然而,隨著芯片集成度的提高,氣泡缺陷成為影響封裝良率的核心挑戰之一。南京屹立芯創半導體科技有限公司(ELEAD TECH)憑借其晶圓級真空貼壓膜系統和多領域除泡系統,為先進封裝提供了關鍵解決方案,助力Chiplet與3D封裝技術實現更高性能與可靠性。

1. Chiplet技術:模塊化設計推動芯片創新

Chiplet技術將傳統SoC(系統級芯片)拆解為多個獨立功能模塊(如計算單元、存儲、I/O接口),通過先進封裝技術集成,類似“半導體樂高”。其優勢包括:

?靈活性:不同工藝節點的Chiplet可混合集成,例如CPU采用5nm工藝,而模擬電路采用成熟制程,降低成本。

?高性能:AMD的EPYC處理器采用Chiplet架構,通過3D堆疊實現更高帶寬和能效。

?良率優化:單個Chiplet良率更高,減少大尺寸單芯片的制造缺陷。

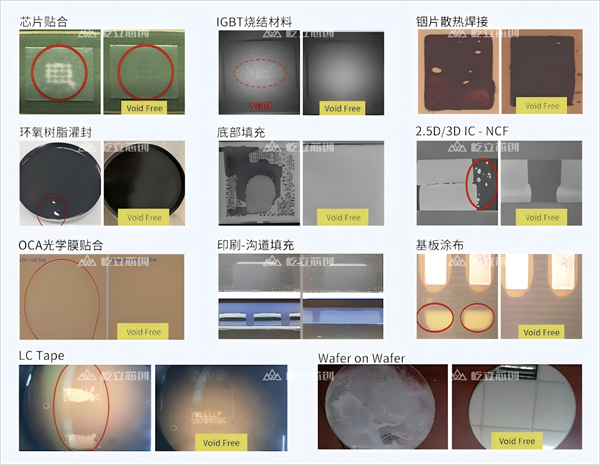

然而,Chiplet集成面臨氣泡殘留問題,尤其是在底部填膠(Underfill)、芯片貼合(Die Attach)等工藝中,氣泡會導致散熱不良、機械應力集中,甚至電路失效。

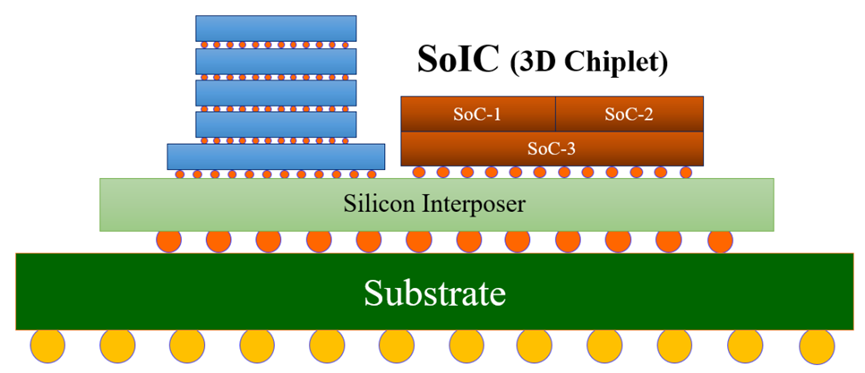

2. 3D封裝:垂直堆疊突破性能極限

3D封裝通過硅通孔(TSV)、混合鍵合(Hybrid Bonding)等技術,將Chiplet在垂直方向堆疊,顯著提升互連密度:

?HBM(高帶寬存儲器):通過TSV實現存儲與邏輯芯片的3D集成,帶寬可達819GB/s,延遲降低80%。

?異構集成:如NVIDIA Grace Hopper超級芯片,整合CPU與GPU裸片,優化AI計算效率。

但3D堆疊加劇了氣泡問題,尤其是在高深寬比(>1:10)的TSV填孔和RDL(再布線層)工藝中,傳統滾輪壓膜技術難以避免氣泡殘留。

3. 屹立芯創的解決方案:突破氣泡瓶頸

屹立芯創專注于半導體先進封裝中的氣泡消除,其核心技術包括熱流控制和氣壓調節,主要產品如下:

(1)晶圓級真空貼壓膜系統(WVLA/WVLM/WVLS)

?真空下貼膜+軟墊氣囊壓合:區別于傳統滾輪壓膜,采用真空環境預鋪設干膜,再通過彈性氣囊震蕩壓合,避免氣泡殘留,適用于凹凸晶圓表面(如Cu Pillar Bump)。

?高深寬比填覆:支持1:20 TSV填孔,廣泛應用于Flip Chip、Fan-out、3D-IC等制程。

?智能自動化:兼容8"/12"晶圓,集成自動切割系統,提升生產效率。

晶圓級真空貼壓膜系統

晶圓級真空貼壓膜系統

(2)多領域除泡系統

?真空壓力交互切換:針對底部填膠、環氧樹脂灌封等工藝,通過多段真空-壓力循環消除氣泡。

?銦片散熱方案:結合銦金屬的高導熱性,優化GPU/CPU封裝散熱,減少高溫導致的氣泡膨脹。

真空壓力除泡系統

真空壓力除泡系統

4. 行業應用與未來趨勢

屹立芯創的技術已成功應用于:

?AI/HPC芯片:如AMD MI300采用3D Chiplet集成,屹立芯創設備保障TSV填孔良率。

?車用電子:自動駕駛芯片需要高可靠性封裝,除泡技術提升長期穩定性。

?5G/物聯網:射頻模塊的異構集成依賴高精度貼膜與氣泡控制。

未來,隨著玻璃通孔(TGV)、混合鍵合等技術的發展,屹立芯創的循環換熱板專利技術(CN220062682U)將進一步優化3D封裝的熱管理能力。

Chiplet與3D封裝正推動半導體行業進入“集成創新”時代,而氣泡控制是確保良率的關鍵。屹立芯創憑借真空貼壓膜系統和智能除泡技術,成為全球除泡品類的領導者,為后摩爾時代的芯片性能突破提供核心支撐。未來,隨著標準化和跨行業協作的深化,Chiplet與3D封裝將在AI、自動駕駛、高性能計算等領域持續釋放潛力。

審核編輯 黃宇

-

封裝

+關注

關注

128文章

8731瀏覽量

145696 -

chiplet

+關注

關注

6文章

460瀏覽量

13025

發布評論請先 登錄

屹立芯創半導體除泡技術:提升先進封裝良率的關鍵解決方案

芯片3D堆疊封裝:開啟高性能封裝新時代!

對話郝沁汾:牽頭制定中國與IEEE Chiplet技術標準,終極目標“讓天下沒有難設計的芯片”

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

評論