面向高性能計算機、人工智能、無人系統(tǒng)對電子芯片高性能、高集成度的需求,以 2.5D、3D 集成技術為代表的先進封裝集成技術,不僅打破了當前集成芯片良率降低、成本驟升的困境,也是實現多種類型、多種材質、多種功能芯粒集成的重要手段。2.5D/3D 集成技術正快速發(fā)展,集成方案與集成技術日新月異。

本期借助771所王根旺博士等人關于“多芯粒 2.5D/3D 集成技術研究與應用現狀”綜述,分享多芯粒2.5D/3D集成技術研究現狀。下期將分享多芯粒2.5D/3D集成技術應用現狀與發(fā)展趨勢。

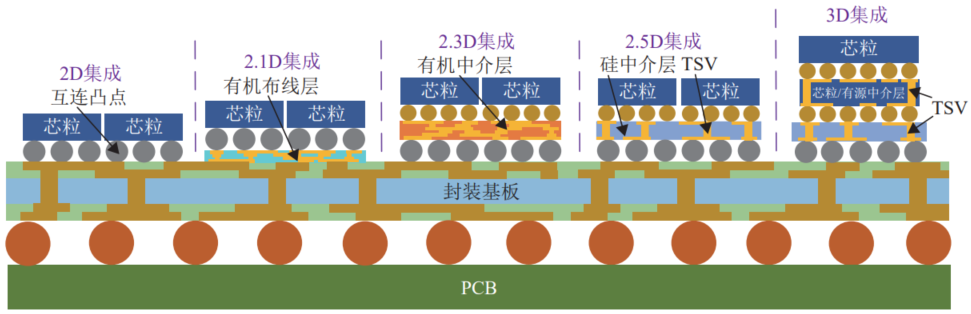

按照芯粒間電學互連的空間維度,多芯粒集成可分為 2D、2.1D、2.3D、2.5D、3D 集成技術,如下圖所示。2D集成是將多個芯粒焊接至封裝基板上,利用封裝基板上的電路實現芯粒之間水平方向上的電學互連。2.1D集成則是在芯粒與封裝基板之間多了RDL層。該層具有密度相對較高的互連線,并可嵌入硅基轉接結構以滿足高密度互連與較好的信號傳輸能力的需求。2.3D與 2.5D 技術則在芯粒與封裝基底之間加入一層無源的中介層(interposer,或稱轉接板、轉接基板等)。前者采用有機中介層,后者則是是使用基于TSV的硅中介層。無源中介層的主要功能是實現多個芯粒在水平方向的高密度互連以及芯粒與封裝基板在垂直方向上的互連。3D封裝技術則是利用有源的 TSV 中介層,或直接在芯粒上制備 TSV、互連微凸點與 RDL等結構,通過等回流焊接、熱壓焊接、鍵合連接等方式實現有源芯粒在垂直方向上的堆疊集成。另外,隨著異質異構芯片集成的需求的出現,2.5D、3D集成已不再局限于TSV 技術,基于玻璃、陶瓷等材料的集成技術也在不斷發(fā)展。在一些粗略分類中,2.1D、2.3D、2.5D 技術也被統(tǒng)稱為 2.5D 技術。

(1)2.5D 封裝集成技術

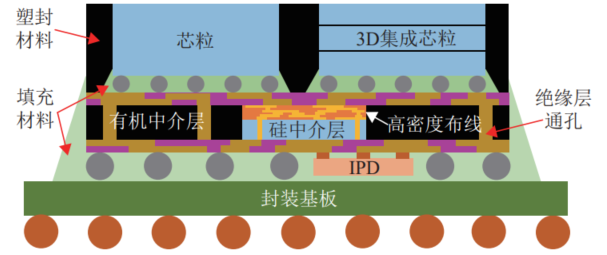

2.5D 封裝集成技術的RDL、有機中介層、TSV 中介層上均可制備密度較高、性能優(yōu)異的互連線,因此可以實現不同類型、不同制程的芯粒在水平方向上的高密度集成,不僅提高了集成芯片工藝良率,降低了集成芯片成本與能耗,也是實現多種功能芯粒集成的重要手段。目前,2.5D技術的典型代表有英特爾的嵌入式多芯片互連橋(EMIB)技術、臺積電的 CoWoS技術(下圖為 CoWoS-L結構)、三星的 I-Cube 等。

(2)3D 封裝集成技術

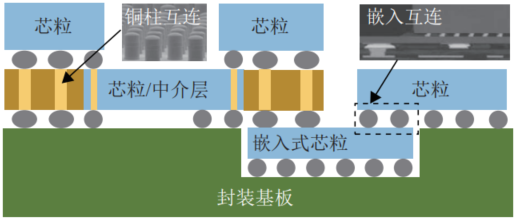

在面臨 2.5D 中介層尺寸增大、信號傳輸能力提高存在瓶頸時,能夠在垂直方向進行芯粒堆疊集成的 3D 封裝集成技術成為了進一步提高集成密度的重要手段。3D集成的關鍵是需要在有源芯粒或中介層上制造互連通孔,然后對芯粒進行堆疊與垂直電互連。目前,最先進的3D集成技術有英特爾的 Foveros、臺積電的 SoIC、AMD 的 3D V-chache、三星的 X-Cube 等。

目前,Foveros的互連節(jié)距可到 36-50μm,有望實現較高密度的集成,同時集成芯片具有較好的可靠性與信號傳輸能力。然而,TSV的大量使用會導致傳輸損耗增加、帶寬減小,互連凸點的尺寸難以繼續(xù)縮小也限制了集成密度的提高。因此,英特爾提出了Foveros Omni與 Foveros Direct技術。Foveros Omni采用一種全方向層間互連技術(ODI),如下圖所示。

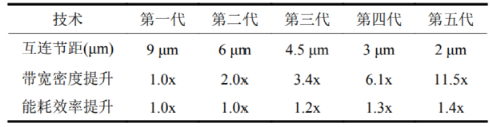

臺積電的 SoIC 技術也采用 TSV、HB等技術,以實現 10 μm 以下互連間距的高密度 3D 集成,并具有較高的帶寬、較低的功耗以及優(yōu)異的電源與信號完整性。研究表明,與其他封裝技術相比,SoIC可以將互連密度提高16倍,帶寬密度提高 191 倍,能耗降低 95 %。為進一步提高互連密度,第四代SoIC技術的互連節(jié)距可以小至3 μm,第五代技術有望減小至2μm。SoIC 技術關鍵指標的提升如下表所示。另外,臺積電也提出了更高互連密度的 SoIC-UHD技術,有望將互連節(jié)距降低至 0.9μm。

(3)多基材集成技術

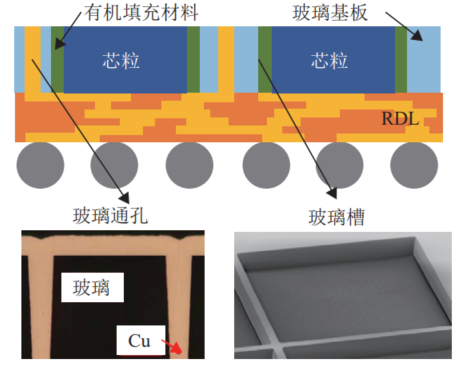

在 2.5D、3D 集成技術不斷發(fā)展的同時,硅基集成技術在材料豐富程度、工藝成本、功能多樣性等方面的先天短板也日益明顯。玻璃、陶瓷等材料成為了進一步豐富封裝結構、實現多功能芯片集成的關鍵。佐治亞理工學院提出了采用玻璃中介層可有效減小信號傳輸損耗、降低成本,同時通過調控玻璃的熱膨脹系數等特性可以解決硅芯粒與基板之間直接互連的可靠性問題,降低封裝成本。下圖為LPKF公司激光誘導刻蝕技術加工的小尺寸TGV、大尺寸填埋槽以及多種圖形的玻璃刻蝕。

陶瓷材料具有耐高溫、耐腐蝕、氣密性好、成本低等特點,是封裝技術中必不可少的關鍵材料。由于陶瓷材料具有可調的膨脹系數,因此陶瓷材料多用于封裝基板中,以提高芯片、封裝基板、PCB 的整體可靠性。另一方面,隨著高性能、一體化集成芯片的需求不多增加,散熱問題成為了產品可靠性的關鍵。高導熱率的陶瓷材料為高性能散熱提供了技術手段。然而,受限于陶瓷通孔(through ceramic via,TCV)制備精度、再布線密度等,陶瓷基板難以實現芯粒間的高密度互連,在 2.5D、3D 集成中的應用較為局限。直徑100μm 以下的 TCV制備成為未來陶瓷基 2.5D、3D 集成的關鍵難題。

-

芯片

+關注

關注

459文章

52267瀏覽量

437260 -

集成技術

+關注

關注

0文章

26瀏覽量

11051 -

芯粒

+關注

關注

0文章

63瀏覽量

252

原文標題:多芯粒2.5D/3D 集成技術研究現狀

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

顯示體驗升級:2.5D GPU技術逐漸成為標配,3D GPU加碼可穿戴

新型2.5D和3D封裝技術的挑戰(zhàn)

異構集成基礎:基于工業(yè)的2.5D/3D尋徑和協(xié)同設計方法

2.5D/3D芯片-封裝-系統(tǒng)協(xié)同仿真技術研究

分享一下小芯片集成的2.5D/3D IC封裝技術

3D封裝與2.5D封裝比較

3D封裝結構與2.5D封裝有何不同?3D IC封裝主流產品介紹

智原推出2.5D/3D先進封裝服務, 無縫整合小芯片

2.5D和3D封裝的差異和應用

探秘2.5D與3D封裝技術:未來電子系統(tǒng)的新篇章!

2.5D/3D封裝技術升級,拉高AI芯片性能天花板

技術資訊 | 2.5D 與 3D 封裝

多芯粒2.5D/3D集成技術研究現狀

多芯粒2.5D/3D集成技術研究現狀

評論