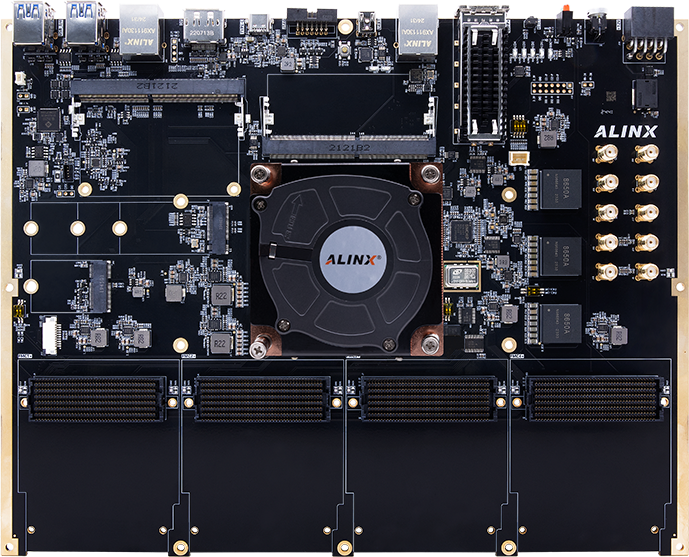

璞致(上海)電子科技有限公司深耕高端 FPGA 領域十余年,推出的 PZ-VU13P-KFB 開發板,以 Xilinx Virtex UltraScale+ XCVU13P 為核心,構建 “超大規模邏輯資源 + 超高速接口集群 + 工業級可靠性” 的高端開發平臺。該產品集成 3780K 邏輯單元、12288 個 DSP Slices 及 4 路 100G QSFP28 光接口,專為超高速信號處理、100G 光通信、多通道雷達等尖端場景設計,為工程師提供從算法驗證到量產落地的全流程支持,重新定義高端 FPGA 開發板的性能邊界。

一、功能賣點

強大的FPGA架構:基于領先的Xilinx Virtex UltraScale+架構,PZ-VU13P-KFB提供高達13萬個邏輯單元和大量DSP切片,確保高性能信號處理,適合復雜算法實現。

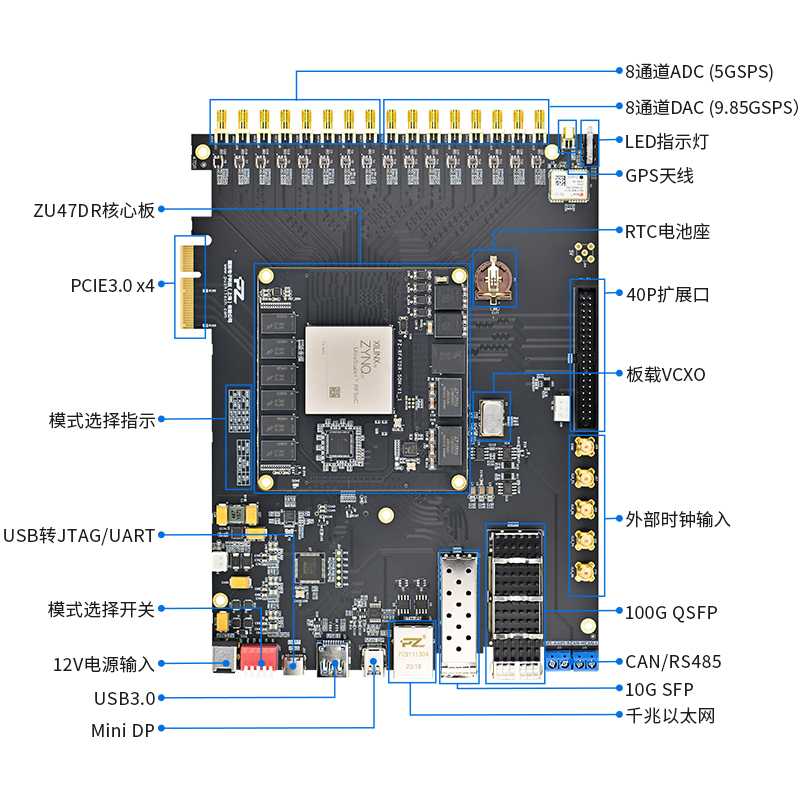

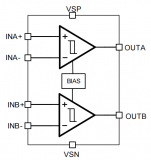

多種射頻接口支持:該平臺支持多種射頻接口,包括ESD保護的高速ADC/DAC,可實現寬頻帶信號處理,增強無線通信鏈路的靈活性。

高可擴展性:支持多種擴展卡和外設連接,滿足用戶個性化和多樣化的需求,能夠輕松適應不同的應用場景。

低延遲和高帶寬:PZ-VU13P-KFB的設計考慮了低延遲和高帶寬的需求,確保在高數據傳輸速率下仍然保持優異的處理能力,是實時應用的理想選擇。

強大的開發工具鏈支持:配備豐富的開發工具和SDK,支持VHDL/Verilog編程,助力工程師快速開發、驗證和部署項目。

1. 超大規模邏輯資源,支撐復雜算法加速

FPGA 核心性能:采用 XCVU13P-2FHGB2104I 主控制器,集成3780K 邏輯單元(Logic Cells)、1728000 個查找表(LUTs)、3456000 個觸發器(Flip-Flops),以及 12288 個 DSP Slices(支持每秒萬億次乘加運算),94.5Mb BLOCK RAM 提供高速數據緩存,可并行處理多通道超高速信號(如 16 路 1GSPS ADC 數據)。

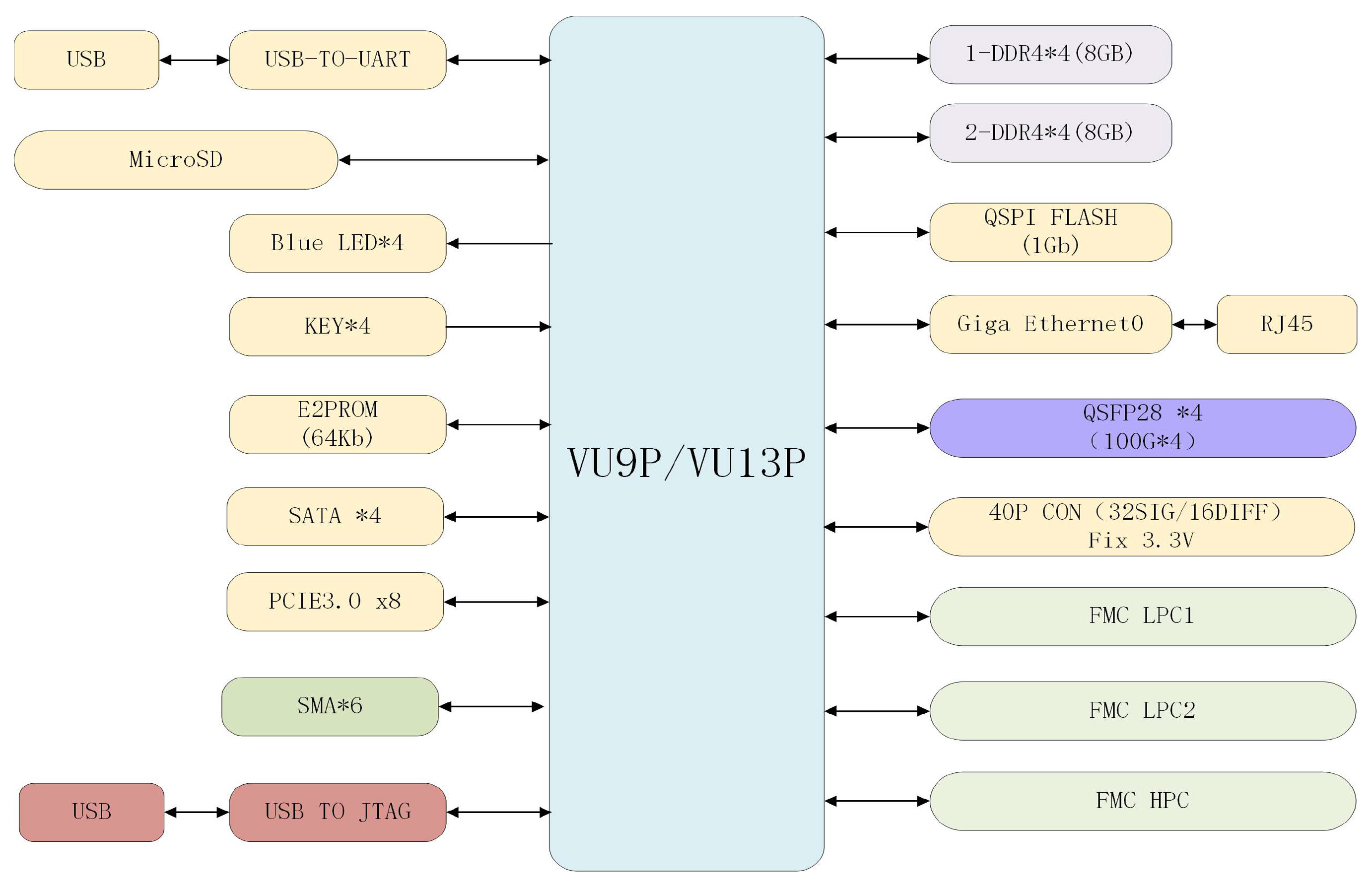

存儲配置:雙組 8GB DDR4(總容量 16GB,64bit 位寬),支持雙通道獨立尋址,滿足超大規模數據緩存需求;1Gbit QSPI FLASH 用于程序固化,支持 JTAG/BPI/SPI 多啟動方式,適配復雜系統啟動邏輯。

2. 超高速接口集群,適配多維度高速傳輸

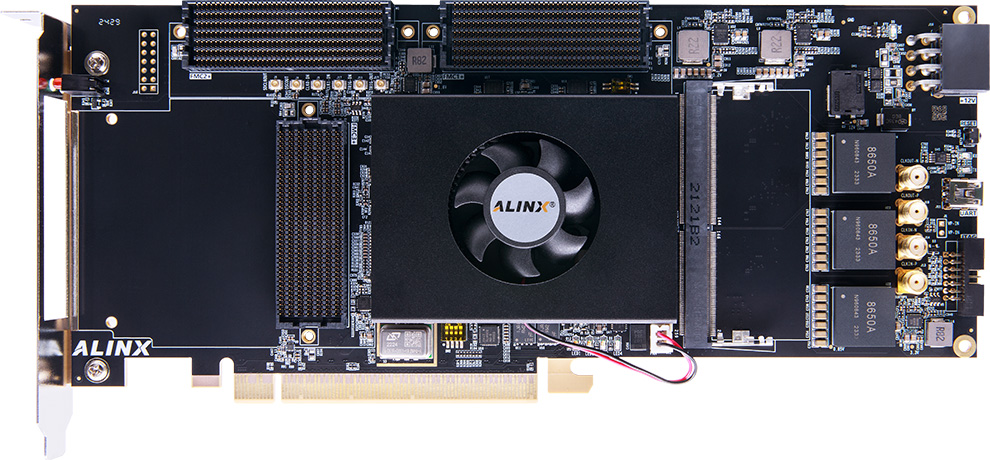

光通信能力:4路 QSFP28 接口(每路支持 100Gbps),集成 GTY 高速收發器(76 對 TX/RX,線速高達 30Gbps),支持 100G Ethernet、OTN 等協議,可構建超高速光傳輸鏈路,適配數據中心互聯、骨干網通信場景。

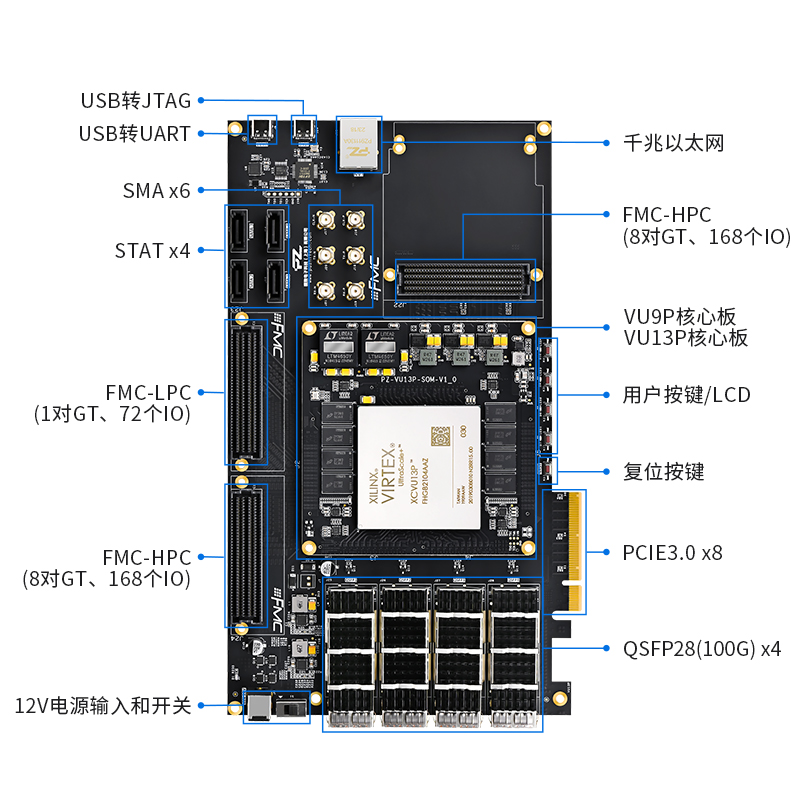

高速擴展接口:PCIe 3.0 x8 接口(帶寬高達 64Gbps),支持與服務器 / 處理器進行高速數據交互;3 個 FMC 擴展口(2 個 HPC 型含 8 對 GT+168 個 IO,1 個 LPC 型含 1 對 GT+72 個 IO),兼容高速 ADC/DAC 子卡(如 AD9680 12bit 5GSPS ADC),實現多通道超高速數據采集。

通用接口:1 路千兆以太網(用于配置與低速數據傳輸)、6 路 SMA 接口(可配置為時鐘輸入 / 觸發信號)、4 路 SATA(用于本地大容量存儲擴展),兼顧通用場景需求。

3. 工業級可靠性,適應極端環境

環境適應性:工作溫度覆蓋 **-40°C~+85°C**,通過寬溫測試驗證;12V/20A 大功率供電(支持峰值電流 30A),具備過流、過壓保護,適配雷達、航空航天等嚴苛供電環境。

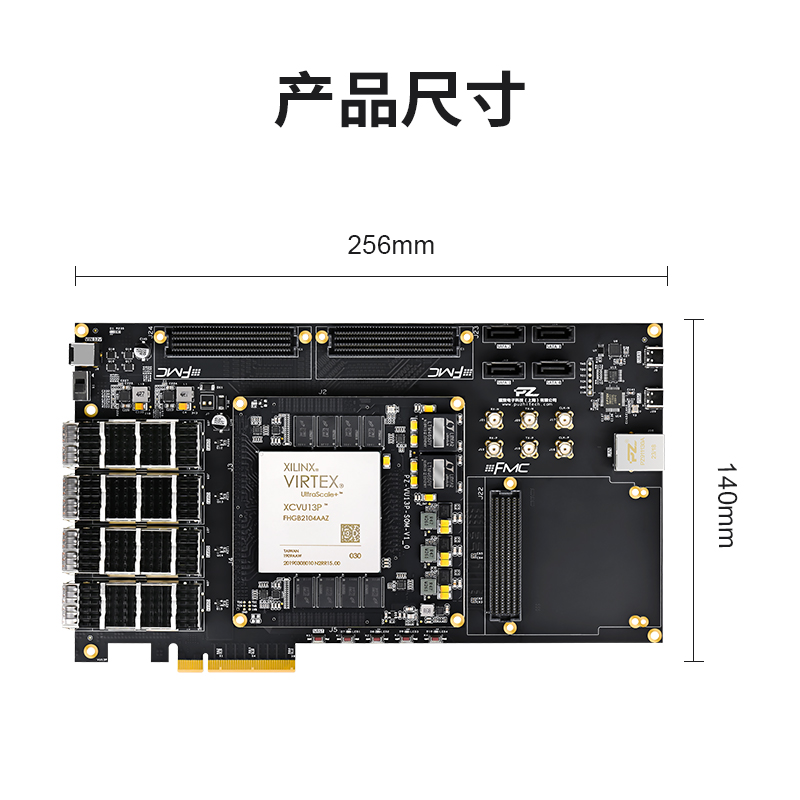

硬件設計:PCB 采用 2.2mm 厚 6 層板設計,黑色啞光沉金工藝,阻抗控制精度 ±5%,確保 30Gbps 高速信號完整性;核心板尺寸 100×100mm,開發板 256×140mm,通過 240P 高速連接器實現穩定連接,抗振動性能滿足軍品級標準。

4. 全棧開發支持,加速高端場景落地

開發工具兼容:支持 Vivado 2023.1+、Vitis HLS,提供完整硬件參考設計(原理圖、PCB 布局)及 SDK 開發包,兼容 Verilog/VHDL 硬件描述語言與 C/C++ 高級語言,降低復雜算法移植門檻。

例程資源:涵蓋 100G QSFP28 誤碼率測試、PCIe 3.0 x8 數據傳輸、多通道 ADC 同步采集(AD9643 14bit 250MSPS)、Aurora 高速串行通信等 20 + 專項例程,支持快速驗證超高速鏈路與并行處理算法。

四、應用場景

100G 光通信系統開發

依托 4 路 QSFP28 接口與 GTY 收發器,可實現 100G Ethernet/OTN 協議棧開發,FPGA 內部完成數據幀解析、FEC 糾錯(如 RS (255,239))與流量調度,PCIe 3.0 x8 接口與服務器交互,適用于骨干網光傳輸設備、數據中心互聯網關。

多通道雷達信號處理

通過 FMC-HPC 接口擴展 4 路 AD9680 子卡(12bit 5GSPS),FPGA 并行實現 16 路數字下變頻(DDC)、脈沖壓縮與目標檢測算法,12288 個 DSP Slices 支持每秒 16 萬億次運算,滿足相控陣雷達實時信號處理需求。

超高速數據采集與記錄

集成 4 路 SATA 接口連接 NVMe SSD 陣列(總帶寬 4GB/s),配合 FMC 擴展的 8 通道 AD7606 子卡(16bit 200KSPS),實現多通道同步數據采集與高速存儲,適用于粒子物理實驗、瞬態信號監測等場景。

國防電子與航空航天

工業級寬溫設計(-40°C~+85°C)與抗振動特性,適配艦載、機載環境;100G 光接口支持遠距離數據回傳,可作為雷達前端處理單元、電子對抗系統核心,滿足國防裝備對可靠性與性能的雙重需求。

無線通信系統:PZ-VU13P-KFB適用于LTE、5G等先進無線通信系統的開發,能夠處理寬頻信號,并進行靈活的調制和解調。

雷達系統:該平臺可用于高分辨率雷達信號的處理,廣泛應用于國防、航空航天和民用安全領域。

信號探測和測量:PZ-VU13P-KFB是無線電頻譜監測、信號探測等應用的理想平臺,支持復雜信號算法的快速驗證和實現。

學術研究與教育:本開發平臺同樣適合用于高等院校的科研和教學,為學生和工程師提供實踐基礎。

關于璞致電子

璞致電子專注于軟件無線電、高速信號處理與嵌入式平臺的研發設計,致力于為全球科研用戶與行業客戶提供高可靠、高性價比的通信與信號處理模塊解決方案。我們以穩定的產品質量和靈活的定制能力,贏得了多個科研單位和通信企業的信賴。我們誠邀您關注璞致(上海)電子科技有限公司的官方網站及社交媒體,獲取更多關于VU13P的詳細信息及后續動態。

審核編輯 黃宇

-

FPGA

+關注

關注

1646文章

22059瀏覽量

619154 -

開發板

+關注

關注

25文章

5707瀏覽量

105171

發布評論請先 登錄

PZSDR/璞致【PZ-ZU47DR-KFB】——RFSoC 架構下的超寬帶軟件無線電開發平臺標桿

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構架構下的智能邊緣計算標桿

基于 IPQ9570 10GPON光纖到戶FTTH WiFi7超高速路由器方案

基于晶豐明源LKS32MC07系列的超高速清潔電器解決方案

APHF系列寬帶超高速捷變頻頻率綜合器-小巧模塊驅動快速跳頻新

使用CYUSB3014進行編程,使用USB 3.0超高速會有什么影響嗎?

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

AI 應用場景全覆蓋!解碼超高端 VU+ FPGA 開發平臺 AXVU13F

ALINX 發布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開發平臺

XCVU9P 板卡設計原理圖:616-基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡 高性能數字計算卡

【PZ-VU13P-KFB】——Virtex UltraScale + 架構下的超高速信號處理標桿,實現高性能系統的部署。

【PZ-VU13P-KFB】——Virtex UltraScale + 架構下的超高速信號處理標桿,實現高性能系統的部署。

評論