隨著電子技術、計算機技術的飛速發展,現代系統中電氣及電子設備的數量大幅增加—— 從消費電子到工業控制,從通信設備到醫療儀器,設備密度持續提升。同時,電子設備的頻帶不斷拓寬(從低頻到射頻甚至毫米波)、功率逐漸增大(如新能源設備的大功率模塊)、靈敏度顯著提高(如傳感器的微伏級信號檢測),而連接各類設備的電纜網絡也因系統復雜化變得更龐大。這一背景下,電磁兼容(EMC) 問題日益凸顯:設備間的電磁干擾可能導致信號失真、功能失效甚至安全隱患。因此,EMC 已成為電子設備設計中不可忽視的核心環節,而比創達等專業機構在EMC 技術研究與解決方案落地中,正通過豐富的工程經驗助力企業突破干擾難題。

電路保護解決方案及電路保護元器件的核心目標,正是服務于電子設備的EMC 問題解決 —— 通過抑制干擾、增強抗擾度,消除電磁兼容隱患,最終確保產品的性能穩定性與長期可靠性。在實際應用中,若防護方案效果未達預期,往往是設計階段的 EMC 考量不足所致。作為近年來設備研究的主流方向,EMC 工作的質量直接決定設備性能上限:做好 EMC 設計,可顯著降低干擾導致的故障概率,提升設備在復雜電磁環境中的適應能力。而比創達通過對千余種設備干擾案例的分析,總結出“設計前置、測試驗證、迭代優化” 的 EMC 解決路徑,為企業提供從方案設計到落地驗證的全流程支持。

一、EMC 的核心定義與要求

EMC(Electro Magnetic Compatibility,電磁兼容性) 是指設備或系統在其電磁環境中 “既能正常運行,又不對環境中其他設備產生無法忍受的電磁干擾” 的能力。這一定義包含兩個相輔相成的要求:

· 干擾發射限值 :設備在正常運行時,向環境釋放的電磁干擾(如傳導干擾、輻射干擾)必須控制在特定限值內,避免干擾周邊設備(例如,家電的輻射干擾不能影響附近的無線電接收設備)。

· 抗擾度要求 :設備對環境中存在的電磁干擾(如電網浪涌、靜電放電、射頻輻射)需具備一定的抵抗能力,確保在干擾存在時仍能正常工作(例如,工業控制器需耐受車間電機啟動時的脈沖干擾)。

無論是干擾發射控制還是抗擾度提升,都需要在設計階段融入專門的EMC 考量 —— 從元器件選型到 PCB 布局,從屏蔽設計到濾波方案,每一步都與 EMC 性能直接相關。比創達在實踐中發現,超過80% 的 EMC 問題可通過前期設計解決,而后期整改的成本往往是前期設計的 5-10 倍。

二、電子可靠性設計:EMC 導向的設計原則

電子可靠性設計是確保設備在預期壽命內穩定工作的基礎,而EMC 是可靠性的重要前提(電磁干擾是導致設備早期失效的主要原因之一)。電子可靠性設計需遵循以下核心原則:

· RAMS 定義與評價指標 :通過可靠性(Reliability)、可用性(Availability)、可維護性(Maintainability)和安全性(Safety)四大指標,量化設備性能,其中 EMC 相關的干擾故障率是可靠性評價的關鍵參數。

· 電子設備可靠性模型 :基于系統架構建立可靠性模型(如串聯模型、并聯模型),并將EMC 風險納入模型分析 —— 例如,敏感模塊的抗擾度不足可能成為系統可靠性的 “短板”。

· 系統失效率的影響要素 :明確電磁干擾、溫度、振動等要素對失效率的影響,其中EMC 相關的干擾是高頻失效的主要誘因之一。

· 電子產品可靠性指標 :結合行業標準(如IEC、GB)設定可靠性目標,包括平均無故障工作時間(MTBF),并通過 EMC 測試驗證干擾環境下的指標達標性。

· 工作環境條件的確定 :針對設備的實際電磁環境(如工業現場的強電磁輻射、醫療場所的低干擾要求)依據規范選擇合適的等級,為后續設計提供依據。

· 系統設計與微觀設計 :在系統層面規劃接地、屏蔽、濾波方案(如整體接地網設計),在微觀層面優化元器件布局與走線(如差分線的對稱設計),從源頭降低EMC 風險。

· 過程審查與測試 :通過設計評審確保EMC 措施落地(如濾波電路是否符合干擾頻率需求),并通過測試驗證(如 EMC 預測試)及時發現問題。

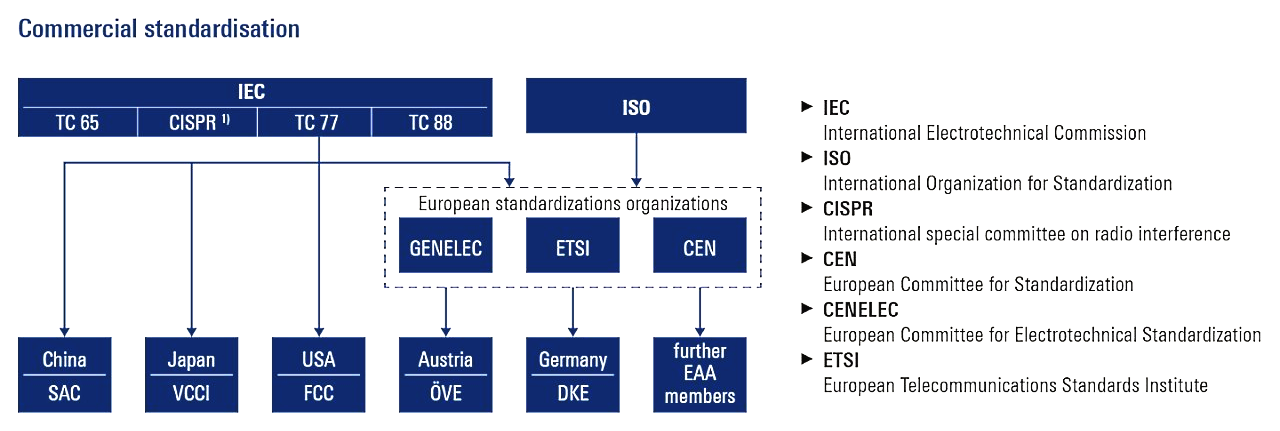

· 設計規范與技術標準 :遵循EMC 相關標準(如 GB 9254《信息技術設備的無線電騷擾限值和測量方法》),結合行業規范制定企業內部設計準則,確保設計一致性。

比創達建議,在設計初期即可引入“EMC 檢查表”,從干擾源、耦合路徑、敏感設備三個維度梳理潛在風險,避免后期出現 “牽一發而動全身” 的整改難題。

三、電路可靠性設計規范:EMC 的核心落地路徑

電路可靠性設計規范是EMC 措施的具體實施指南,涵蓋從參數設計到工藝控制的全流程,其中多項內容直接服務于 EMC 目標:

· 降額設計 :通過降低元器件的實際工作應力提升可靠性,同時需考慮EMC 相關的應力(如電感的飽和電流需預留干擾沖擊余量)。

· 熱設計 :通過熱仿真、散熱結構設計控制元器件溫度(如功率器件的散熱片設計)所有元器件性能在高溫情況下都可能有一定的衰減。

· 電路安全性設計規范 :結合EMC 安全要求(如防雷擊干擾導致的過壓),設計過流、過壓保護電路,避免干擾引發安全事故。

· EMC 設計 :這是規范的核心環節,包括濾波設計(如共模電感選型)、屏蔽設計(如金屬外殼的接縫處理)、接地設計(如單點接地避免地環路)、布線設計(如信號線與電源線的隔離)等,直接決定設備的干擾發射與抗擾度水平。

· PCB 設計 :作為EMC 設計的 “載體”,PCB 布局布線需遵循:

· 布局:敏感電路(如ADC 模塊)遠離干擾源(如開關電源);

· 布線:差分線等長等距,減少阻抗突變;

· 接地:設置完整接地平面,降低地阻抗(減少共模干擾的地電位差);

· 阻抗匹配:避免信號反射(反射會產生額外電磁輻射);

· 加工工藝:確保接地過孔可靠性、屏蔽層焊接質量,避免EMC 性能因工藝缺陷下降。

· 可用性設計 :在確保功能可用的同時,考慮EMC 對操作的影響(如觸摸屏在電磁干擾下的響應準確性)。

比創達在PCB 設計優化中發現,合理的接地平面設計可使共模干擾衰減 20-40dB,而差分線的不等長誤差超過 5% 時,抗擾度會顯著下降。

四、可靠性測試:EMC 性能的驗證手段

可靠性測試是檢驗設計有效性的關鍵,其中EMC 測試是核心環節 —— 通過模擬真實電磁環境,驗證設備的抗干擾能力和干擾控制水平:

· 標準符合性測試 :依據EMC 標準(如 EN 61000 系列)進行測試,包括傳導發射、輻射發射、靜電放電抗擾度、浪涌抗擾度等,確保設備滿足市場準入要求。

· 邊緣極限條件測試 :在極端電磁環境下測試(如最大干擾強度、最低工作電壓疊加干擾),驗證設備的極限耐受能力。

· 容錯性測試 :模擬干擾導致的局部故障(如傳感器信號受干擾失真),測試系統是否能通過冗余設計或算法修正恢復正常(如數據校驗、濾波算法)。

· HALT 測試(高加速壽命測試) :通過高溫、高振動、強電磁干擾的組合應力,快速暴露設計缺陷(如EMC 濾波電路在高溫下失效)。

· 破壞性測試 :通過超過額定值的干擾(如強雷擊沖擊)測試設備的抗毀能力,驗證保護元器件(如TVS 管)的有效性。

· 隱含條件測試 :針對非預期電磁環境(如設備靠近大功率電機時的低頻干擾)進行測試,避免實際應用中的“隱性干擾”。

· 接口條件測試 :重點測試電纜接口的EMC 性能(如 USB 接口的共模干擾抑制),因為接口是干擾傳入傳出的主要路徑。

比創達的測試數據顯示,約30% 的 EMC 問題在標準測試中未暴露,但在邊緣極限條件測試中會顯現,因此建議企業增加 “實際場景模擬測試” 環節。

五、元器件選型:EMC 性能的基礎保障

元器件是EMC 設計的 “基石”,其選型直接影響設備的干擾發射與抗擾度。需結合 EMC 需求選擇合適的元器件:

· 基礎元器件 :電容(如選用低ESR 的陶瓷電容用于高頻濾波)、電阻(選用無感電阻減少高頻干擾輻射)、二極管 / 三極管(開關速度需匹配 EMC 要求,避免開關噪聲過大)。

· 連接與時鐘器件 :接插件(選用帶屏蔽殼的接口,減少輻射)、晶振(選擇低相位噪聲型號,降低時鐘輻射干擾)。

· 光電與信號器件 :光耦(通過光電隔離阻斷共模干擾)、LED(避免驅動電路產生高頻干擾),增強抗擾度)。

· 功率與能量器件 :電控機械動作器件(如繼電器,需設計吸收電路抑制觸點火花干擾)、開關電源(選擇EMC 認證的模塊,減少傳導干擾)、變壓器(優化繞制工藝,降低漏感導致的輻射)。

· 數字IC :選擇低功耗、低開關噪聲的芯片,減少內部干擾源。

· 保護器件 :這是EMC 防護的核心元器件,包括保險絲(過流保護)、磁環 / 磁珠(抑制高頻共模干擾)、壓敏電阻(吸收浪涌干擾)、TVS 管(快速抑制瞬態過壓)。例如,在電源入口串聯磁環,可有效衰減電網傳入的高頻共模干擾。

在選型過程中,需參考元器件的EMC 特性參數(如共模電感的阻抗 - 頻率曲線、TVS 管的響應時間),并結合實際干擾場景(如干擾頻率、幅度)選擇匹配的型號。比創達電磁兼容通過大量案例驗證,在100MHz-1GHz 頻段,磁珠的抑制效果優于普通電感,而 TVS 管的響應時間需小于 1ns 才能有效抑制靜電放電干擾。

六、元器件失效機理與分析:EMC 相關失效的排查

元器件失效可能由電磁干擾直接或間接導致,掌握失效機理與分析方法,可快速定位EMC 相關問題:

· 常見失效機理 :

· 電磁干擾導致的過壓/ 過流:如浪涌干擾擊穿電容、靜電放電損壞 IC 引腳;

· 長期干擾導致的老化加速:如高頻振動干擾使接插件接觸不良、持續共模電流導致電感磁芯損耗增加;

· 分析方法與工具 :通過電磁干擾測試儀(如頻譜分析儀)定位干擾源,結合失效分析工具(如示波器、熱像儀)判斷失效與干擾的關聯性(如測量失效時刻的干擾電壓波形)。

比創達在失效分析中常用“干擾路徑追溯法”:先通過頻譜儀確定干擾頻率,再通過電流探頭定位干擾傳導路徑,最終鎖定失效元器件 —— 該方法可將 EMC 相關失效的排查時間縮短 50% 以上。

總結

EMC 作為電子設備可靠性的核心保障,已從 “后期測試修補” 轉向 “前期設計融入”。從 EMC 定義的雙重要求,到可靠性設計原則中的 EMC 導向,再到元器件選型、PCB 設計、測試驗證的全流程控制,每一環都需圍繞 “抑制干擾、增強抗擾” 的目標展開。比創達的實踐經驗表明,EMC 設計的核心是 “系統化思維”—— 而非孤立的濾波或屏蔽:干擾源控制、耦合路徑阻斷、敏感設備保護需同步考量。

未來,隨著電子設備的進一步集成化、高頻化,EMC 將成為更關鍵的技術壁壘。企業需在設計初期就建立 EMC 意識,結合專業機構的經驗(如比創達的方案庫),從源頭降低干擾風險。只有將EMC 深度融入可靠性設計,才能真正實現設備在復雜電磁環境中的 “穩定運行、互不干擾”,最終提升產品的市場競爭力。

審核編輯 黃宇

-

電磁兼容

+關注

關注

54文章

1982瀏覽量

98951 -

emc

+關注

關注

172文章

4178瀏覽量

187122 -

電路可靠性

+關注

關注

0文章

7瀏覽量

7651

發布評論請先 登錄

電磁兼容(EMC)與電路可靠性設計:從理論到實踐

電磁兼容(EMC)與電路可靠性設計:從理論到實踐

評論