目前主流的CPU制程已經(jīng)達(dá)到了14-32納米(英特爾第五代i7處理器以及三星Exynos 7420處理器均采用最新的14nm制造工藝),更高的在研發(fā)制程甚至已經(jīng)達(dá)到了7nm或更高。但,就是這幾個(gè)在常人看來(lái)稀松平常的數(shù)字背后,卻暗藏著一場(chǎng)激烈的“標(biāo)準(zhǔn)之爭(zhēng)”。

英特爾聯(lián)合創(chuàng)始人戈登?摩爾在半世紀(jì)前提出的摩爾定律,是指每代制程工藝都要讓芯片上的晶體管數(shù)量翻一番。縱觀芯片每代創(chuàng)新歷史,業(yè)界一直遵循這一定律,并按前一代制程工藝縮小約 0.7倍來(lái)對(duì)新制程節(jié)點(diǎn)命名,這種線性微縮意味著晶體管密度翻番。因此,出現(xiàn)了90nm、65nm、45nm、32nm—每一代制程節(jié)點(diǎn)都能在給定面積上,容納比前一代多一倍的晶體管。

切入正題之前,先普及一下什么叫“制程工藝”?

按照百度百科的說(shuō)法,半導(dǎo)體制造工藝指制造CPU或GPU的制程,或指晶體管門電路的尺寸,單位為納米(nm)。制造工藝越先進(jìn),CPU與GPU這樣的芯片內(nèi)部就會(huì)集成更多的晶體管,使處理器具有更多的功能與更高的性能;更先進(jìn)的制造工藝會(huì)減少處理器的散熱功耗(TDP),從而解決處理器頻率提升的障礙;更先進(jìn)的制造工藝還可以使處理器的核心面積進(jìn)一步減小,也就是說(shuō)在相同面積的晶圓上可以制造出更多的CPU與GPU產(chǎn)品,直接降低了CPU與GPU的產(chǎn)品成本。

目前主流的CPU制程已經(jīng)達(dá)到了14-32納米(英特爾第五代i7處理器以及三星Exynos 7420處理器均采用最新的14nm制造工藝),更高的在研發(fā)制程甚至已經(jīng)達(dá)到了7nm或更高。

但,就是這幾個(gè)在常人看來(lái)稀松平常的數(shù)字背后,卻暗藏著一場(chǎng)激烈的“標(biāo)準(zhǔn)之爭(zhēng)”。

考不過就改分,不厚道吧?

戰(zhàn)爭(zhēng)總是激烈的,先講個(gè)笑話放松一下:

一個(gè)班里,坐著I、S和T三位同學(xué)。期末考試結(jié)束了,家長(zhǎng)會(huì)上老師說(shuō),我們班這次S同學(xué)和T同學(xué)成績(jī)最高,值得表?yè)P(yáng)。I同學(xué)聽后很委屈,回家跟家長(zhǎng)說(shuō),我考了98.5,那是真的,那倆傻子只考了79,為了不挨打,自己偷偷把分?jǐn)?shù)改成99了。

好了,開始說(shuō)正經(jīng)的……

在2014年英特爾推出14nm工藝之后不到一年的時(shí)間內(nèi),三星和臺(tái)積電都陸續(xù)推出了自己的14nm工藝和16nm工藝,并被蘋果用于制造iPhone 6s所搭載的A9處理器。2016年底,三星和臺(tái)積電又相繼推出了自己的10nm工藝,看起來(lái)這也比英特爾的10nm工藝早了將近十個(gè)月。

然而英特爾高級(jí)院士、技術(shù)與制造事業(yè)部制程架構(gòu)與集成總監(jiān)馬博(Mark Bohr)卻批評(píng)了競(jìng)爭(zhēng)對(duì)手的一些做法,指出也許是因?yàn)橹瞥踢M(jìn)一步的微縮越來(lái)越難,一些公司背離了摩爾定律的法則。即使晶體管密度增加很少,或者根本沒有增加,但他們?nèi)岳^續(xù)為制程工藝節(jié)點(diǎn)命新名,結(jié)果導(dǎo)致這些新的制節(jié)點(diǎn)名稱根本無(wú)法體現(xiàn)位于摩爾定律曲線的正確位置。

“行業(yè)亟需一種標(biāo)準(zhǔn)化的晶體管密度指標(biāo),以便給客戶一個(gè)正確的選擇。客戶應(yīng)能夠隨時(shí)比較芯片制造商不同的制程,以及各個(gè)芯片制造商的‘同代’產(chǎn)品。但半導(dǎo)體制程以及各種設(shè)計(jì)日益復(fù)雜使標(biāo)準(zhǔn)化更具挑戰(zhàn)性。”Mark Bohr說(shuō)。

他認(rèn)為,“行業(yè)真正需要的是給定面積(每平方毫米)內(nèi)的晶體管絕對(duì)數(shù)量。”也就是說(shuō),每個(gè)芯片制造商在提到制程節(jié)點(diǎn)時(shí),都應(yīng)披露用這個(gè)簡(jiǎn)單公式所測(cè)算出的MTr/mm2 (每平方毫米晶體管數(shù)量(單位:百萬(wàn)))單位中邏輯晶體管密度。只有這樣,行業(yè)才可以厘清制程節(jié)點(diǎn)命名的混亂狀況,從而專心致志推動(dòng)摩爾定律向前發(fā)展。

英特爾公布的數(shù)據(jù)顯示,英特爾10nm制程的最小柵極間距從70nm縮小至54nm,且最小金屬間距從52nm縮小至36nm。這使得邏輯晶體管密度可達(dá)到每平方毫米1.008億個(gè)晶體管,是之前英特爾14nm制程的2.7倍,大約是業(yè)界其他“10nm”制程的2倍。同時(shí),芯片的die area縮小的幅度也超過了以往。可以看到,22nm之前每代工藝的提升可帶來(lái)die area約0.62倍的縮減,14nm以及10nm則帶來(lái)了0.46倍和0.43倍的縮減。

超微縮是英特爾用來(lái)描述從14nm到10nm制程,晶體管密度提高2.7倍的術(shù)語(yǔ)。超微縮為英特爾14nm和10nm制程提供了超乎常規(guī)的晶體管密度,并延長(zhǎng)了制程工藝的生命周期。盡管制程節(jié)點(diǎn)間的開發(fā)時(shí)間超過兩年,但超微縮使其完全符合摩爾定律。

縱向來(lái)看,相比之前的14nm制程,英特爾10nm制程提升了高達(dá)25%的性能和降低45%的功耗。全新增強(qiáng)版的10 nm制程—10++,則可將性能再提升15%或?qū)⒐脑俳档汀?/p>

“如果我們?cè)贆M向的與業(yè)界其他競(jìng)爭(zhēng)友商的16/14nm制程相比,就會(huì)發(fā)現(xiàn)英特爾14nm制程的晶體管密度是他們的1.3倍。業(yè)界其他競(jìng)爭(zhēng)友商10nm制程的晶體管密度與英特爾14nm制程相當(dāng),卻晚于英特爾14nm制程三年。”英特爾公司執(zhí)行副總裁兼制造、運(yùn)營(yíng)與銷售集團(tuán)總裁Stacy Smith說(shuō)。

摩爾定律到底有沒有失效?

2011年下半年,英特爾發(fā)布了22nm工藝;2年半之后的2014年上半年,英特爾才發(fā)布最新的14nm工藝;3年后的2017年,英特爾才正式發(fā)布新一代10nm工藝。而且,在從14nm向10nm提升的過程中,英特爾此前一直秉承的Tick-Tock策略(一年提升工藝,一年提升架構(gòu))也很少再被提及。

“連英特爾這樣最頂級(jí)的芯片制造商都花了3年左右的時(shí)間去完成兩代工藝間的演進(jìn),這難道還不算失效嗎?”人們不禁要問?

但如果我們細(xì)心的挖掘一下就會(huì)發(fā)現(xiàn),英特爾14nm與之前的22nm的命名并不是0.7倍之間的關(guān)系。也就是說(shuō),如果按照0.7倍命名規(guī)律來(lái)看,22nm的0.7倍命名應(yīng)該是16nm,而不是22nm的0.64倍的14nm工藝。

從上兩張圖可以看到,英特爾14nm工藝下的晶體管密度為37.5Mtr/mm2(百萬(wàn)晶體管/平方毫米),而這個(gè)密度是英特爾22nm工藝下晶體管密度的2.45倍。如果按照摩爾定律每?jī)赡攴环臉?biāo)準(zhǔn),兩年半的周期,晶體管數(shù)量應(yīng)該是需要增加2.5倍左右,所以英特爾的14nm工藝的晶體管密度也是基本符合摩爾定律要求的。

而且,從英特爾的32nm到22nm,每?jī)赡甑臅r(shí)間,晶體管密度(單位面積下晶體管的平均數(shù)量)的提升都超過了兩倍(32nm的晶體管密度是45nm的2.27倍)。雖然英特爾從22nm升級(jí)到14nm,以及從14nm升級(jí)到10nm的時(shí)間周期都超過了兩年,但是對(duì)應(yīng)的晶體管密度也分別提升了2.5倍和2.7倍。

而英特爾最新發(fā)布的10nm工藝下的晶體管密度則達(dá)到了100.8Mtr/mm2,大約是上一代的14nm工藝的2.7倍,也就是說(shuō)3年左右的時(shí)間內(nèi),英特爾實(shí)現(xiàn)了晶體管密度2.7倍的增長(zhǎng),雖然略低于本該3倍的增長(zhǎng),但是結(jié)合此前幾代超出摩爾定律的增長(zhǎng),英特爾10nm工藝仍然是符合摩爾定律的對(duì)于晶體管密度的線性增長(zhǎng)要求。

超微縮的意義是什么?

在我看來(lái),超微縮技術(shù)其實(shí)還是想盡可能維持摩爾定律,并保持芯片性能和成本而提出來(lái)的。因?yàn)橹瞥坦?jié)點(diǎn)越小,工藝越復(fù)雜,完全按照摩爾定律的規(guī)律是越來(lái)越困難了。die area越小,一個(gè)300mm晶圓上可放置的晶體管數(shù)量就越多,對(duì)英特爾和其他廠商來(lái)說(shuō),至少不用提前上450mm晶圓,此為其一。

其二,延長(zhǎng)節(jié)點(diǎn)時(shí)間一是出于制造成本,工藝越先進(jìn),成本越高。英特爾說(shuō)了,就算啥都不干,單把設(shè)備搬進(jìn)fab里就需要花費(fèi)70億美元,恐怕英特爾自己也要掂量掂量;二是制造難度在大幅上升,很多技術(shù)需要進(jìn)一步研究,以前那種革命式的前進(jìn)就會(huì)變成漸變式的前進(jìn),這就是英特爾為什么要提出10nm+、10nm++的概念,簡(jiǎn)單說(shuō)就是“小步快跑”。

其三,不是所有應(yīng)用都需要如此先進(jìn)的制造技術(shù),目前也就是CPU、GPU、FPGA這類的芯片追逐新工藝以提升性能,更多應(yīng)用可能28nm工藝甚至90nm工藝都足夠應(yīng)對(duì)了。而且,還要考慮是不是有公司能設(shè)計(jì)出5nm芯片?造出來(lái)能有多少產(chǎn)能?帶來(lái)多大利潤(rùn)?在沒有明確前景的時(shí)候,在相對(duì)比較成熟的工藝上“修修補(bǔ)補(bǔ)”可能更可靠。

其四,為了能夠?qū)崿F(xiàn)縮小面積,提高晶體管密度的目標(biāo),英特爾又提出很多新的技術(shù),比如FinFET、3D堆疊、硅通孔、采用紫外光光刻等等。不過另一方面,單純依靠堆疊晶體管數(shù)量又不行,因?yàn)檫€需要考慮其他因素,比如緩存、驅(qū)動(dòng)電壓、電流密度等,所以確實(shí)是一件很復(fù)雜的事情。

隨著工藝的發(fā)展,制程節(jié)點(diǎn)之間的時(shí)間已經(jīng)延長(zhǎng),成本也更加昂貴,越來(lái)越少的公司可以承擔(dān)得起推進(jìn)摩爾定律的成本,這是整個(gè)行業(yè)正在面臨的問題。憑借規(guī)模優(yōu)勢(shì)、制程技術(shù)優(yōu)勢(shì)和集成密度優(yōu)勢(shì),英特爾正在矢志不渝的推動(dòng)摩爾定律在未來(lái)的繼續(xù)前進(jìn)。

顛覆未來(lái)計(jì)算

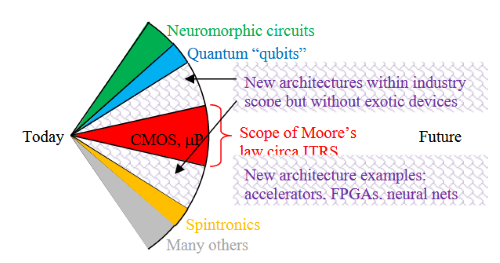

持續(xù)推動(dòng)摩爾定律前行的動(dòng)力不止來(lái)自于制造工藝的演進(jìn)。

隨著從高度動(dòng)態(tài)、非結(jié)構(gòu)化自然數(shù)據(jù)中進(jìn)行收集、分析和決策的需求越來(lái)越高,對(duì)計(jì)算的需求也超越了經(jīng)典的CPU和GPU架構(gòu)。“不去研究數(shù)據(jù)的產(chǎn)生、數(shù)據(jù)的類別、所需要的處理能力是不行的。這和以前的通用數(shù)據(jù)處理不一樣,單純強(qiáng)調(diào)某一種處理器的算力是相當(dāng)片面的。”英特爾公司全球副總裁兼中國(guó)區(qū)總裁楊旭認(rèn)為,人工智能等于GPU是一個(gè)誤解。人工智能最起碼還要發(fā)展一二十年,現(xiàn)在沒有任何一家廠商敢說(shuō)應(yīng)對(duì)未來(lái)人工智能的發(fā)展,所有的計(jì)算能力都準(zhǔn)備好了,能勝任今后所有從簡(jiǎn)單到復(fù)雜的人工智能應(yīng)用。

在向數(shù)據(jù)公司轉(zhuǎn)型的過程中,英特爾將自身定義為端到端方案提供商,即產(chǎn)品線覆蓋云端、網(wǎng)絡(luò)傳輸端和終端。其中,核心來(lái)自云端的大規(guī)模數(shù)據(jù)處理,而布局端到端則可以讓英特爾掌握“數(shù)據(jù)什么時(shí)候來(lái)、是什么樣的數(shù)據(jù)、需要怎么來(lái)處理”。

為了彌補(bǔ)處理新數(shù)據(jù)的能力,跟上技術(shù)發(fā)展的步伐,并推動(dòng)PC和服務(wù)器以外的計(jì)算,英特爾過去六年來(lái)一直在研究能夠加快經(jīng)典計(jì)算平臺(tái)的專用架構(gòu),并且不惜重金收購(gòu)。2017年3月,英特爾斥資153億美元收購(gòu)以色列自動(dòng)駕駛技術(shù)供應(yīng)商Mobileye,并由Mobileye主導(dǎo)如今的英特爾自動(dòng)駕駛事業(yè)部;2016年,英特爾收購(gòu)了AI初創(chuàng)企業(yè)Nervana Systems、視覺處理芯片企業(yè)Movidius等;2015年6月,英特爾斥資167億美元收購(gòu)可編程芯片F(xiàn)PGA的生產(chǎn)商Altera,并成立了可編程解決方案事業(yè)部。

此外,英特爾還同時(shí)加大了對(duì)人工智能(AI)和神經(jīng)擬態(tài)計(jì)算的投資和研發(fā),這被視作英特爾對(duì)未來(lái)計(jì)算的提前布局,旨在顛覆全球未來(lái)計(jì)算格局。

●量子計(jì)算

相對(duì)于傳統(tǒng)計(jì)算,量子計(jì)算最大的優(yōu)勢(shì)是可以并行地運(yùn)行數(shù)據(jù),它表示數(shù)據(jù)的能力達(dá)到傳統(tǒng)計(jì)算機(jī)的50倍,使得我們可以處理在固定內(nèi)存時(shí)間內(nèi)傳統(tǒng)計(jì)算機(jī)解決不了的問題。

如何淺顯易懂的理解量子計(jì)算和傳統(tǒng)計(jì)算的區(qū)別,有一個(gè)行業(yè)公認(rèn)的例子:拋一枚硬幣,通常來(lái)說(shuō),它落地時(shí)或者正面朝上、或者反面朝上,只有兩種答案,這就是二進(jìn)制的傳統(tǒng)計(jì)算。那么,現(xiàn)在你把硬幣立起來(lái)旋轉(zhuǎn),它既是1,也是0,這就是量子計(jì)算。

對(duì)于英特爾這樣一家數(shù)據(jù)公司,押注量子計(jì)算的目的十分明顯。目前全球范圍內(nèi)包括無(wú)人駕駛、人工智能各個(gè)領(lǐng)域的數(shù)據(jù)呈現(xiàn)爆發(fā)式增長(zhǎng),但計(jì)算能力加起來(lái)卻十分有限,量子計(jì)算如果一旦落地使用,將會(huì)呈現(xiàn)顛覆式跨越。

2015年,英特爾就與學(xué)術(shù)界合作伙伴QuTech一起加快量子計(jì)算的研發(fā),2017年10月,雙方攜手成功測(cè)試了17量子比特超導(dǎo)計(jì)算芯片。而在CES 2018期間,英特爾正式向QuTech交付了首個(gè)49量子比特量子計(jì)算測(cè)試芯片。

三個(gè)月,實(shí)現(xiàn)從17量子比特到49量子比特的跨越,迭代速度是顯而易見的。對(duì)于英特爾來(lái)說(shuō),這意味著,量子計(jì)算雖然經(jīng)歷了將近40年歷史,直到今天才邁出萬(wàn)里長(zhǎng)征的第一步,但毫無(wú)疑問的是,屬于英特爾的“量子霸權(quán)”時(shí)機(jī)已經(jīng)來(lái)臨。

●神經(jīng)擬態(tài)研究原型芯片Loihi

神經(jīng)擬態(tài)計(jì)算的靈感來(lái)自我們目前對(duì)大腦結(jié)構(gòu)及其計(jì)算能力的了解。英特爾神經(jīng)擬態(tài)研究原型芯片Loihi包括模仿大腦基本機(jī)制的數(shù)字電路,從而讓機(jī)器學(xué)習(xí)變得更快、更高效,同時(shí)對(duì)計(jì)算力的需求更小。與訓(xùn)練人工智能系統(tǒng)的通用計(jì)算芯片相比,Loihi芯片的能效提升了1000倍。

英特爾科學(xué)家把羅莎林·富蘭克林造型的搖頭娃娃作為訓(xùn)練工具,將其360度旋轉(zhuǎn),讓Loihi能夠從每一個(gè)角度記住羅莎林。訓(xùn)練了一次后,Loihi便能在4秒鐘內(nèi)從少量圖片中區(qū)分一個(gè)橡膠鴨子、一個(gè)玩具大象和搖頭娃娃。盡管研究院只給出了羅莎林的一個(gè)背影,Loihi還是能夠快速辨別出來(lái)。雖然這個(gè)實(shí)驗(yàn)只使用了Loihi不到1%的芯片資源,但它表明了架構(gòu)的有效性。

專家預(yù)測(cè),機(jī)器人將是神經(jīng)擬態(tài)計(jì)算的殺手級(jí)應(yīng)用。在智能家庭的應(yīng)用中,想要入室搶劫的小偷,在進(jìn)入房間時(shí)就可能被智能監(jiān)控?cái)z像頭中的Loihi所識(shí)別,并發(fā)出警報(bào);在汽車應(yīng)用中,Loihi還可能扮演“交警”的角色,緩解交通壓力,或是識(shí)別汽車、自行車的運(yùn)動(dòng);在工業(yè)領(lǐng)域,Loihi也許會(huì)化身為一絲不茍的“監(jiān)工”,監(jiān)測(cè)小到滾珠軸承、大到修建路橋的一切工業(yè)應(yīng)用。“神經(jīng)擬態(tài)芯片將幫助人們減少一些繁重而耗時(shí)的工作”,

●人工智能

英特爾中國(guó)研究院院長(zhǎng)宋繼強(qiáng)認(rèn)為,如果終極AI的智能程度是100%的話,那么當(dāng)下AI的智能程度也就10%。也就是說(shuō),AI還處于嬰兒期,依然有著巨大的成長(zhǎng)空間。

在計(jì)算機(jī)和算法創(chuàng)新的推動(dòng)下,人工智能的變革性力量預(yù)計(jì)將對(duì)社會(huì)產(chǎn)生重大影響。現(xiàn)在,英特爾正在運(yùn)用自身的優(yōu)勢(shì),推動(dòng)摩爾定律和制造領(lǐng)先地位,為市場(chǎng)帶來(lái)各種產(chǎn)品——英特爾至強(qiáng)處理器、英特爾 Nervana技術(shù)、英特爾Movidius技術(shù)和英特爾FPGAs ——以便從網(wǎng)絡(luò)邊緣到數(shù)據(jù)中心和云計(jì)算平臺(tái),來(lái)滿足人工智能計(jì)算任務(wù)的獨(dú)特需求。

正如之前所述,英特爾的獨(dú)特之處在于能夠提供多元化的解決方案,能夠提供適應(yīng)不同工作負(fù)載和能耗的產(chǎn)品,而不是其中的一兩項(xiàng)。這樣,用戶既可以將自己的應(yīng)用與通用軟件融合在一起,選擇在至強(qiáng)處理器上運(yùn)作;同時(shí),如果有更加細(xì)分的工作要求,也可以選擇從通用處理器轉(zhuǎn)向更加具體的處理器:如果想要低延遲,就可以使用FPGA;如果是想更注重低能耗,就可以使用

Movidius;如果想追求諸如數(shù)據(jù)中心這樣的高性能,就可以使用至強(qiáng)。

在宋繼強(qiáng)看來(lái),“任何一種說(shuō)用一種芯片或者說(shuō)一種架構(gòu)方式全處理所有的問題,都是太過夸張的。”因?yàn)楹芏郃I應(yīng)用都還未完成,而且可以預(yù)見的趨勢(shì)是算法帶來(lái)的紅利將越來(lái)越少,邊際效應(yīng)呈逐級(jí)遞減態(tài)勢(shì)。俗話說(shuō),“是騾子是馬,拉出來(lái)溜溜”,等到AI應(yīng)用出來(lái)需要真正落地的時(shí)候,就需要所有人開始真正按照產(chǎn)品而不是學(xué)術(shù)的方式思考,不同的計(jì)算能力適合不同的應(yīng)用,不同的硬件需要逐一接受市場(chǎng)檢驗(yàn)。

-

英特爾

+關(guān)注

關(guān)注

61文章

10166瀏覽量

173925 -

cpu

+關(guān)注

關(guān)注

68文章

11033瀏覽量

215978 -

人工智能

+關(guān)注

關(guān)注

1804文章

48699瀏覽量

246437

原文標(biāo)題:節(jié)點(diǎn)工藝命名藏貓膩,英特爾主動(dòng)出擊正視聽

文章出處:【微信號(hào):edn-china,微信公眾號(hào):EDN電子技術(shù)設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

半導(dǎo)體制程微縮將在2024年以前告終

英特爾10納米可實(shí)現(xiàn)多達(dá)25%的性能提升

【AD新聞】英特爾解讀全球晶體管密度最高的制程工藝

英特爾半導(dǎo)體制程的節(jié)點(diǎn)命名

半導(dǎo)體工藝幾種工藝制程介紹

三星加速制程微縮 DRAM進(jìn)入40納米世代

半導(dǎo)體制程再微縮下去,還有經(jīng)濟(jì)效益嗎?

制程工藝是什么?

NOR Flash制程工藝技術(shù)市場(chǎng)格局及技術(shù)演進(jìn)

HV-CMOS工藝制程技術(shù)簡(jiǎn)介

什么叫“制程工藝”?超微縮的意義是什么?

什么叫“制程工藝”?超微縮的意義是什么?

評(píng)論