文章來源:學習那些事

原文作者:前路漫漫

本文主要講述為什么外延生長技術是半導體制造的核心工藝。

外延生長技術:半導體制造的核心工藝

隨著半導體器件特征尺寸不斷微縮,對高質量薄膜材料的需求愈發迫切。外延技術作為一種在半導體工藝制造中常用的單晶薄膜生長方法,能夠在單晶襯底上按襯底晶向生長新的單晶薄膜,為提升器件性能發揮了關鍵作用。本文將對外延技術的定義、分類、原理、常用技術及其應用進行探討。

在半導體工藝制造領域,隨著CMOS器件特征尺寸持續減小,高質量薄膜材料對于提升器件性能的重要性日益凸顯。外延技術作為生長高質量單晶薄膜的關鍵手段,為半導體產業的發展提供了強大支撐。通過在單晶襯底上生長外延層,不僅能夠精確控制薄膜的厚度、摻雜濃度等參數,還能有效改善器件的性能,如提高雙極型晶體管的高頻性能、解決CMOS器件的閂鎖效應等。因此,深入研究外延技術對于推動半導體制造工藝的進步具有重要意義。

外延的基本概念

1.定義

外延指的是在單晶襯底上,按照襯底晶向生長一層新的單晶薄膜的工藝。生長出的單晶層被稱為外延層,帶有外延層的襯底則被稱作外延片。這種生長方式能夠使外延層與襯底在晶體結構和晶向上保持良好的一致性,從而為半導體器件的制造提供高質量的材料基礎。

2.分類

按照外延生長材料的類型,外延可分為同質外延和異質外延。同質外延是指外延層與襯底材料相同的外延工藝,例如在Si襯底上外延Si,在GaAs襯底上外延GaAs等。這種外延方式能夠充分利用襯底的特性,生長出與襯底晶格匹配良好的外延層,減少晶格缺陷,提高外延層的質量。異質外延則是外延層與襯底材料不同的外延工藝,如Si上外延SiGe,GaAs上外延GaAlAs等。異質外延為實現不同材料之間的優勢互補提供了可能,通過合理選擇外延層和襯底材料,可以獲得具有特殊性能的半導體結構,滿足不同器件的需求。

按照工藝劃分,外延可分為氣相外延(VPE)、液相外延(LPE)、固相外延(SPE)和分子束外延(MBE)等。不同的外延工藝具有各自的特點和適用范圍,在半導體制造中發揮著不同的作用。

按照電阻率高低劃分,外延可分為正向外延和反向外延。正向外延是在低阻襯底上外延高阻層(重襯底上外延生長輕摻雜層),而反向外延則是在高阻襯底上外延低阻層(輕摻雜襯底上外延生長重摻雜層)。這種分類方式主要是根據外延層和襯底的電阻率差異來進行的,不同的電阻率分布會對器件的性能產生重要影響。

按照壓力劃分,可分為常壓外延(100kPa)和低壓(減壓)外延(5 - 20kPa)。壓力對外延生長過程中的氣體傳輸、化學反應以及薄膜質量等方面都有著顯著的影響,選擇合適的壓力條件能夠優化外延工藝,提高外延層的質量和均勻性。

按照溫度劃分,可分為反應溫度在1000℃以上的高溫外延和1000℃以下的低溫外延。溫度是外延生長過程中的一個關鍵參數,它直接影響著化學反應速率、原子擴散速率以及外延層的晶體結構和質量。不同的外延工藝和材料對溫度的要求各不相同,需要根據具體情況進行精確控制。

外延在半導體器件中的重要性

在早期半導體工藝制造中,外延被用于改善雙極型晶體管的高頻性能。為了實現高頻大功率,雙極型晶體管的集電極需要具備高擊穿電壓和低串聯電阻,然而這兩個要求對集電極材料的電阻率有著相互矛盾的需求。外延技術通過在電阻極低的襯底上生長一層高電阻率外延層(正向外延),成功地解決了這一矛盾。將雙極型晶體管制作在外延層上,高電阻率的外延層保證了晶體管有高的擊穿電壓,而低電阻的襯底又降低了串聯電阻,從而顯著提升了高頻雙極型器件的性能。

在CMOS器件中,外延同樣發揮著關鍵作用。CMOS器件中電源和地之間由于寄生PNP和NPN雙極型晶體管相互影響,可能會產生低阻抗通路,導致“閂鎖效應”(Latch - Up),使器件損壞。通過在CMOS器件中增加低電阻率的外延層,可以避開雙極型晶體管的發射極,使其不能“開啟”,從而有效地解決了“閂鎖效應”。此外,在先進CMOS工藝制造中,廣泛采用SiGe源漏選擇性外延工藝給PMOS器件溝道施加壓應力,能夠提高器件的空穴遷移率,進而提升器件性能。

硅氣相外延基本原理

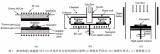

一、外延設備的構成

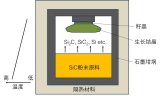

典型的外延設備由多個關鍵部分組成,包括氣體分布系統、反應腔、支撐并加熱硅片的基座、控制系統以及尾氣系統。氣體分布系統中,氣體質量流量控制器(MFC)和真空閥用于嚴格控制氣體流動到反應腔,確保反應氣體能夠精確、穩定地輸送到反應區域。基座一般由石墨或者覆蓋著碳化硅或氮化硅的多晶硅組成,它需要具備足夠的強度,并且不能與反應物和反應產物發生反應,以保證在高溫、復雜化學反應環境下能夠穩定支撐硅片并均勻加熱。

二、反應源

硅氣相外延常用的反應源有四氯化硅(SiCl?)、三氯硅烷(SiHCl?,TCS)、二氯硅烷(SiH?Cl?,DCS)、硅烷(SiH?)以及其他硅烷。早期集成電路制造常采用四氯化硅(SiCl?)作為反應源,但由于其外延生長Si的熱預算很高,會帶來諸多不利影響,而現今集成電路制造工藝對熱預算要求盡可能低,所以目前SiCl?主要應用在傳統的外延工藝中。三氯硅烷與SiCl?特性相似,但其所需的熱預算比SiCl?低很多,且生長速率較高,適合用于生長厚的外延層。二氯硅烷則廣泛應用于在更低溫度下生長高質量的薄外延層,其生長的外延層缺陷密度低,是選擇性外延常用的一種反應源。硅烷的熱分解反應是硅外延生長中較為簡單的化學反應,其化學方程式為SiH?→Si(s) + 2H?(g),這種工藝常用于多晶硅的淀積,也可在低于900℃的溫度下外延生長很薄的外延層,且淀積速率很快。此外,像乙硅烷(Si?H?)或者丙硅烷(Si?H?)等其他硅烷,因其外延生長溫度更低,適合淀積很薄的外延層,且淀積速率快。

三、外延生長模型

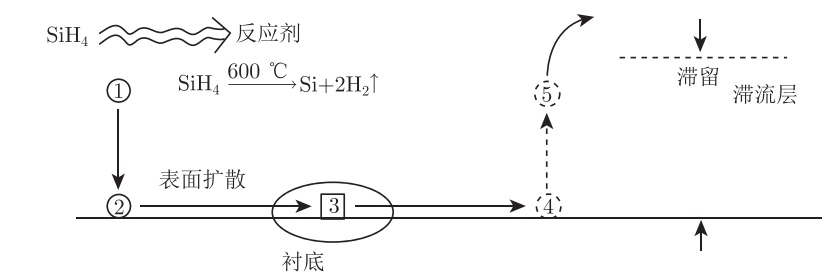

為了更好地理解外延的生長過程,建立了詳細的外延生長模型。在這個模型中,外延生長可劃分為六個具體步驟:

傳輸:反應物氣體經過氣相質量輸運轉移到Si表面。在這一步驟中,反應氣體在氣流的帶動下,通過復雜的氣體動力學過程,從氣體分布系統輸送到硅片表面,為后續的反應提供物質基礎。

吸附:反應物吸附在Si表面。當反應氣體分子到達硅片表面后,會與硅片表面的原子發生相互作用,通過物理吸附或化學吸附的方式附著在硅片表面,為進一步的化學反應做準備。

化學反應:反應物在Si表面進行化學反應,生長Si外延層及副產物。吸附在硅片表面的反應物分子在高溫等條件下發生化學反應,硅原子逐漸結合形成外延層,同時產生相應的副產物。

脫吸:副產物脫離襯底。反應產生的副產物需要從硅片表面脫離,以便為新的反應騰出空間,保證外延生長過程的持續進行。

逸出:脫吸的副產物逸出反應室。脫離硅片表面的副產物在氣流的作用下,從反應腔中排出,避免副產物在反應腔內積累對反應產生不利影響。

加接:生成的Si原子加接到Si襯底晶格點陣上,延續Si襯底晶向。新生成的硅原子會按照硅襯底的晶向,有序地加入到晶格點陣中,從而實現外延層的生長,保持與襯底晶向的一致性。

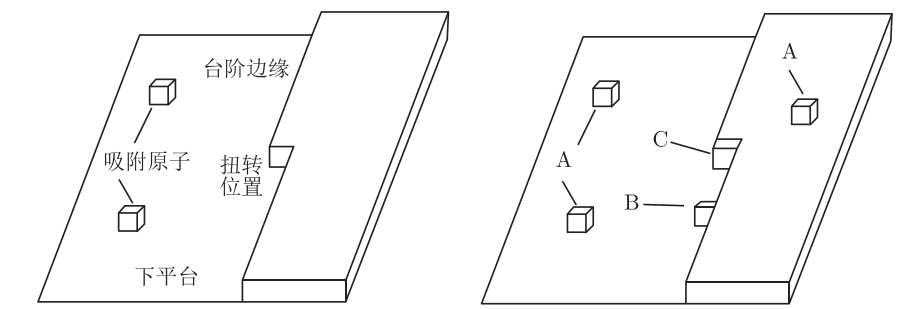

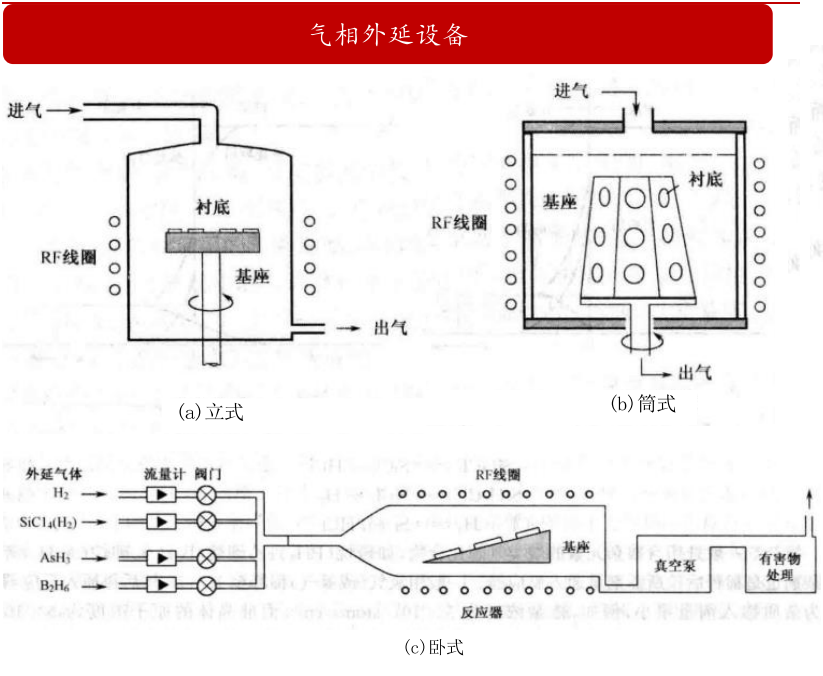

在外延生長進程中,外延層展現出橫向二維逐層生長的特性,這一特性與晶面獨特的“平臺 - 臺階 - 扭轉位置”構造緊密相連。晶面的微觀結構可看作由平整的原子平臺、平臺邊緣的臺階以及臺階拐角處的扭轉位置共同構成。當吸附原子(如硅原子)抵達平臺區域的A位置時,若能量較低而保持靜止,后續吸附的原子會在其周圍無序堆積,逐步形成短鏈狀的硅串或島狀結構。隨著硅串或硅島數量增多并相互連接,極易在晶面內引入大量晶格缺陷(如位錯、層錯),嚴重破壞外延層的單晶質量。

當吸附原子具備較高能量時,會借助表面擴散機制向能量更低的穩定位置遷移。其中,臺階邊緣的B位置因存在未完全飽和的Si - Si鍵,能與遷移原子形成部分共價鍵作用,其能量狀態比平臺中央的A位置更低,成為原子遷移的優先選擇。而位于臺階拐角處的扭轉位置C,原子在此處可同時與兩個方向的晶格原子形成鍵合(約完成50%的Si - Si鍵),能量狀態最為穩定。因此,當原子遷移至扭轉位置時,幾乎不再發生二次遷移,而是直接作為生長節點,推動外延層沿襯底晶向有序延伸。這種“平臺吸附 - 臺階遷移 - 扭轉固定”的生長模式,是確保外延層保持單晶特性的核心機制。

注意,若原子遷移過程受到動力學因素抑制(如低溫或高速生長),將導致生長模式偏離理想的逐層外延。具體表現為:

淀積速率的閾值效應:在特定溫度下,存在一個臨界淀積速率值。當實際生長速率超過該閾值時,氣相中源源不斷供給的原子會使平臺表面迅速飽和,大量原子因來不及遷移至扭轉位置而直接在平臺上無序堆積,最終形成多晶或亞微晶結構;反之,當生長速率低于閾值時,原子有充足時間完成表面擴散,從而實現單晶外延。

溫度對遷移能力的調控:在固定淀積速率條件下,溫度通過影響原子表面遷移率發揮關鍵作用。高溫環境能顯著提升原子動能,使其擴散系數增大(如硅原子在1000℃時的表面遷移距離是800℃時的10倍以上),從而快速定位至扭轉位置完成有序生長;而低溫會導致原子“凍結”在初始吸附位置,被迫以島狀模式生長,最終形成多晶薄膜。這種溫度 - 速率的協同作用,構成了外延工藝窗口優化的核心依據。

外延生長速率的影響因素

反應源

不同硅源的熱分解行為和表面反應活性直接決定生長速率排序。以常見硅源為例:

硅烷(SiH?):在低溫(600 - 900℃)下即可發生熱分解(反應式:SiH? → Si + 2H?),其氣相擴散系數大(約0.1 cm2/s),且分解后產生的Si*活性基團能快速吸附于襯底表面,因此生長速率最高(可達數μm/min)。

鹵代硅烷(如SiCl?、SiHCl?):需更高溫度(1100 - 1200℃)才能通過氫還原反應釋放硅原子(如SiCl? + 2H? → Si + 4HCl),且反應過程伴隨HCl副產物的刻蝕效應,導致實際生長速率低于硅烷。

速率排序規律:SiH? > SiH?Cl?> SiHCl?> SiCl?,這一順序與硅源中Si - Cl鍵的鍵能呈負相關(SiCl?鍵能3.8 eV > SiHCl?鍵能3.3 eV),鍵能越高,需更多能量打破化學鍵,導致反應速率降低。

溫度

溫度通過控制反應速率的限速步驟,使外延生長呈現雙區域特性:

高溫區(質量輸運控制區):

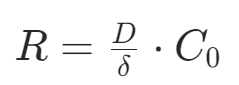

此時表面化學反應速率極快,硅源分子的氣相擴散成為限速步驟。生長速率主要取決于反應氣體穿過邊界層(厚度δ≈0.1 - 1 mm)的擴散通量,可由菲克定律描述:

其中,D為擴散系數,C?為氣相主體濃度。由于擴散系數對溫度的依賴較弱(D ∝ T^(3/2)),高溫區生長速率對溫度波動不敏感,但對反應腔幾何結構(如氣體入口設計、襯底間距)和氣流速度(雷諾數Re)高度敏感。

低溫區(表面反應控制區):

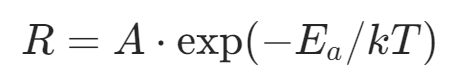

硅源分子的熱分解效率下降,表面化學反應成為限速步驟。生長速率遵循阿倫尼烏斯定律:

其中,活化能E?(如SiCl?氫還原反應E?≈2.3 eV)決定溫度敏感性。

制備厚外延層(如功率器件的高阻漂移層)時,優先選擇高溫區工藝,利用質量輸運控制的穩定性實現均勻生長;

生長納米級超薄外延層(如FinFET源漏應變層)時,采用低溫區工藝,通過精確控溫實現原子級厚度控制,但需注意抑制多晶化傾向。

3.反應劑濃度

以 SiCl?為例,外延工藝主要分成兩個過程,第一過程為氫氣還原 SiCl?,第二過程是 Si 外延層的生長。硅外延生長速率由這兩個過程中較慢的一個決定。當 SiCl?濃度較小時,氫氣還原 SiCl?受限,氧化 - 還原反應釋放硅原子的速率遠遠小于硅原子在襯底上有序排列生長單晶硅的速率,表面的氧化 - 還原反應速率控制了外延層的生長速率,此時屬于表面化學反應控制類型的生長。隨著 SiCl?濃度的增加,氧化 - 還原反應速率加快,外延生長速率也相應增加,當濃度大到一定程度時,氧化 - 還原反應釋放出硅原子的速率會超過硅原子在襯底上有序排列生長單晶硅的速率,此時由氧化 - 還原反應速率控制轉變為由硅原子有序排列生長單晶的速率控制,在這種情況下易生成多晶硅。當增大 SiCl?濃度大于0.1 時,外延生長速率會逐漸減小,這是因為生長的硅膜在高溫下被副產物 HCl 刻蝕,發生了 “逆向反應”。當 SiCl?濃度大于0.27 時,只存在 HCl 對硅膜的腐蝕反應。

氣流速率

與CVD工藝類似,在外延腔體中的氣流速率對淀積速率也有影響。氣體流速越大,邊界層越薄,腔體中反應劑更容易擴散穿過邊界層到達襯底表面,外延生長速率也越快。但當氣流大到一定程度時,邊界層變得很薄,氣相質量輸運到襯底表面的反應劑數量超過外延溫度下的表面化學反應需要的數量,此時外延生長轉變為表面化學反應速率控制,外延層的生長速率基本不隨氣體流量增大而加快。

晶面

不同晶面的共價鍵密度不同,其成鍵結合能力存在差別,也會對生長速率產生一定影響。在共價鍵密度小的晶面,比如(111)晶面,其成鍵結合能力差,外延生長速率較慢;反過來,在共價鍵密度大的晶面,比如(100)晶面,其成鍵結合能力強,外延生長速率則快。

常用外延技術

1.減壓(低壓)化學氣相淀積(RPCVD)

常壓外延作為相對成熟的外延工藝,在半導體工藝制造水平不斷提高的背景下,逐漸暴露出一些問題,如外延圖形漂移過大,掩埋層中雜質向外延層擴散等。而RPCVD作為一種低壓外延技術(1x103 - 2x10?Pa),能夠有效解決這些問題。采用低壓外延技術可減小自摻雜效應,因為在低壓情況下,分子平均自由程增大,加快了雜質的擴散速率,使襯底逸出的雜質能快速地穿過邊界層被排出反應腔,重新進入外延層的機會減小,有效降低了自摻雜效應對外延層中雜質濃度和分布的影響,可以實現陡峭的雜質分布。另外,RPCVD還可改善外延層電阻率的均勻性,減小埋層圖形的漂移和畸變。與常壓外延相比,低壓外延的生長速率只下降了15% - 17%,但其外延生長溫度可以降低100 - 150℃,顯著提高了圖形轉移和掩埋層的質量。

2.選擇性外延(SEG)

硅選擇性外延利用了硅在絕緣體上很難成核并繼續生長成薄膜的特性,可以選擇性地在硅表面特定區域生長外延層而其他區域不生長。硅在SiO?上成核的可能性最小,而在Si上的可能性最大,這是因為Si晶核/SiO?界面會產生較大的晶格失配,與Si晶核/Si襯底的同質成核相比,在SiO?上生成晶核的能量增加。此外,要進行外延生長的地方通常是窗口內或者硅表面的凹陷處,這些地方成核能較低,因此,落在SiO?上的原子因不易成核而遷移到更易成核的硅表面凹陷處。在先進CMOS制造中,選擇性外延可用于導電溝道的應變工程,通過在器件源漏區域外延生長鍺硅(SiGe)以增加導電溝道的壓應力來提高PMOS的空穴遷移率,或者在溝槽中選擇性外延生長高遷移率溝道材料,比如Ge、InGaAs等。

3.橫向超速外延(ELO)

橫向超速外延是基于選擇性外延工藝發展而來的一種外延技術。當硅選擇外延生長的外延層厚度超過SiO?島的臺階高度時,除了沿著垂直硅襯底表面的縱向層生長以外,也會沿橫向生長,這種外延技術稱為橫向超速外延(ELO)。橫向與縱向生長速率之比受到窗口或臺階的高度以及襯底晶向等因素的影響。通過控制這些因素,可以實現對橫向和縱向生長速率的調控,從而獲得具有特定結構和性能的外延層。

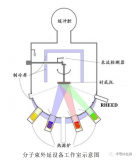

4.分子束外延(MBE)

分子束外延是在超高真空下,使外延層組分元素受熱蒸發(電阻加熱或電子束加熱)形成原子或分子蒸氣流,然后到達加熱的襯底表面,進而形成外延層。分子束外延能夠生長元素半導體單晶,如Si和Ge,以及化合物半導體SiGe、GaAs和GaN單晶等。一個典型的分子束外延系統由超高真空系統、生長系統、測量、分析、監控系統等組成。與其他外延技術相比,分子束外延具有生長速率較慢且可控、表面及界面平整、外延溫度相對低等特點。較低的生長速率使得分子或原子有充分的時間到達成核點,從而制備出高質量的薄膜。外延溫度相對較低,減少了系統的放氣,降低了擴散效應和自摻雜效應的影響,降低了來自襯底雜質的再分布以及熱缺陷的產生。其中固態分子束外延采用固態源超高真空蒸發技術,與普通熱蒸發技術相比,對薄膜的化學組成及摻雜濃度精確可控,并且可實現厚度原子級的精確控制。基于這些優點,分子束外延被廣泛用于生長組分及摻雜分布陡峻的突變異質結和復雜的多層結構,包括量子阱器件、超晶格、激光器等,所有這些都得益于外延生長過程中對成分的精確控制。例如,利用分子束外延技術可以產生許多由GaAs和AlGa???As交替組成的超晶格外延層結構,其厚度低至10?。分子束外延不僅在半導體領域有著重要應用,在光學等其他領域也有用武之地,如公交車上的車站預告板、體育場內的超大顯示屏,其發光元件往往由分子束外延制造。

金屬有機化學氣相淀積(MOCVD)

金屬有機化學氣相淀積是以Ⅲ族、Ⅱ族元素的有機化合物和Ⅴ、Ⅵ族元素的氫化物等作為外延層生長的反應源,以熱分解反應方式在襯底上進行氣相外延生長各種Ⅲ-Ⅴ族、Ⅱ-Ⅵ族化合物半導體以及它們的多元固溶體的外延層。其組分和摻雜可通過反應源的流量進行精確控制。通常MOCVD系統中的晶體生長都是在常壓或低壓(10 - 100 Torr)下通H?的冷壁石英(或不銹鋼)反應腔中進行,襯底溫度為500 - 1200℃,用直流加熱石墨基座(襯底基片在石墨基座上方),H?通過溫度可控的液體源鼓泡攜帶金屬有機物到外延生長區。金屬有機化學氣相淀積能實現外延層生長界面成分的突變,實現陡峭的界面,適用于各種異質結外延層的生長。MOCVD技術已廣泛應用于光學器件、超導薄膜材料、半導體器件、高介電材料等薄膜材料的制備中。在光電器件領域,如發光二極管(LED)、激光二極管(Laser Diode)及太陽能電池(Solar Cells)的制造中,MOCVD發揮著關鍵作用,通過精確控制反應源流量和生長條件,能夠制備出高質量的化合物半導體薄膜,滿足光電器件對材料性能的嚴格要求。同時,在新型微電子器件的研發中,MOCVD也為探索新的材料體系和器件結構提供了有力的技術支持。

總結

外延技術作為半導體制造中的核心工藝,在提升半導體器件性能方面發揮著不可替代的作用。通過在單晶襯底上生長高質量的外延層,能夠精確控制薄膜的各項參數,解決半導體器件制造中的諸多難題,如改善雙極型晶體管的高頻性能、克服CMOS器件的閂鎖效應等。隨著半導體技術的不斷發展,對高質量薄膜材料的需求日益增長,外延技術也在不斷創新和進步。外延層缺陷仍然是影響半導體器件性能的重要因素,在后續的文章中我們也還會對外延層缺陷進行探討。未來,外延技術將繼續在半導體制造領域發揮關鍵作用,為推動半導體產業的持續發展提供強大動力,同時也將在其他相關領域,如光學、傳感器等,展現出更廣闊的應用前景,促進多學科的交叉融合和協同發展。

-

CMOS

+關注

關注

58文章

5997瀏覽量

238231 -

半導體

+關注

關注

335文章

28677瀏覽量

233602 -

晶體管

+關注

關注

77文章

9990瀏覽量

140854 -

制造工藝

+關注

關注

2文章

201瀏覽量

20293

原文標題:外延生長技術:半導體制造的核心工藝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

GaN外延生長方法及生長模式

SiGe外延工藝及其在外延生長、應變硅應用及GAA結構中的作用

8英寸單片高溫碳化硅外延生長室結構

鐘罩式熱壁碳化硅高溫外延片生長裝置

一文詳解外延生長技術

一文詳解外延生長技術

評論