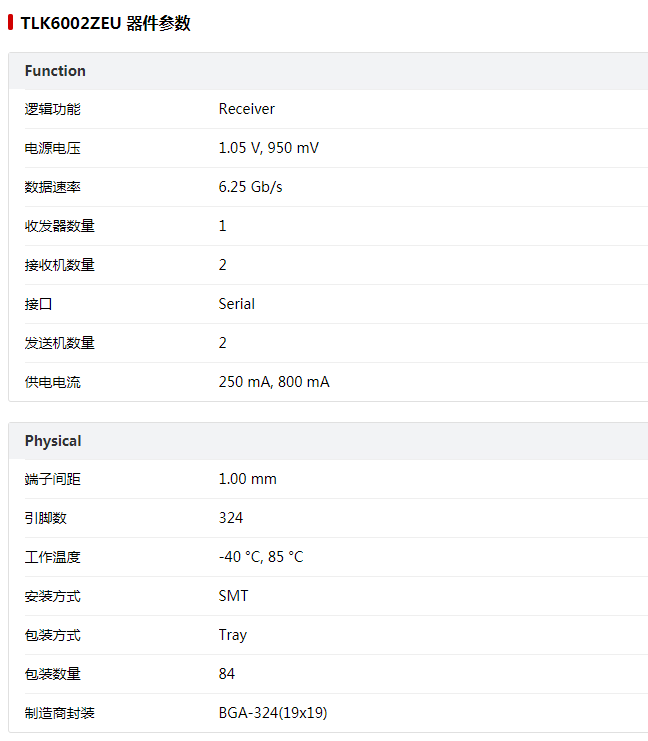

給大家帶來Texas Instruments (TI)推出的 TLK6002ZEU參數特性、引腳 EDA模型與數據手冊解析。

TLK6002是德州儀器 (TI) 很久之前就推出的業界首款 6 千兆位每秒 (Gbps) 的雙通道串行器-解串器 IC (SerDes),其可為無線應用提供 高達470 兆位每秒 (Mbps) 至6.25 Gbps 的連續數據速率。該TLK6002支持從原有速度到最新更快速度的升級,符合所有無線基站設計所需的 OBSAI 與 CPRI 標準要求。TLK6002 可用于各種無線基礎設施應用,其中包括 WiMAX、TD-SCDMA、WCDMA 以及 CDMA2000 等。

雙通道 0.47Gbps 至 6.25Gbps 多速率收發器TLK6002是多千兆位收發器產品組合的一員,旨在用于超高速雙向點對點數據傳輸系統。它專門用于基站RRH(遠程無線電頭)應用,但也可用于其他高速應用。

最新 SerDes 使用統一 122.88 MHz 或 153.6 MHz 固定參考時鐘頻率,可支持通用公共無線電接口 (CPRI?) 與開放式基站架構發起組織 (OBSAI) 速率。此外,TLK6002 的 20 位并行單端接口還可便捷地連接至現場可編程門陣列 (FPGA)。與具有高速串行鏈路的 FPGA 相比,更經濟的 FPGA 與 TLK6002 組合方案可顯著降低系統成本。

TLK6002ZEU EDA模型免費下載:http://www.asorrir.com/p/e951433114

http://www.asorrir.com/p/e951433114

TLK6002ZEU 數據手冊免費下載:

TLK6002 的主要特性與優勢:

接收機均衡與收發器預加強功能可通過對線纜振幅損失與碼間干擾 (ISI) 的補充來提高信號完整性,從而可支持超過 50 厘米的線跡范圍;

集成型自動 CPRI/OBSAI 速率感測功能可自動調諧適應于系統設置,無需其它硬件或軟件;

集成型高精度時延測量(6.144 Gbps 時為 0.6510 ns)功能可簡化系統設計,為設計人員減少工作量;

支持 CPRI/OBSAI 數據速率:0.6144、0.768、1.2288、1.536、2.4576、3.072、4.9152 以及 6.144 Gbps;

TLK6002 可為眾多 TI 數字信號處理器 (DSP)、數據轉換器以及時鐘產品提供補充。

TLK6002支持0.470 Gbps至6.25 Gbps的串行接口速度。速率支持包括使用單個固定參考時鐘頻率(122.88 MHz或153.6 MHz)的所有CPRI和OBSAI速率(0.6144 /0.768 /1.2288 /1.536 /2.4576 /3.072 /4.9152 /6.144 Gbps)。

TLK6002 20位并行接口采用1.5V或1.8V HSTL單端格式。 20位接口允許并行端的低速信號,因此可以在系統設計中使用低成本FPGA。并行接口可以編程為SDR(單數據速率)或DDR(雙數據速率)模式。線路速率可以設置為滿(≤6.25Gbps),半(≤3.75Gbps),四分之一(≤1.88Gbps)或第八(≤0.94Gbps)。可以使用器件輸入或軟件控制寄存器設置線速率。

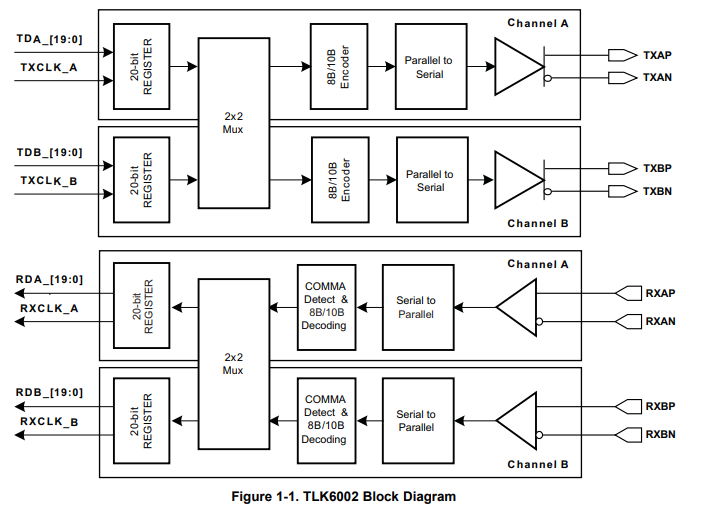

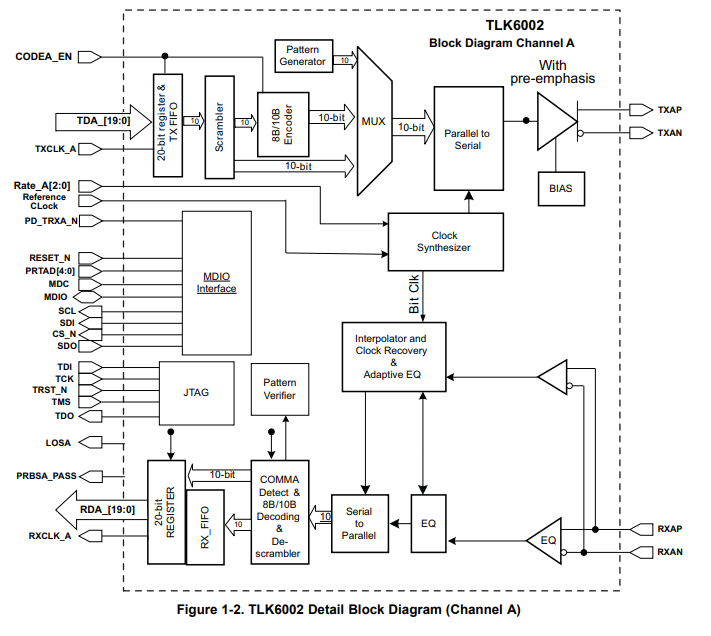

TLK6002作為物理層接口器件執行并行到串行,串行到并行和時鐘提取的數據轉換。串行收發器接口的最大串行數據速率為6.25 Gbps。

TLK6002在其并行發送和接收數據總線上接受單端HSTL信號。如果內部8B /10B編碼和解碼被使能,則TCL /B_ [19:0]被TXCLK_A /B鎖存并發送到內部8b /10b編碼器,其中產生的編碼字被串行化并使用線路時鐘差分傳輸以期望的線速率從SERDES參考時鐘導出。如果禁用內部編碼和解碼,則TDA /B_ [19:0]被定義為20位數據被串行化并根據所需的線路速率進行未經修改的傳輸。

接收方向執行串行輸入串行數據的并行轉換,將得到的20位并行數據與恢復的字節時鐘(RXCLK_A /B)同步。可選的解碼接收數據可在RDA /B_ [19:0]輸出信號上獲得。

串行發送器和接收器使用帶集成終端電阻的差分電流模式邏輯(CML)實現。

TLK6002提供兩個本地(并行側)和兩個遠程(串行側)環回模式,用于自檢和系統診斷。

TLK6002具有集成的信號丟失(LOS)檢測功能功能,在串行輸入信號沒有足夠電壓幅度(≤75mV dfpp )的條件下置位。注意,當使能接收數據通路數據的信號丟失失敗時(輸入位6.6),輸入信號必須≥150mV dfpp 。

特性總結:

雙通道470Mbps至6.25Gbps連續/多速率收發器

支持所有CPRI和OBSAI數據速率

集成延遲測量功能,精度為±814 ps

CPRI /OBSAI自動速率感應(ARS)功能

支持SERDES操作,8B /10B數據模式(20-位和16位+控制器)

20位HSTL單端并行數據接口(集成源和

端接)

每個通道的共享或獨立參考時鐘< /li>

延遲/深度可配置發送和接收FIFO。

環回功能(串行和并行端),符合OBSAI

支持串行重新定時操作

支持PRBS(2 7 -1),(2 23 -1)和(2 31 -1)和

CRPAT Long /短期生成和驗證

雙電源:1.0V內核和1.5V /1.8VI /O標稱電源

串行側三分頻發送去加重和接收自適應均衡離子

允許擴展背板延伸

串行輸出上的可編程輸出擺幅

最小接收器差分輸入閾值為100mV dfpp

信號丟失(LOS)檢測(≤75mV dfpp )

背板,銅纜或光模塊的接口

熱插拔保護< /li>

JTAG; IEEE 1149.1 /1149.6測試接口

MDIO; IEEE 802.3第22條支持

65nm高級CMOS技術

全速率工業環境工作溫度(-40°C至85°C)

器件封裝; 324 PBGA

應用程序

WI基礎設施

CPRI和OBSAI鏈接

專有鏈接

背板

高速點對點傳輸系統

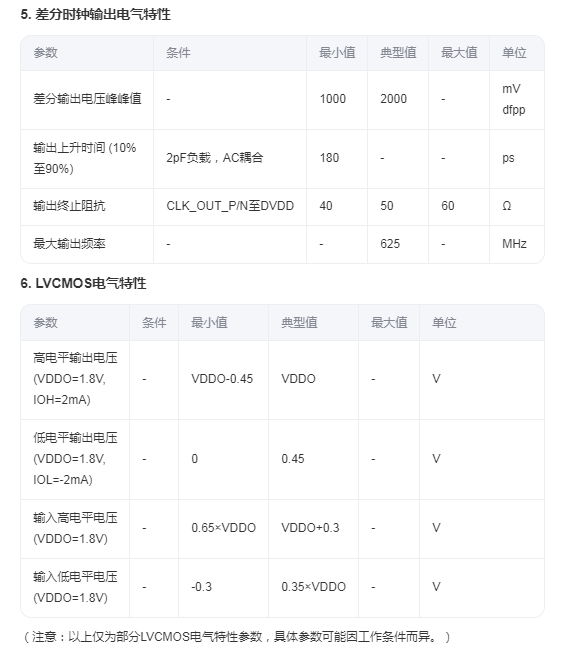

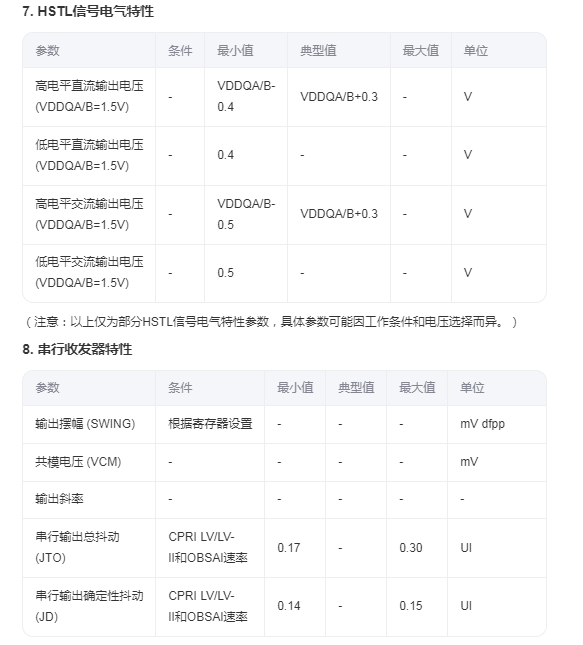

TLK6002ZEU 數據手冊解析、電氣規格匯總:

TLK6002文檔主要內容提煉

1. 引言

- ?產品概述?:TLK6002是一款雙通道多速率收發器,支持0.47Gbps至6.25Gbps的串行接口速度,專為超高速雙向點對點數據傳輸系統設計。

- ?應用領域?:包括無線基礎設施、CPRI和OBSAI鏈路、專有鏈路、背板以及高速點對點傳輸系統等。

2. 收發器特性

- ?雙通道支持?:每個通道獨立或共享參考時鐘。

- ?多速率支持?:支持所有CPRI和OBSAI數據速率,通過單個固定參考時鐘頻率(122.88MHz或153.6MHz)實現。

- ?接口模式?:支持20位SDR/DDR并行接口模式,可選8b/10b編碼/解碼。

- ?集成功能?:包括延遲測量、可編程輸出擺幅、CPRI/OBSAI自動速率感應(ARS)功能、PRBS生成和驗證等。

3. 功能描述

- ?數據轉換?:支持并行到串行、串行到并行的數據轉換以及時鐘提取。

- ?串行接口?:使用差分電流模式邏輯(CML),集成終端電阻,支持熱插拔保護。

- ?自動速率感應?:ARS功能可自動檢測并適應CPRI/OBSAI標準定義的串行鏈路速率。

- ?延遲測量?:集成延遲測量功能,測量精度±814ps。

- ?電源管理?:支持多種電源管理模式,包括引腳控制和MDIO接口控制。

4. 引腳描述

- ?信號引腳?:包括串行收發引腳(TXAP/N、RXAP/N等)、時鐘引腳(REFCLK_0_P/N、REFCLK_1_P/N等)、控制引腳(RATE_A[2:0]、RATE_B[2:0]等)以及其他功能引腳。

- ?電源引腳?:提供多種電源電壓選項,包括核心電壓(DVDD)、模擬電壓(AVDD)、高速模擬電路電壓(VDDT)等。

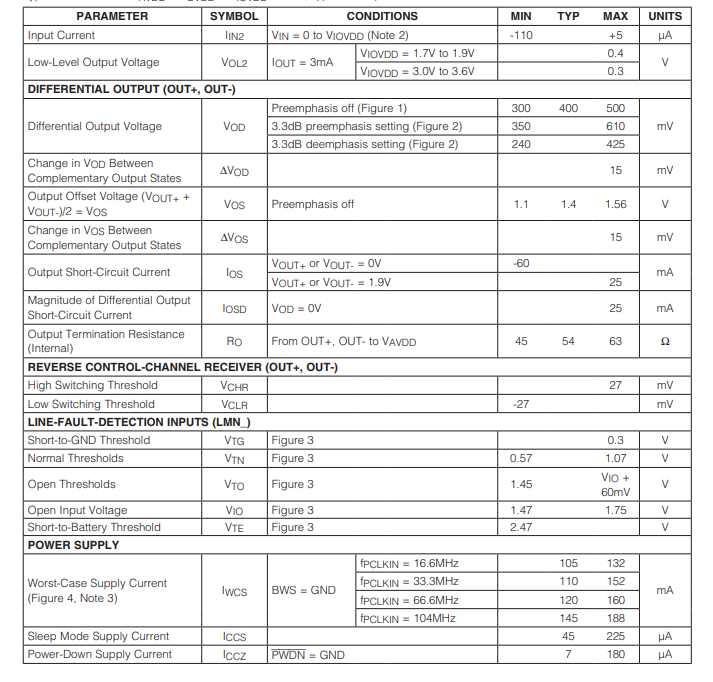

5. 電氣規格

- ?絕對最大額定值?:規定了供電電壓、輸入電壓、存儲溫度等參數的最大值。

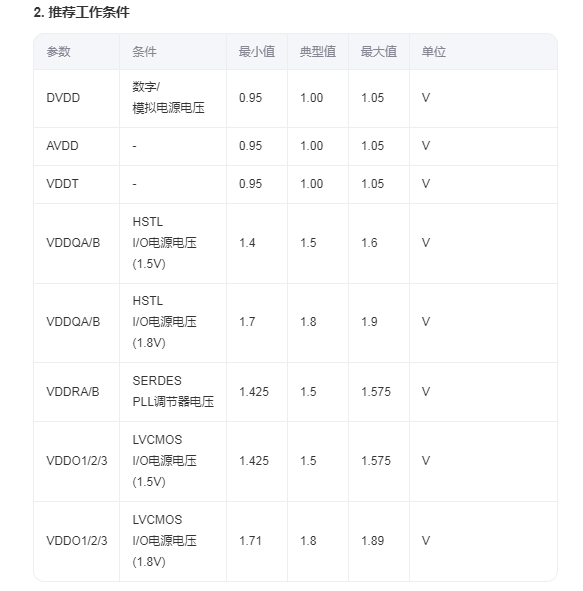

- ?推薦工作條件?:詳細列出了各電源電壓、電流、溫度等推薦工作范圍。

- ?參考時鐘要求?:規定了參考時鐘的頻率范圍、相對精度、占空比等。

- ?串行收發器特性?:包括輸出擺幅、共模電壓、輸出斜率、抖動容限等詳細參數。

6. 應用指南

- ?設備初始化?:提供了詳細的設備初始化步驟,包括引腳設置、設備復位、時鐘配置、數據速率設置等。

- ?測試模式?:支持多種測試模式,包括CRPAT長/短模式、PRBS 27-1/223-1/231-1模式等,用于生成和驗證測試圖案。

- ?功耗評估?:提供了不同工作條件下的設備功耗評估數據。

7. 封裝與尺寸

- ?封裝類型?:采用324引腳BGA封裝。

- ?尺寸與標記?:數據手冊提供了封裝尺寸、引腳間距、設備標記等詳細信息。

8. 附件

- ?連續速率設備配置?:詳細說明了如何根據串行速率和SERDES配置選擇參考時鐘。

- ?8b/10b控制字符支持?:列出了支持的8b/10b控制字符及其編碼。

- ?設備延遲規范?:提供了設備在不同工作模式下的絕對延遲、靜態延遲變化和動態延遲變化數據。

核心電氣規格匯總如下:

一、電源規格

- ?核心電壓?:

- 工作范圍:0.95V - 1.05V(推薦1.0V)

- 最大耐受電壓:1.1V45

- ?I/O電壓?:

- 支持雙電壓:1.5V 或 1.8V HSTL單端接口14

- 容差范圍:±5%4

- ?功耗?:

- 最大電源電流:250mA(全速率工作)5

二、接口電氣特性

- ? 串行收發器(CML差分接口) ?:

- 輸出差分擺幅:800mVpp - 1600mVpp(可編程調節)45

- 接收靈敏度:最小100mVpp差分輸入4

- 共模電壓范圍:0V - 1.2V4

- ? 并行接口(20位HSTL) ?:

- 邏輯高電平:0.8×VDDIO 1

- 邏輯低電平:0.2×VDDIO 1

三、時鐘與信號完整性

- ?參考時鐘要求?:

- 頻率:122.88MHz 或 153.6MHz(固定)14

- 抖動容限:≤1ps RMS(12kHz-20MHz頻帶)4

- 占空比:45% - 55%4

- ?抖動性能?:

- 發送端抖動:≤0.15UI(峰峰值)4

- 接收端容限:支持>0.6UI抖動輸入5

四、環境與可靠性

- ?工作溫度?:

- 工業級:-40°C 至 +85°C57

- ?保護功能?:

- 熱插拔保護(Hot Plug)4

- 信號丟失檢測(LOS):閾值≤75mVpp差分4

五、物理封裝

- ?封裝形式?:324引腳BGA(19mm×19mm)67

- ?焊盤設計?:裸露焊盤增強散熱

TLK6002ZEU EDA模型免費下載:http://www.asorrir.com/p/e951433114

http://www.asorrir.com/p/e951433114

-

收發器

+關注

關注

10文章

3660瀏覽量

107448 -

ti

+關注

關注

113文章

8021瀏覽量

214411 -

串行器

+關注

關注

0文章

161瀏覽量

14880 -

解串器

+關注

關注

1文章

135瀏覽量

14012 -

TLK6002

+關注

關注

0文章

4瀏覽量

7548

發布評論請先 登錄

英特爾在14nm制程技術上推出32 Gbps串行解串器

基于TLK10232的雙通道 XAUI 轉 SFI 參考設計包括BOM,原理圖及光繪文件

基于TLK10081的千兆以太網多速率鏈路聚合器參考設計包括原理圖和BOM表

TLK6002 2 通道 0.47Gbps 至 6.25Gbps 多速率收發器

TLK1102E 11.3 Gbps雙通道電纜和PC板均衡器數據表

TLK6002雙通道0.47Gbps至6.25Gbps多速率收發器數據表

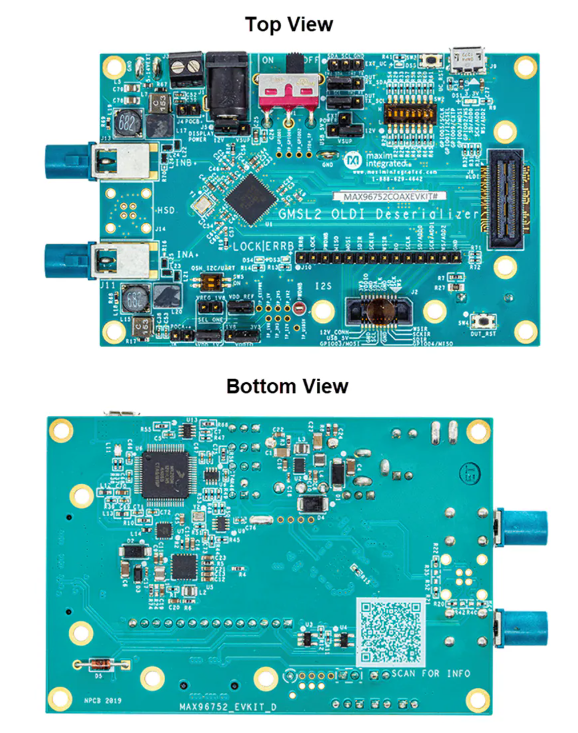

Analog Devices / Maxim Integrated MAX96752xEVKIT解串器評估套件數據手冊

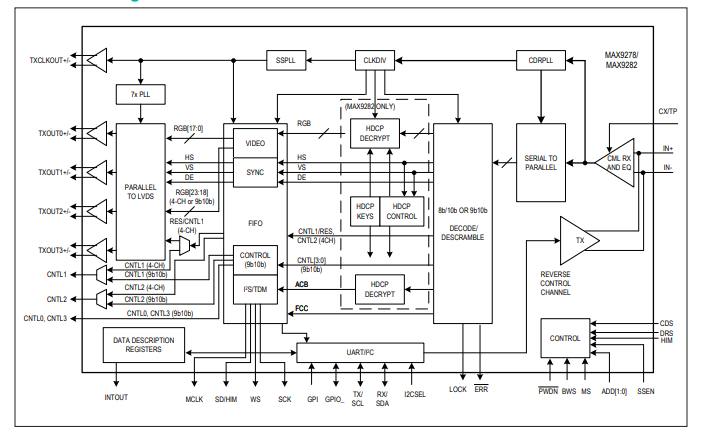

MAX9278/MAX9282用于同軸電纜或STP輸入和LVDS輸出的3.12Gbps GMSL解串器技術手冊

Texas Instruments LMH0044SQ/NOPB 自適應電纜均衡器的參數特性、EDA模型 數據手冊分享

Texas Instruments TLK6002ZEU 6千兆位每秒 (Gbps) 的雙通道串行器-解串器 EDA模型與數據手冊解析

Texas Instruments TLK6002ZEU 6千兆位每秒 (Gbps) 的雙通道串行器-解串器 EDA模型與數據手冊解析

評論