高速串行接口(如PCIe、以太網、HDMI等)是芯片設計的“高速公路”,但調試過程卻常讓人抓狂——信號質量差、誤碼率高、眼圖模糊……耗時耗力的測試流程,是否讓你無數次想對屏幕喊“太難了”?

別急!XSBERT——專為FPGA高速收發器設計的調試利器,幫你一鍵生成誤碼率報告、實時掃描眼圖,輕松驗證鏈路穩定性!

01為什么需要XSBERT?

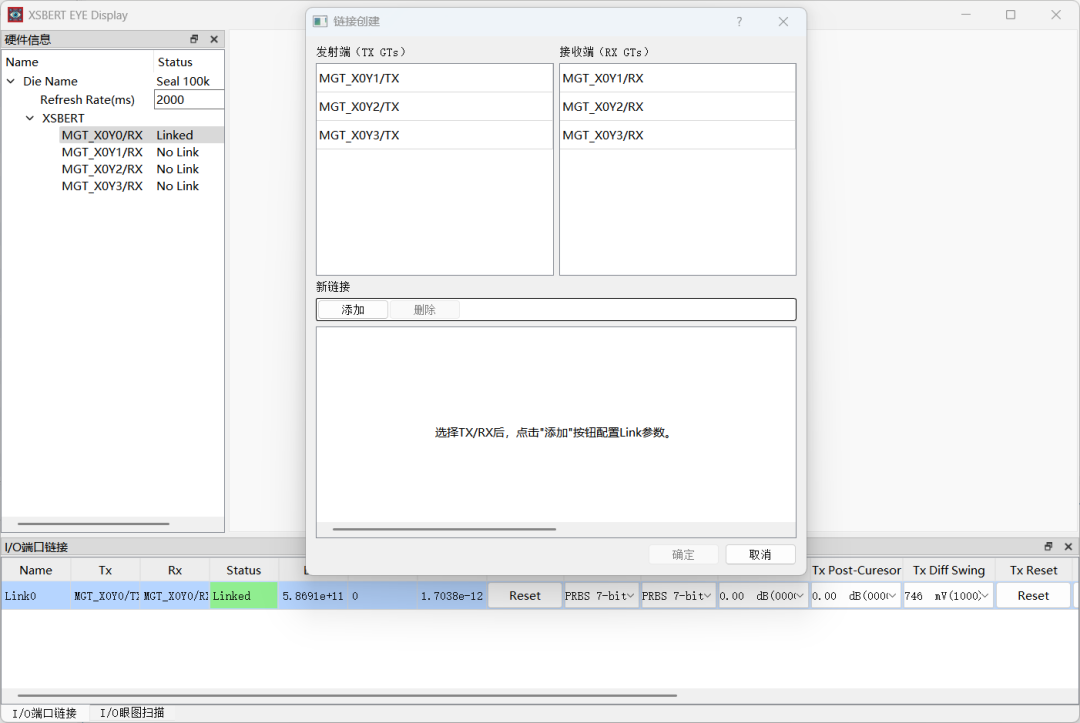

想象一下:傳統的高速接口測試需要外接儀器、反復編譯代碼、手動分析數據……而XSBERT直接集成在FPGA中,通過JTAG接口即可完成以下操作:

1、實時誤碼率測試:發送偽隨機序列(PRBS),自動統計誤碼率,瞬間鎖定問題鏈路

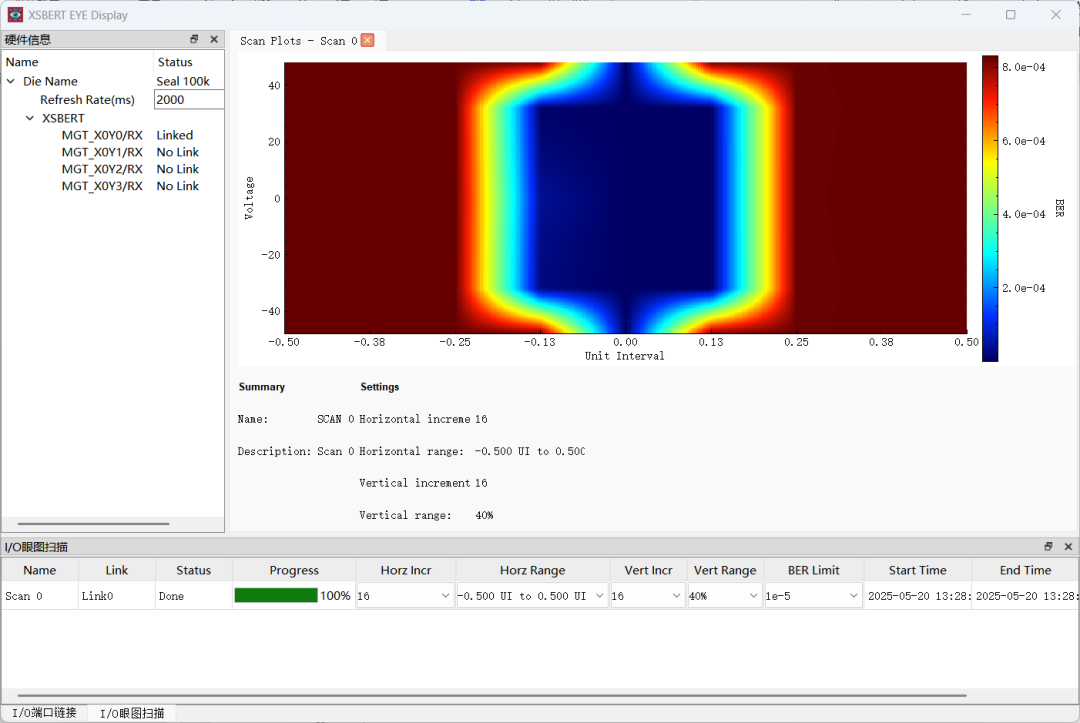

2、眼圖掃描:直觀顯示信號質量,快速判斷噪聲、抖動等干擾影響

3、動態參數調整:無需重新編譯設計,直接在線修改預加重、均衡參數,優化信號完整性

02XSBERT的三大核心優勢

1. 開箱即用,節省90%調試時間

無需外接復雜儀器,只需下載bit/bin文件,通過xsberteye軟件即可完成配置。

一鍵生成4通道測試鏈路(Quad),統一配置線速率、時鐘源等參數。

支持多種回環模式,快速驗證收發器性能。

2. 信號質量一目了然

眼圖掃描:自由調節水平和垂直分辨率,直觀查看信號張開度,精準定位衰減點。

實時監控:誤碼率、PLL狀態、鏈路通斷狀態實時刷新,問題無處遁形。

3. 靈活適配多種場景

支持1.25~12.5 Gbps寬范圍線速率,覆蓋主流協議需求。

動態調整發送端預加重、差分擺幅,優化長距離傳輸信號質量。

接收端均衡功能,有效對抗通道失真,提升抗干擾能力。

03典型應用場景

1. 芯片原型驗證:快速驗證PCIe、以太網等接口的物理層穩定性,縮短迭代周期。

2. 產線測試:批量檢測FPGA收發器性能,避免因信號問題導致的批量返工。

3. 教學與培訓:學生/新人通過眼圖與誤碼率數據,直觀理解高速信號完整性概念。

04立即體驗

無論你是芯片設計老手,還是初入行的工程師,XSBERT都能讓高速接口調試化繁為簡!

-

FPGA

+關注

關注

1645文章

22040瀏覽量

618185 -

收發器

+關注

關注

10文章

3671瀏覽量

107918 -

接口

+關注

關注

33文章

8997瀏覽量

153699

原文標題:“芯”技術分享|高速串行接口調試難?XSBERT一鍵搞定誤碼率與眼圖掃描!

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

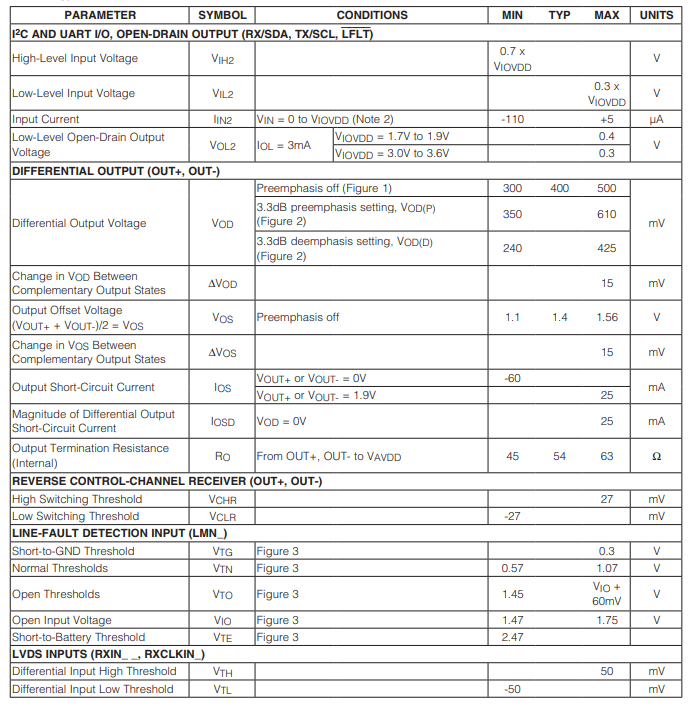

MAX9249多媒體串行鏈路串行器,帶有LVDS系統接口技術手冊

是德S系列示波器如何應對高速串行測試

智多晶XSTC_8B10B IP介紹

智多晶XSBERT讓高速串行接口調試化繁為簡

智多晶XSBERT讓高速串行接口調試化繁為簡

評論