引言:本文介紹FPGA與高速ADC接口方式和標準以及JESD204與FPGA高速串行接口。

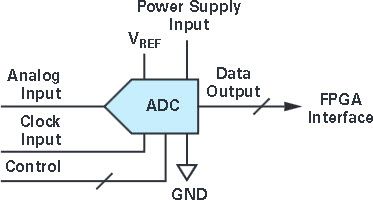

如圖1所示,ADC模數轉換器可以與微控制器、DSP、FPGA以及ASIC均可以實現互聯,在進行選擇時,需要考慮以下因素:設計要求的信號處理和轉換器性能、開發成本、IO接口速率、開發的便利性以及器件材料成本。

圖1:ADC與處理器互聯需要權衡的因素

2. 高速ADC常見的接口形式

(1)并行接口

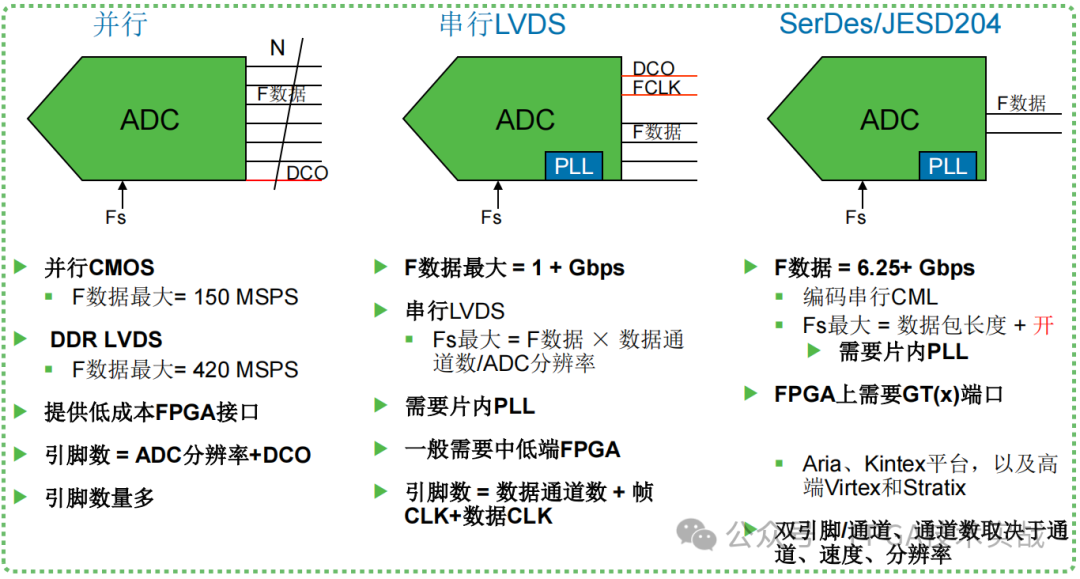

并行接口又可分為并行CMOS和并行DDR LVDS接口。CMOS并行接口一般速率在150MSPS,DDR LVDS ADC可達420MSPS速率,通常對FPGA接口性能要求不高,在低檔FPGA接口實現,但是由于采用并行接口,這種ADC占用的FPGA IO管腳數量較多。

(2)串行LVDS接口

串行LVDS ADC最大速率可≥1Gbps,通常ADC片內集成倍頻PLL,由于數據數量較高,通常需要中端FPGA實現互聯,與FPGA互聯的引腳數與使用的數據通道數有關。

(3)JESD204B接口

JESD204B ADC最大數據速率≥6.25Gbps,通常常用串行CML接口標準。需要使用FPGA收發器接口才可互聯,一般需要中高端FPGA,由于采用Gbps收發器,使用的FPGA IO引腳數較少。

高速ADC常見的接口形式對比如圖2所示。

圖2:高速ADC常見的接口形式對比

3. 高速ADC常見控制接口

高速ADC的控制接口幾乎都獨立于數據接口,通常為SPI,有時為I2C或引腳可編程(物理管腳配置)。控制接口通常用于訪問轉換器的寄存器,實現芯片控制。

控制接口運行速率比數據接口慢得多,SPI運行速率通常小于40 MHz (5 Mbps)。

4. JESD204串行接口

(1)采用JESD204串行接口優點

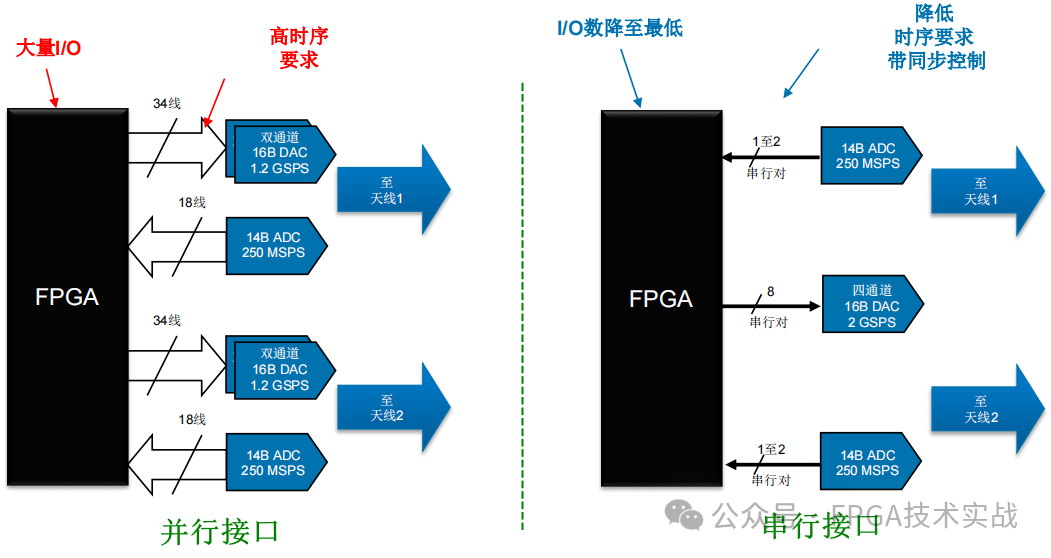

如圖3所示,采用JESD204串行接口優點較多。

圖3:并行接口與串行接口對比

1)簡化整體系統設計

減少走線路徑,簡化電路板走線設計;

簡化同步時序設計。

2)引腳數減少 – Tx和Rx均是如此

引腳數量多的低速并行接口轉為引腳數量少的高速串行接口;

3)降低系統成本

更小的IC封裝和電路板設計可降低成本。

4)輕松擴展滿足未來帶寬需要

幾何尺寸更小、速度更快,更好地適應標準。

(2)JESD204標準演進

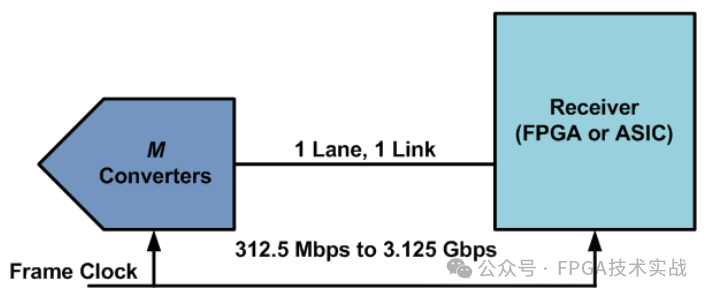

JESD204,是JEDEC定義的針對高速點對點串行接口的一項標準,用于互連兩個(或更多)器件,如轉換器到數字接收器、數字源到DAC或數字源到數字接收器。

與以前的轉換器接口相比單個主機串行接口可用來傳遞所有數據、時鐘和幀信息。時鐘和幀信息嵌入數據流中,無需擔心數據和時鐘之間的設置建立和保持時間。

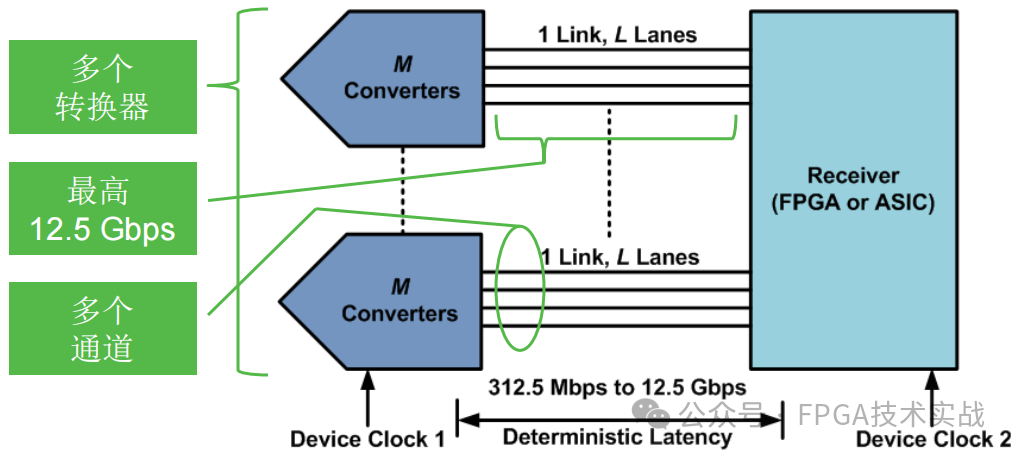

圖4:JESD204標準鏈路

JESD204這種標準在轉換器和接收器(通常為FPGA或ASIC)定義了一種數千兆位的數據鏈路。

如圖4所示,JESD204(2006年4月)原有標準只定義了一條通道、一條鏈路對采樣通過單個串行通道到多個轉換器的傳輸進行了定義,最高速率為3.125Gbps。

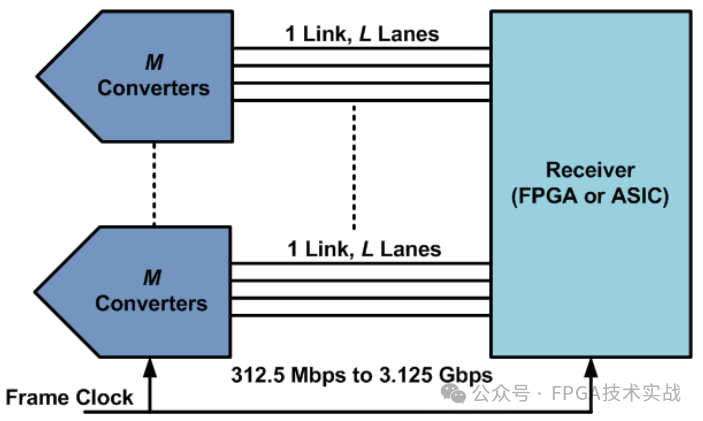

圖5:JESD204A標準鏈路

如圖5所示,JESD204A(2008年4月)—首次修訂,將原有標準擴展成多條鏈路和多個通道。修訂版增加了通過多個對齊串行通道向多個轉換器傳輸數據的能力,最高速率為3.125 Gbps。

圖6:JESD204B標準鏈路

如圖6所示,JESD204B(2011年8月),第三版,運用一個器件時鐘,同時增加了多項措施以確保獲得確定性的延遲。支持通過多個對齊的串行通道向多個轉換器傳輸數據,最高速率為12.5Gbps。

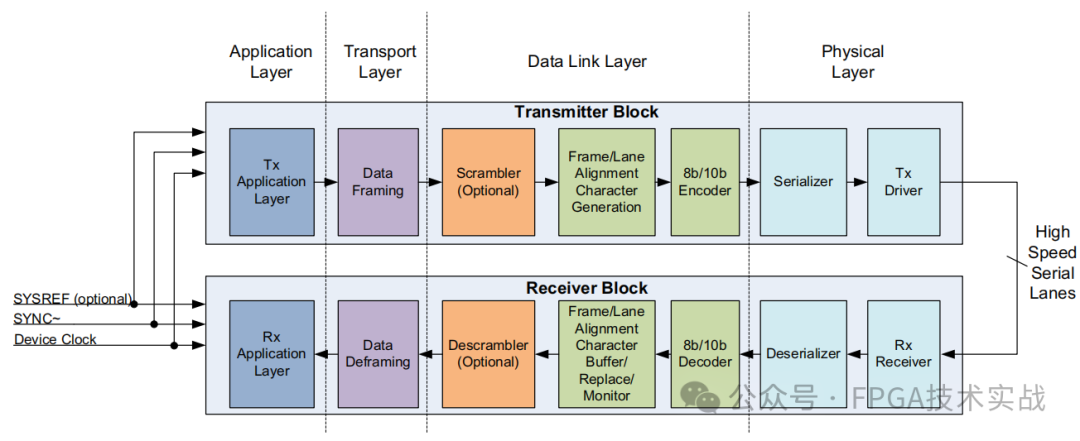

(3)JESD204標準各層

圖7:JESD204B各層的簡化數據流

如圖7所示,JESD204B標準是一種分層規范,規范中的各層都有自己的功能要完成。應用層支持JESD204B鏈路的配置和數據映射。傳輸層實現轉換樣本與成幀未加擾八位字之間的映射。加擾層可以選擇性地獲取八位字并進行加擾或解擾,以便通過延展頻譜尖峰來降低EMI效應。加擾在發送器中完成,解擾在接收器中完成。在數據鏈路層中,可選加擾的八位字編碼成10位字符。該層也是產生或檢測控制字符的地方,目的是監視和維護通道對齊。物理層即串行器/解串器(SERDES)層,負責以線路速率發送或接收字符。該層包括串行器、驅動器、接收器、時鐘和數據恢復電路。

(4)JESD204B 標準中關鍵信號

1)器件時鐘(Device clock)

系統中的一個時鐘信號,為鏈路中數據的幀速率的諧波;

在JESD204B系統中,幀時鐘不再是主機系統參考源。

2)SYNC~

從接收器到發送器的一個系統同步低電平有效信號,表示同步狀態;

當SYNC~為低電平時,接收器和發送器同步;

如果涉及多個DAC/ADC,則可將SYNC~組合起來。

3)通道0、 … 、 L-1

鏈路中的差分通道(通常為高速CML);

8B/10B代碼組按先MSB/后LSB方式傳輸。

4)SYSREF(可選)

一個可選的源同步、高壓擺率時序分辨率信號,用于重置器件時鐘分頻器(包括LMFC),以確保獲得確定性的延遲。

同時分配至系統中的ADC/DAC和ASIC/FPGA邏輯器件,可用時,SYSREF是JESD204B系統中的主機時序參考,因為它負責重置LMFC參考。

(5)JESD204x 標準中確定性延遲

當從JESD204x接收器輸入端到JESD204x接收器輸出端的時間始終為相同時鐘周期時,則延遲具有確定性;

在并行實現中,確定性延遲很簡單—時鐘隨數據傳輸;

在串行實現中,存在多個時鐘域,結果可能造成不確定性;

JESD204和JESD204A并未針對如何確定延遲的確定性進行規定

JESD204B通過規定三個器件子類,試圖解決這一問題:

器件子類0—不支持確定性延遲;

器件子類1—利用SYSREF(500 MSPS以上)實現確定性延遲;

器件子類2—利用SYNC(最高500 MSPS)實現確定性延遲。

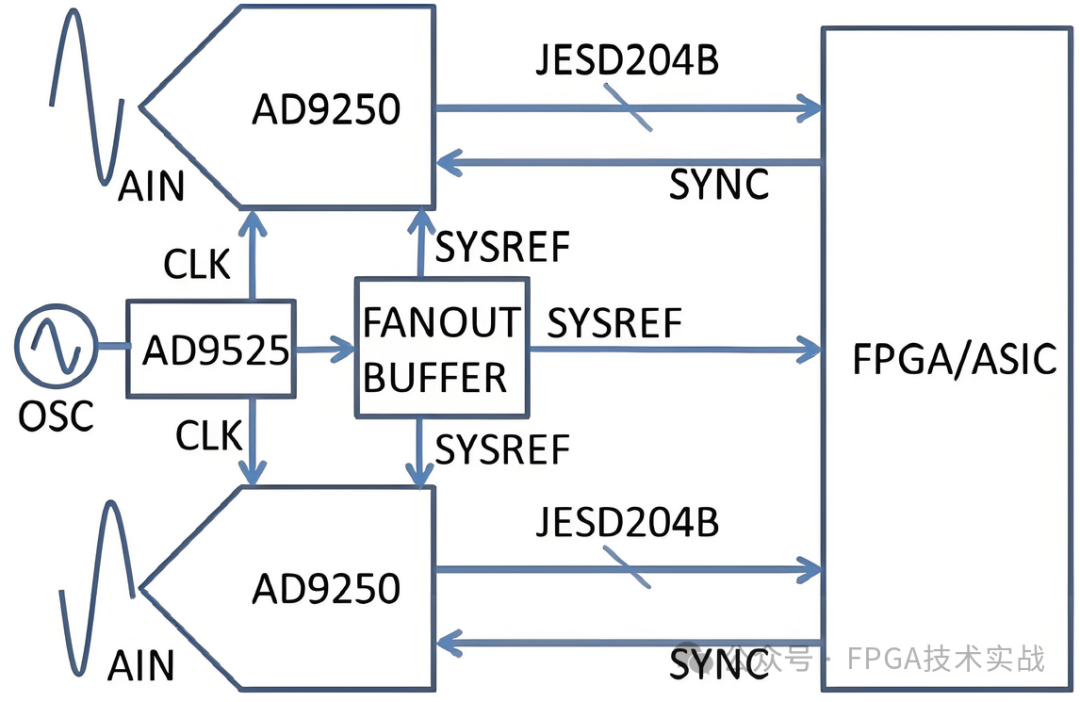

(6)JESD204B硬件應用示例

圖8:JESD204B ADC與FPGA硬件連接示例

如圖8所示,AD9250是來自ADI公司的250 MSPS 14位雙ADC,支持子類1實現中的JESD204B接口。該子類允許使用SYSREF事件信號跨ADC進行模擬采樣同步。AD9525是一款低抖動時鐘發生器,不僅提供高達3.1 GHz的七個時鐘輸出,而且能夠根據用戶配置同步SYSREF輸出信號。這兩種產品,再加上ADI公司的一系列扇出緩沖器產品,提供了一個框架,可以精確同步和對齊發送到FPGA或ASIC進行處理的多個ADC數據。

來源:本文轉載自FPGA技術實戰公眾號

-

處理器

+關注

關注

68文章

19821瀏覽量

233690 -

FPGA

+關注

關注

1643文章

21980瀏覽量

614526 -

接口

+關注

關注

33文章

8961瀏覽量

153260 -

adc

+關注

關注

99文章

6648瀏覽量

548360 -

模數轉換器

+關注

關注

26文章

3306瀏覽量

128016

原文標題:FPGA與高速ADC接口簡介

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

LVDS高速ADC接口_Xilinx FPGA實現

LVDS高速ADC接口, xilinx FPGA實現

基于FPGA的高速ADC接口設計

fpga高速接口有哪些

高速ADC與FPGA的LVDS數據接口中避免時序誤差的設計考慮

FPGA與高速ADC接口簡介

FPGA與高速ADC接口簡介

評論