概述

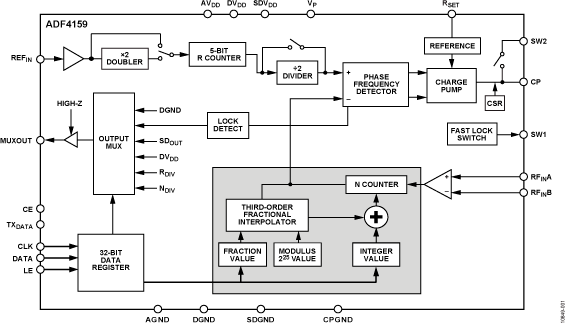

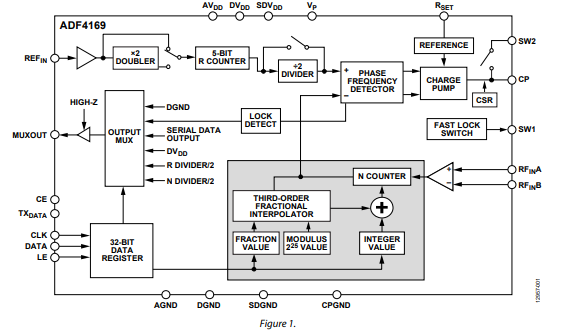

ADF4159是一款具有調制、以及快速和慢速波形產生能力的13 GHz小數N分頻頻率合成器, 該器件使用25位固定模數,提供次赫茲頻率分辨率。

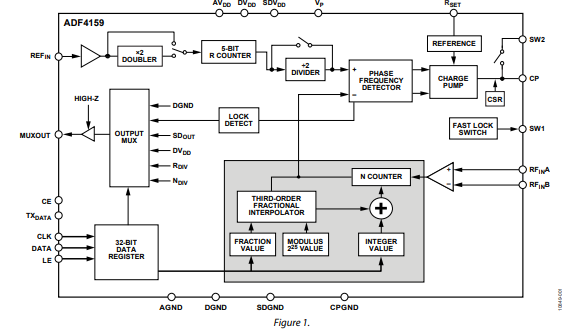

ADF4159由低噪聲數字鑒頻鑒相器(PFD)、精密電荷泵和可編程參考分頻器組成。 該器件內置一個Σ-Δ型小數插值器,能夠實現可編程小數N分頻。 INT和FRAC寄存器可構成一個總N分頻器(N = INT + (FRAC/2 ^25^ ))。

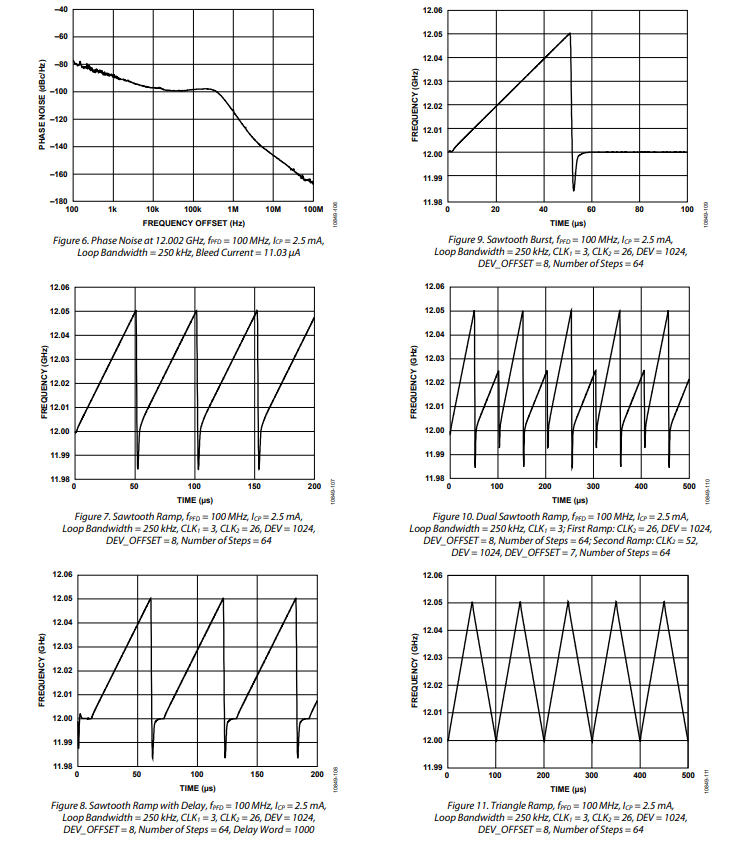

ADF4159可用于實現頻移鍵控(FSK)和相移鍵控(PSK)調制。 還有一些可用的頻率掃描模式,可在頻域內產生各種波形,例如鋸齒波和三角波。 掃描可以設置為自動進行,也可以設置為通過外部脈沖手動觸發每個步驟。 ADF4159具有周跳減少電路,可進一步縮短鎖定時間,而無需修改環路濾波器。

所有片內寄存器均通過簡單的三線式接口進行控制。 ADF4159采用2.7 V至3.45 V模擬電源和1.62 V至1.98 V數字電源供電,不用時可以關斷。

數據表:*附件:ADF4159直接調制 快速波形產生13GHz小數N分頻頻率合成器技術手冊.pdf

應用

特性

- RF帶寬達13 GHz

- 高速和低速FMCW斜坡發生

- 25位固定模數可提供次赫茲頻率分辨率

- PFD頻率最高達110 MHz

- 歸一化相位噪底:?224 dBc/Hz

- FSK和PSK功能

- 鋸齒波、三角波和拋物線波形發生

- 斜坡與FSK疊加

- 具有2種不同掃描速率的斜坡

- 斜坡延遲、頻率回讀和中斷功能

- 可編程相位控制

- 2.7 V至3.45 V模擬電源供電

- 1.8 V數字電源供電

- 可編程電荷泵電流

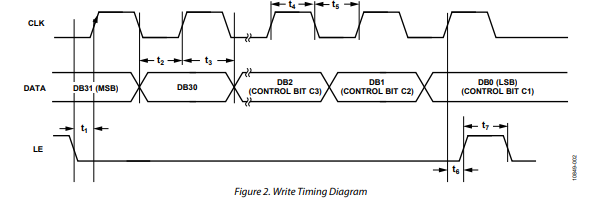

- 三線式串行接口

- 數字鎖定檢測

- ESD性能: 3000 V HBM、1000 V CDM

- 通過汽車應用認證

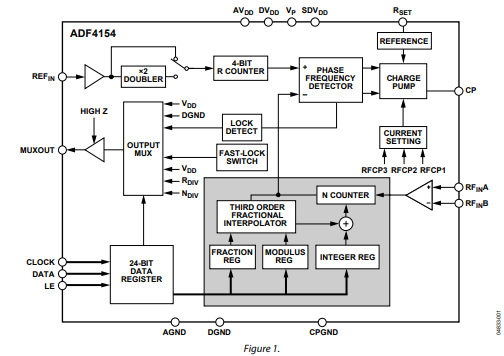

框圖

時序圖

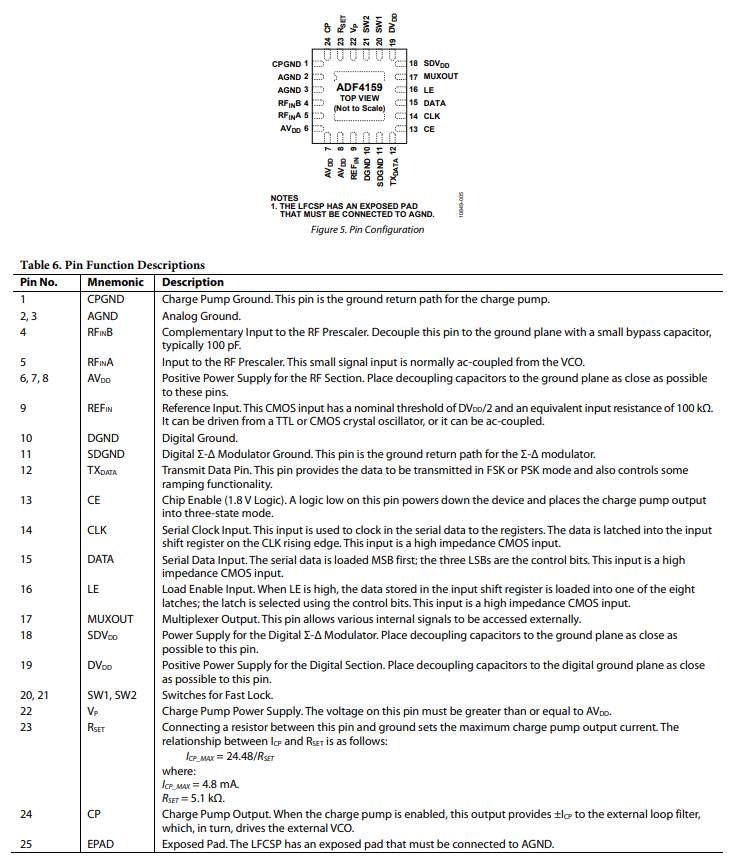

引腳配置描述

典型性能特征

參考輸入部分

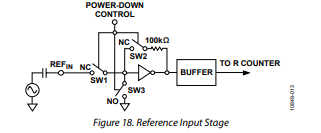

圖18展示了參考輸入級。SW1和SW2開關通常閉合(NC,常閉)。SW3開關通常斷開(NO,常開)。掉電時,SW3閉合,SW1和SW2斷開。這樣,在掉電期間,**REF_{IN}**引腳不會有負載。

射頻輸入級

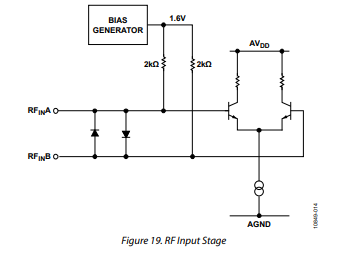

圖19展示了射頻輸入級。輸入級之后是兩級限幅放大器,用于生成預分頻器所需的電流模式邏輯(CML)時鐘電平。

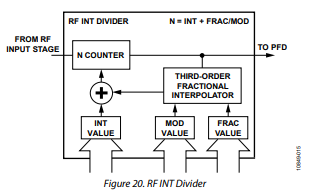

射頻整數分頻器(RF INT Divider)

射頻整數CMOS分頻器可在PLL反饋計數器中實現分頻比。允許的分頻比范圍為23至4095。

25位固定模數

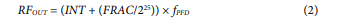

ADF4159具有25位固定模數。該模數可使輸出頻率間隔分辨率為

其中**f_{PFD}**是鑒頻鑒相器(PFD)的頻率。例如,若PFD頻率為100MHz,則頻率步長可達2.98Hz。由于Σ-Δ調制器的架構,VCO輸出上存在一個固定的 +(f_{PFD}/2^{25})偏移量。有關消除此偏移量的信息,請參見“Σ-Δ調制器模式”部分。

INT、FRAC和R計數器關系

INT和FRAC值與R計數器配合,能夠生成間隔為PFD頻率分數倍的輸出頻率。

射頻VCO頻率(RF_{OUT})公式為:

其中:

- **RF_{OUT}**是外部壓控振蕩器(VCO)的輸出頻率。

- INT是12位二進制計數器的預設分頻比(23至4095)。

- FRAC是分數除法的分子(0至$2^{25} - 1$)。

PFD頻率(f_{PFD})公式為:

其中:

- **REF_{IN}**是參考輸入頻率。

- D是**REF_{IN}**倍頻位(0或1)。

- R是5位二進制可編程參考(R)計數器的預設分頻比(1至32)。

- T是**REF_{IN}**二分頻位(0或1)。

R計數器

5位R計數器可對輸入參考頻率(REF_{IN})進行分頻,以產生PFD的參考時鐘。允許的分頻比范圍為1至32。

-

頻率合成器

+關注

關注

5文章

293瀏覽量

32705 -

PFD

+關注

關注

0文章

22瀏覽量

14581 -

ADF4159

+關注

關注

2文章

4瀏覽量

8993

發布評論請先 登錄

ADI推出業界最高性能PLL頻率合成器ADF4159

ADF4159 直接調制/快速波形產生13 GHz小數N分頻頻率合成器

無雜散、50 MHz 至 2.1 GHz 單通道小數 N 分頻頻率合成器 skyworksinc

ADF4159直接調制/快速波形產生13GHz小數N分頻頻率合成器技術手冊

ADF4159直接調制/快速波形產生13GHz小數N分頻頻率合成器技術手冊

評論