概述

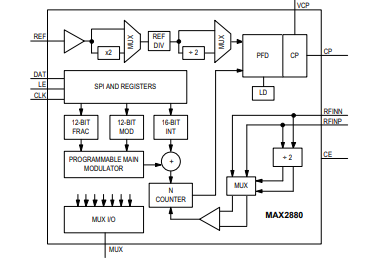

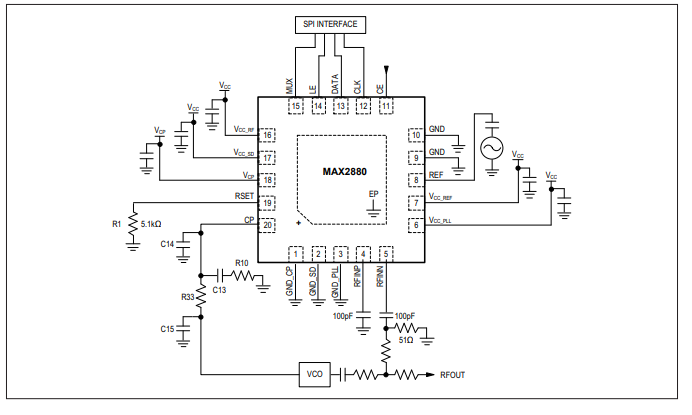

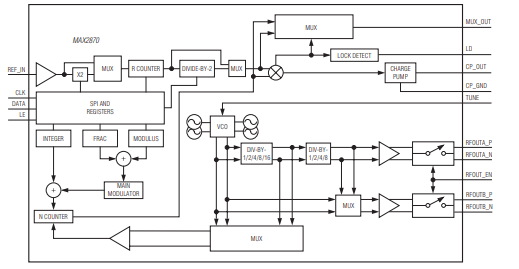

MAX2880為高性能鎖相環(PLL),提供整數或分數N分頻工作模式。器件配合外部參考時鐘振蕩器、環路濾波器和VCO,可以構成超低噪聲、低雜散頻率合成器,可接受高達12.4GHz的RF輸入。

MAX2880由高頻、低噪聲鑒頻器(PDF)、精密電荷泵、10位可編程參考時鐘計數器、16位整數N分頻計數器、12位可變模分數調制器。

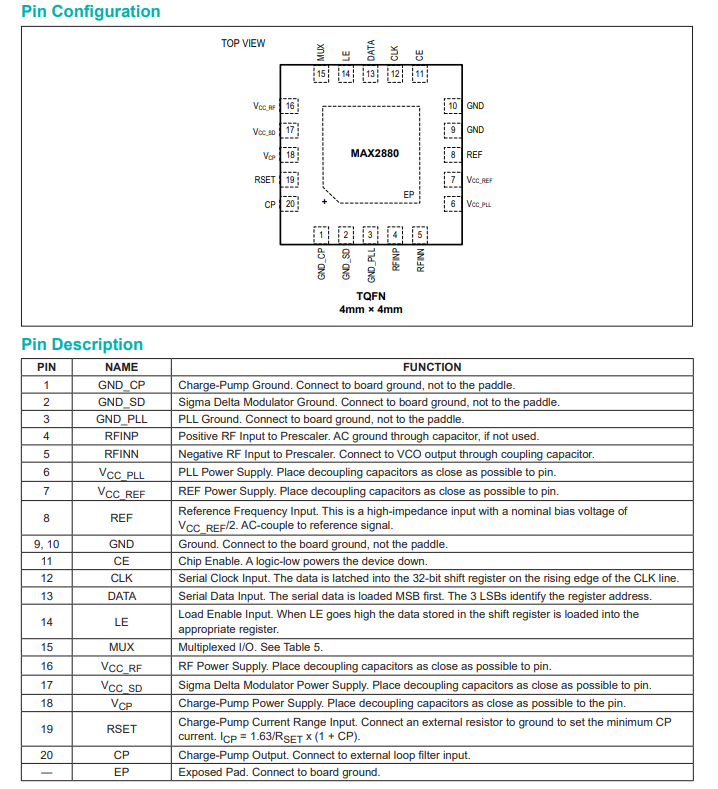

MAX2880通過3線串口控制,兼容于1.8V控制邏輯。器件采用無鉛、符合RoHS標準的20引腳TQFN封裝和16引腳TSSOP封裝,工作在-40°C至+85°C擴展級溫度范圍。

數據表:*附件:MAX2880 250MHz-12.4GHz、高性能、分數 整數型N分頻PLL技術手冊.pdf

應用

特性

- 整數/分數N分頻模式

- 250MHz至12.4GHz寬帶RF輸入

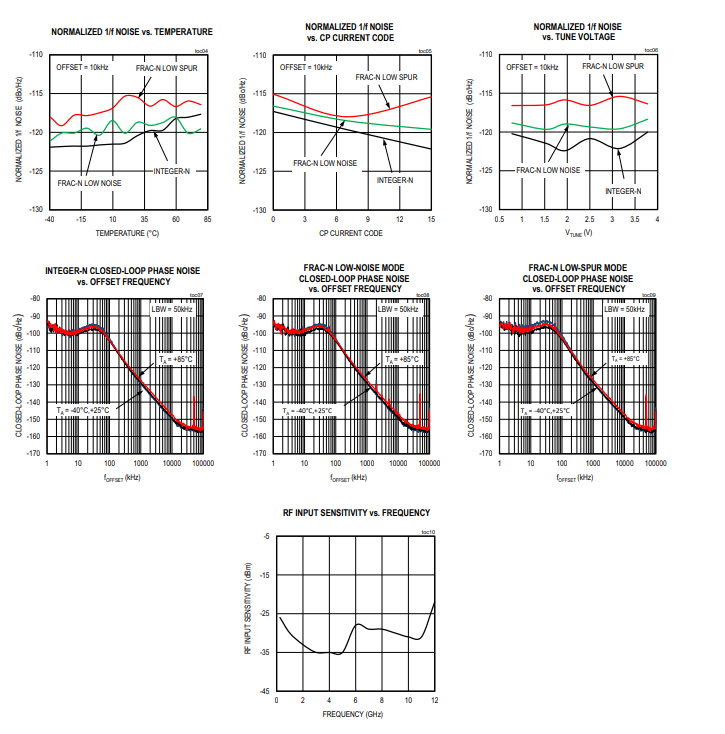

- 歸一化帶內噪底

- 整數模式:-229dBc/Hz

- 分數模式:-227dBc/Hz

- 較寬的輸入靈敏度:-10dBm至+5dBm

- 低噪聲鑒相器

- 分數模式:105MHz

- 整數模式:140MHz

- 參考時鐘頻率高達210MHz

- +2.8V至+3.6V供電

- 快速鎖存

- 軟件及硬件控制關斷

- 軟件鎖相檢測

- 片上溫度傳感器

- 兼容+1.8V控制邏輯

- 相位調節

框圖

典型操作特性

引腳配置描述

詳細說明

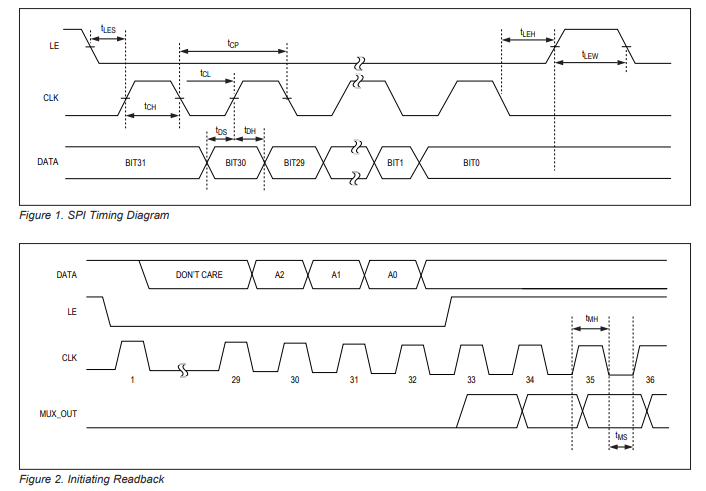

四線串行接口

MAX2880串行接口包含五個讀寫寄存器和一個只讀32位寄存器。29個最高有效位(MSB)是數據,三個最低有效位(LSB)是寄存器地址。寄存器在MSB優先的四線串行端口接口(SPI)上加載。

當使能引腳(LE)為邏輯低電平,時鐘(CLK)為邏輯高電平時,在CLK的上升沿移入數據。在LE的上升沿,29位數據鎖存到寄存器中,由地址位選擇。掉電時,默認值不能保證。上電后需對所有寄存器值進行編程。

寄存器編程順序應為地址0x04、0x03、0x02、0x01和0x00 。多個位采用雙緩沖,以便同時更新設置。有關雙緩沖設置的寄存器描述,請見相關內容。

任何寄存器都可通過MUX引腳回讀。用戶必須首先將MUX位設為1111。然后,寫入寄存器(先讀,且地址字節的READ位(位TSB) = 1 )。如果未設置READ位,30:3位的數據無關緊要,因為它們不會鎖存到寄存器中,也不參與讀操作。地址字節在CLK和LE引腳為邏輯高電平時鎖存。在CLK引腳的下一個上升沿之后,MUX引腳將在用戶的下28個時鐘上升沿之后改變。在LSB被讀取后,用戶應將MUX位重置為0000。

掉電模式

將SHDN設為1(寄存器3,位5 )或使CE引腳為邏輯低電平,可使MAX2880進入掉電模式。

應用電路

-

pll

+關注

關注

6文章

880瀏覽量

136018 -

VCO

+關注

關注

13文章

311瀏覽量

69961 -

分頻

+關注

關注

0文章

253瀏覽量

25080

發布評論請先 登錄

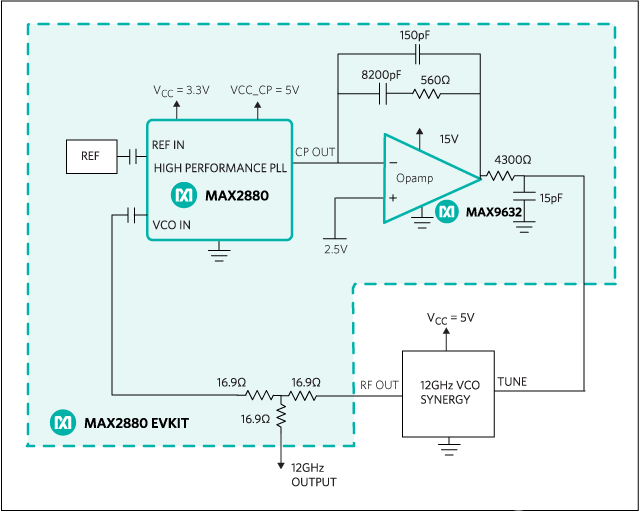

電源技巧#8:設計12GHz,超低相位噪聲(0.09 ps rms抖動)鎖相環

電源技巧#8:設計12GHz,超低相位噪聲(0.09 ps rms抖動)鎖相環

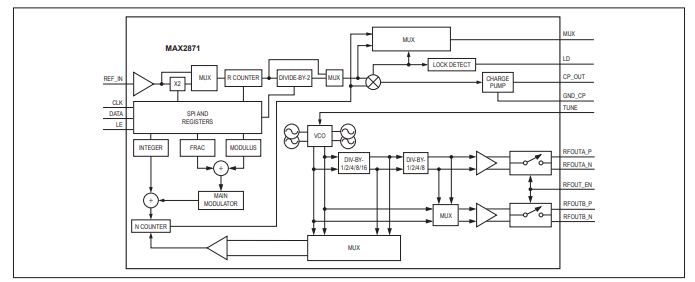

MAX2870 23.5MHz至6000MHz分數/整數N合成器和VCO

設計12GHz、超低相位噪聲(0.09 ps rms抖動)鎖相環

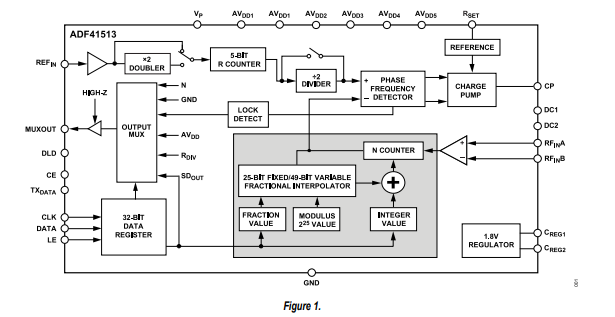

ADF41513 26.5GHz整數N/小數N PLL頻率合成器技術手冊

集成整數 N 分頻 PLL 和 VCO 的 350-5000 MHz 寬帶接收混頻器 skyworksinc

MAX2880 250MHz-12.4GHz、高性能、分數/整數型N分頻PLL技術手冊

MAX2880 250MHz-12.4GHz、高性能、分數/整數型N分頻PLL技術手冊

評論