本文翻譯轉(zhuǎn)載于:Cadence Blog

作者:Vinod Khera

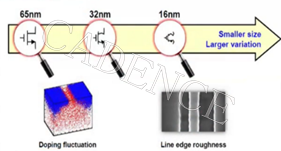

對于最新的微型半導(dǎo)體制作工藝而言,制程工藝變化和器件不匹配帶來了深遠(yuǎn)影響。復(fù)雜制程工藝也會影響器件生產(chǎn)的可變性,進(jìn)而影響整體良品率。 蒙特卡洛(MC)仿真使用重復(fù)的隨機(jī)抽樣方法,將工藝變化與電路性能和功能聯(lián)系起來,從而確定它們對良品率的影響。然而,要進(jìn)行全面的設(shè)計(jì)空間研究,設(shè)計(jì)團(tuán)隊(duì)需要完成大量的 MC 仿真才能達(dá)到必要的可信度。

一個芯片上的數(shù)十億個元件,再加上工藝變化和器件不匹配,我們能運(yùn)行數(shù)十億次統(tǒng)計(jì)仿真并耗費(fèi)大量時間進(jìn)行驗(yàn)證嗎?

運(yùn)行數(shù)百萬次甚至數(shù)十億次仿真所需的時間和運(yùn)算資源是不切實(shí)際的,因此,我們迫切需要在提高效能的同時滿足統(tǒng)計(jì)準(zhǔn)確度要求。使用 Cadence Spectre FMC Analysis,Broadcom 取得了良好的成果,并且顯著提升了生產(chǎn)力。此外,Spectre 仿真的多處理器模式在保證準(zhǔn)確度的同時進(jìn)一步縮短了運(yùn)行時間。本文將探討 Broadcom 借助 Spectre FMC 實(shí)現(xiàn)的準(zhǔn)確度和性能提升,內(nèi)容摘錄自 Broadcom 團(tuán)隊(duì)之前的 CadenceLIVE Silicon Valley 2024 演講。

為何制程工藝變化總是捉摸不定?

半導(dǎo)體代工廠通過開發(fā)統(tǒng)計(jì)模型來準(zhǔn)確形容器件級別的變化。這樣便可通過兼顧工藝變化的設(shè)計(jì)技術(shù)來最大程度降低集成電路(IC)故障的可能性。MC 仿真可使用這些統(tǒng)計(jì)模型來識別最壞情況并確保良品率符合預(yù)期。然而,這些仿真需要耗費(fèi)大量的計(jì)算資源和時間,對于芯片上經(jīng)常使用且具有低故障要求的設(shè)計(jì)模塊來說更是如此,例如標(biāo)準(zhǔn)單元、存儲位單元和模擬 IP(ADC、DAC、PLL 和帶隙基準(zhǔn)等)。

盡管仿真工具和大規(guī)模計(jì)算資源(如多核和云計(jì)算)方面已經(jīng)非常先進(jìn)了,執(zhí)行計(jì)算密集型 MC 仿真仍然不切實(shí)際,多數(shù)情況下根本不可能完成。對于高 sigma MC 分析來說更是如此,這里可能需要超過 10 億次仿真才能獲得高良品率。例如,用 25 億個樣本來確認(rèn)6σ。

為了在更少的仿真次數(shù)和更短的時間內(nèi)準(zhǔn)確估計(jì)良品率并判斷最壞情況,半導(dǎo)體行業(yè)需要使用 EDA 工具。要實(shí)現(xiàn)快速、精確的高 sigmaMC 分析,具有一流仿真能力的先進(jìn) EDA 解決方案必不可少。

解決方案:

Cadence Spectre FMC Analysis

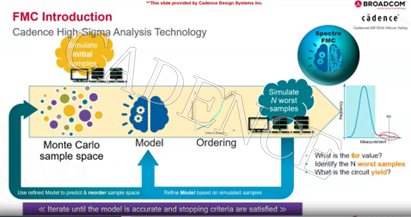

為了克服上述挑戰(zhàn),Cadence 開發(fā)了 Spectre FMC Analysis,將其作為 Spectre Simulation Platform 的一部分,引領(lǐng)行業(yè)步入高性能 SPICE 精確電路仿真。

它使用人工智能增強(qiáng)技術(shù),以便:

●在不影響統(tǒng)計(jì)準(zhǔn)確度的情況下,盡早、盡快地估計(jì)良品率

●發(fā)現(xiàn)統(tǒng)計(jì)異常值和最壞情況樣本

●與傳統(tǒng) MC 分析相比,在大幅度減少的仿真次數(shù)內(nèi)提取有用的統(tǒng)計(jì)信息

Broadcom 為何選擇采用

Spectre FMC Analysis?

Broadcom 需要的解決方案必須滿足以下要求:能夠準(zhǔn)確地測量和驗(yàn)證變化模型、具有成本效益并且能無縫整合進(jìn)現(xiàn)有的 IC 設(shè)計(jì)流程。此外,還必須具備可擴(kuò)展性,以滿足當(dāng)下和未來的設(shè)計(jì)需求。通過與 Cadence 合作,Broadcom 將 Spectre FMC Analysis 用于與時序相關(guān)的準(zhǔn)確度和分析項(xiàng)目中。

該產(chǎn)品為 Broadcom 帶來的好處包括:

●在高 sigma 下獲得高精度

●應(yīng)用現(xiàn)有 License Pool 的能力

●命令行界面 (CLI) 友好

●輕松整合進(jìn)現(xiàn)有的 IC 設(shè)計(jì)流程 Distributed processing

●分布式處理

●易于擴(kuò)展

●變化準(zhǔn)確度認(rèn)證

案例研究:

Non-Gaussian 分布

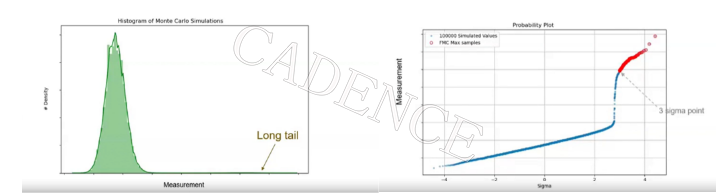

為了研究 Spectre FMC 的準(zhǔn)確度和性能,Broadcom 團(tuán)隊(duì)提出了一個具有 long tail 的案例,該案例不是嚴(yán)格的 Gaussian 分布。

結(jié)果表明,Spectre FMC 有能力處理這樣充滿挑戰(zhàn)的分布。通過對比傳統(tǒng) MC 和 Spectre FMC 的性能數(shù)據(jù),Broadcom 團(tuán)隊(duì)獲得了更大的信心。

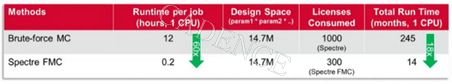

如果不使用 Spectre FMC Analysis,處理每個作業(yè)需要 12 小時,總運(yùn)行時間約為 245 個月的 CPU 時間,需要使用 1000 個 Spectre License。使用 Spectre FMC,每個作業(yè)平均需要 0.2 小時左右,需要使用 300 個 Spectre License,總 CPU 時間也縮短為 14 個月。在 Spectre FMC Analysis 的助力下,Broadcom 在一個月左右的時間內(nèi)完成了該項(xiàng)目,證明該產(chǎn)品能夠帶來顯著的性能提升。

Cadence Spectre FMC 優(yōu)勢

在與 Broadcom 現(xiàn)有 IC 設(shè)計(jì)流程無縫整合的同時,Spectre FMC 還大大提高了準(zhǔn)確度和性能。在適當(dāng)?shù)脑S可條件下運(yùn)行時,Broadcom 每個 CPU 處理每個作業(yè)的效率提升 60 倍左右。即便減少 License 的數(shù)量,該產(chǎn)品帶來的優(yōu)勢仍然十分顯著,整體性能大約提高了 18 倍。Broadcom 提到,使用 Spectre FMC 的主要優(yōu)勢在于提升精確度和顯著縮短運(yùn)行時間。確保有足夠的 License Pool 至關(guān)重要。此外,該產(chǎn)品的命令行簡單易用,且具有強(qiáng)大的可擴(kuò)展性,非常適合用于高效探索整個設(shè)計(jì)空間。

-

集成電路

+關(guān)注

關(guān)注

5420文章

11947瀏覽量

367137 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28599瀏覽量

232518 -

Cadence

+關(guān)注

關(guān)注

67文章

964瀏覽量

143829 -

制程工藝

+關(guān)注

關(guān)注

0文章

46瀏覽量

9551

原文標(biāo)題:Broadcom 使用 Spectre FMC(Fast-MC)快速蒙特卡羅 進(jìn)行時序變化分析

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

DDR3內(nèi)存的PCB仿真與設(shè)計(jì)

如何利用FPGA進(jìn)行時序分析設(shè)計(jì)

tcl命令用于時序分析如何檢查輸入或輸出的時間?

時序計(jì)算和Cadence仿真結(jié)果的運(yùn)用

Cadence PCB SI分析特性阻抗變化因素教程

靜態(tài)時序分析基礎(chǔ)及應(yīng)用

在進(jìn)行時序分析時為什么CPR操作得出的效果卻是相反的?

Vivado進(jìn)行時序約束的兩種方式

SK部署Cadence仿真器進(jìn)行FastSPICE功能驗(yàn)證

DB GlobalChip有效運(yùn)用Cadence的Spectre FX和AMS Designer,將IP驗(yàn)證速度加快2倍

使用IBIS模型進(jìn)行時序分析

Broadcom使用Cadence Spectre FMC Analysis進(jìn)行時序變化分析

Broadcom使用Cadence Spectre FMC Analysis進(jìn)行時序變化分析

評論