近日,作為國內(nèi)領先的系統(tǒng)級驗證EDA解決方案提供商,芯華章分別攜手飛騰信息技術、中興微電子在IC設計驗證領域最具影響力的會議DVCon China進行聯(lián)合演講,針對各個場景下驗證中的“硬骨頭”問題,用實際案例詮釋“AI+EDA”如何重塑驗證效率,讓大家實實在在的看見國產(chǎn)驗證EDA技術落地的扎實與生態(tài)協(xié)同創(chuàng)新的力量。

破解復雜算子驗證困局

從 “高門檻” 變 “高效能”

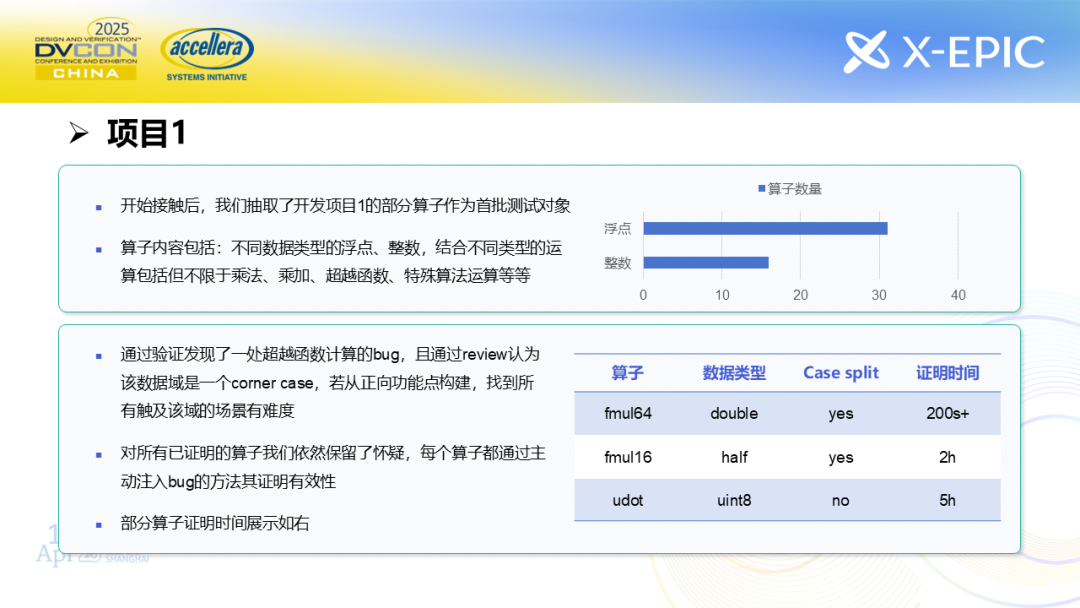

在高性能CPU與AI芯片設計中,浮點運算、矩陣乘等復雜算子的驗證長期面臨“覆蓋不全、效率低下”的挑戰(zhàn)。傳統(tǒng)仿真方法難以窮舉海量邊界條件,而手動形式化驗證的高門檻讓眾多團隊望而卻步。

芯華章與飛騰聯(lián)合攻關,將AI算法深度融入芯華章GalaxEC-HEC高階等價性驗證工具,通過智能案例拆分與數(shù)學化證明引擎,實現(xiàn)了從算法級到RTL級的精準映射——雙精度乘加算子證明時間從89小時降至11小時,單精度乘加從86小時壓縮至1小時。

這一突破在飛騰某國產(chǎn)CPU項目中轉化為實實在在的工程價值:在沒有增加太多人力資源的情況下,實現(xiàn)了將近9倍于項目1算子數(shù)量的證明。

飛騰高級IC設計工程師鄭帥克表示,“芯華章GalaxEC-HEC不僅提升了驗證效率,更在AI的加持下實現(xiàn)了全算子‘精準掃描’,它讓我們從依賴經(jīng)驗篩選驗證重點轉向數(shù)據(jù)驅(qū)動全場景覆蓋,為國產(chǎn) CPU 的自主創(chuàng)新筑牢根基。”

LLM 讓復雜斷言生成

從 “人工苦旅” 走向 “智能生成”

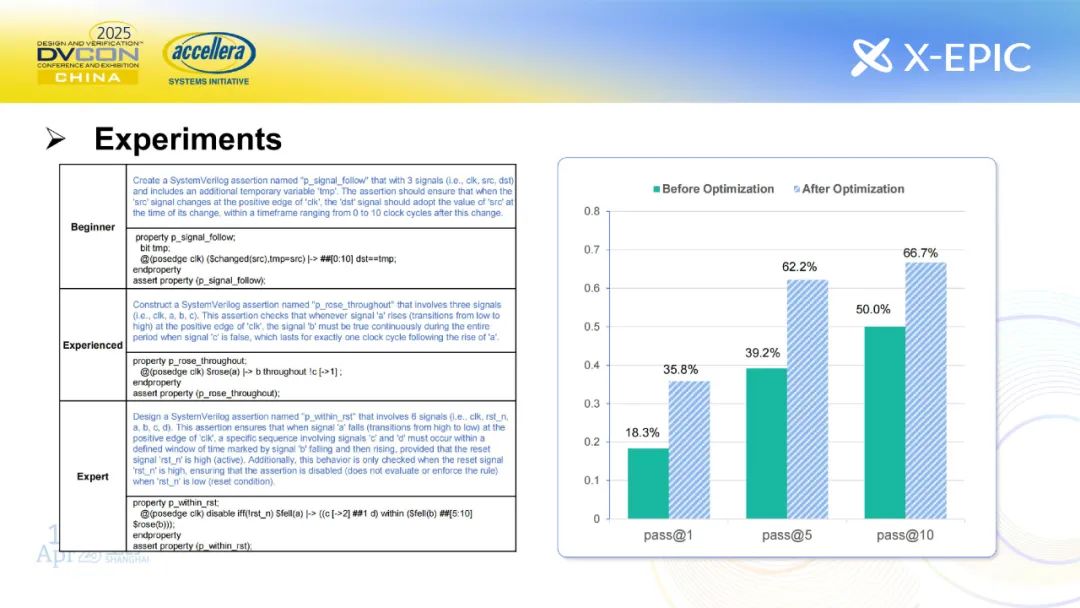

SystemVerilog 斷言(SVA)在形式屬性驗證(FPV)中對于確保設計的正確性至關重要,但復雜時序邏輯的手工編寫耗時耗力,且容易因邊界條件遺漏導致驗證漏洞。

芯華章與中興微電子瞄準這一痛點,聯(lián)合研發(fā)基于大語言模型(LLM)的SVA生成并引入工業(yè)級創(chuàng)新評估系統(tǒng)SVAEval。該框架通過迭代式提示優(yōu)化和指標評估,顯著提升了由大型語言模型生成的 SVA 的質(zhì)量。

在真實項目驗證中,該系統(tǒng)展現(xiàn)出強大的場景適配能力:面對“信號變化后10 周期內(nèi)目標信號匹配”、“異步時鐘域斷言同步”等復雜需求,可自動生成包含臨時變量、時間窗口及跨時鐘域處理的斷言代碼,覆蓋傳統(tǒng)手動編寫易遺漏的20%以上邊界場景。

中興微電子研發(fā)團隊實測顯示,pass5@較基線提升59%,復雜斷言開發(fā)效率提升40%以上,原本需要3天的調(diào)試周期縮短至數(shù)小時。

中興微電子IC驗證經(jīng)理商思航指出,“通過自動化 SVA 的生成和評估,我們顯著提升了大語言模型生成SVA的質(zhì)量,大幅減少了驗證工程師耗時耗力的SVA編寫工作。同時也讓驗證工程師能夠?qū)⒕劢褂谠O計規(guī)范的深度分析和邊界驗證條件挖掘,避免過多關注SVA語法自身,降低了人工成本,大大提升了驗證效率。”

在深度融合項目實踐中,芯華章將技術洞察、創(chuàng)新經(jīng)驗及技術突破進行系統(tǒng)化沉淀。此次,芯華章分別與中興微電子、EDA國創(chuàng)中心合作發(fā)布《LLM based SVA Generation with Formal Evaluation》、《Automated SVA Generation with LLMs》,兩篇研究成果成功入選2025 DVCon China論文。

這些研究成果錨定AI驅(qū)動驗證技術前沿,既深入解析復雜斷言生成系統(tǒng)如何借助LLM實現(xiàn)效率突破的技術細節(jié),也全面探討國產(chǎn)大模型在EDA領域規(guī)模化應用的方法論,為行業(yè)貢獻了可復用的技術路徑與實踐參考。

協(xié)同創(chuàng)新夯實產(chǎn)業(yè)生態(tài)

把握 AI 機遇,共創(chuàng)差異化價值

AI的快速發(fā)展與廣泛應用,催生了對算力、功耗優(yōu)化的多元需求。在AI算力需求爆發(fā)、存儲技術迭代、系統(tǒng)架構多元化的行業(yè)趨勢下,底層芯片產(chǎn)業(yè)鏈正經(jīng)歷深度創(chuàng)新,市場也迎來了更豐富的發(fā)展機遇。對芯華章而言,AI帶來的機遇遠不止于工具層面的突破,更在于與客戶建立深度協(xié)同、實現(xiàn)價值共創(chuàng)的契機。

差異化價值的創(chuàng)造,核心在于深度理解客戶需求并實現(xiàn)技術落地的精準匹配。芯華章始終將客戶需求作為技術創(chuàng)新的起點:無論是算子驗證時追求 “算透”,還是斷言生成時力求 “精準”,亦或是通過智能優(yōu)化仿真速度、精準定位調(diào)試問題,讓每一項技術探索始終緊貼產(chǎn)業(yè)一線痛點展開,讓每一次創(chuàng)新都經(jīng)過實際項目的打磨。

未來,芯華章將持續(xù)探索“AI+EDA”創(chuàng)新路徑,與客戶共同研發(fā)適配其技術路線的驗證方案,為客戶提供更加高效、可靠的驗證解決方案,實現(xiàn)從需求響應到價值共創(chuàng)的跨越。

-

AI

+關注

關注

88文章

35136瀏覽量

279716 -

芯片驗證

+關注

關注

5文章

40瀏覽量

47629 -

飛騰

+關注

關注

2文章

325瀏覽量

13725 -

芯華章

+關注

關注

0文章

182瀏覽量

11645

原文標題:攜手飛騰、中興,芯華章以AI驅(qū)動驗證創(chuàng)新,直擊芯片驗證“效率之痛”

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

芯華章攜手EDA國創(chuàng)中心推出數(shù)字芯片驗證大模型ChatDV

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預測......

國內(nèi)EDA大廠芯華章換將,聚焦發(fā)展,戰(zhàn)略升級

全球的AI+EDA(電子設計自動化)創(chuàng)新項目

芯華章謝仲輝:國產(chǎn)EDA以市場為導向,以客戶價值為重

芯華章持續(xù)助力EDA精英挑戰(zhàn)賽

芯華章發(fā)布FPGA驗證系統(tǒng)新品HuaProP3

芯華章發(fā)布新一代FPGA原型驗證系統(tǒng)HuaPro P3

芯華章推出新一代高性能FPGA原型驗證系統(tǒng)

國產(chǎn)EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統(tǒng)

芯華章以AI+EDA重塑芯片驗證效率

芯華章以AI+EDA重塑芯片驗證效率

評論