面向國(guó)家在集成電路EDA領(lǐng)域的重大需求,芯華章攜手全國(guó)首家集成電路設(shè)計(jì)領(lǐng)域國(guó)家級(jí)創(chuàng)新中心——EDA國(guó)創(chuàng)中心,針對(duì)日益突出的芯片設(shè)計(jì)驗(yàn)證痛點(diǎn),強(qiáng)強(qiáng)聯(lián)手,共同推出具有完全自主知識(shí)產(chǎn)權(quán)的基于LLM的數(shù)字芯片驗(yàn)證大模型ChatDV。

立足技術(shù)創(chuàng)新與產(chǎn)品服務(wù),芯華章已經(jīng)在系統(tǒng)級(jí)驗(yàn)證領(lǐng)域建立起完整的數(shù)字驗(yàn)證全流程工具鏈,擁有超200件專利申請(qǐng),服務(wù)包括芯擎科技、黑芝麻、燧原科技、飛騰、中科院軟件所、天數(shù)智芯、芯來科技、加特蘭微電子、鯤云科技、曦智科技等數(shù)十家業(yè)內(nèi)知名企業(yè)。

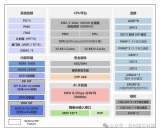

為打造“數(shù)字芯片驗(yàn)證智能體”,EDA國(guó)創(chuàng)中心審慎評(píng)估后,選用芯華章GalaxSim高性能邏輯仿真工具用于大模型生成代碼的仿真驗(yàn)證,以及GalaxFV形式化驗(yàn)證工具用于針對(duì)故障代碼的反例數(shù)據(jù)收集,將AI技術(shù)與設(shè)計(jì)驗(yàn)證深度融合,革新了傳統(tǒng)芯片驗(yàn)證各個(gè)環(huán)節(jié)的工作模式。

芯華章GalaxSim在性能上已經(jīng)和國(guó)際主流仿真器相當(dāng),并原生支持鯤鵬、飛騰等國(guó)產(chǎn)服務(wù)器,且已在多個(gè)基于ARM平臺(tái)的國(guó)產(chǎn)構(gòu)架上測(cè)試通過。

芯華章與中興微電子聯(lián)合研發(fā)基于大語言模型(LLM)的SVA生成,打造出具有差異化優(yōu)勢(shì)產(chǎn)品GalaxFV,解決在高性能處理器芯片設(shè)計(jì)中,復(fù)雜時(shí)序邏輯的手工編寫耗時(shí)耗力、容易因邊界條件遺漏導(dǎo)致驗(yàn)證漏洞的問題。在中興微的項(xiàng)目實(shí)測(cè)中,該系統(tǒng)展現(xiàn)出強(qiáng)大的場(chǎng)景適配能力,且復(fù)雜斷言開發(fā)效率提升40%以上,原本需要3天的調(diào)試周期縮短至數(shù)小時(shí)。

在深度融合項(xiàng)目實(shí)踐中,芯華章與中興微電子、EDA國(guó)創(chuàng)中心合作發(fā)布《LLM based SVA Generation with Formal Evaluation》、《Automated SVA Generation with LLMs》,兩篇研究成果成功入選2025 DVCon China論文。這些研究成果錨定AI驅(qū)動(dòng)驗(yàn)證技術(shù)前沿,既深入解析復(fù)雜斷言生成系統(tǒng)如何借助LLM實(shí)現(xiàn)效率突破的技術(shù)細(xì)節(jié),也全面探討國(guó)產(chǎn)大模型在EDA領(lǐng)域規(guī)模化應(yīng)用的方法論,為行業(yè)貢獻(xiàn)了可復(fù)用的技術(shù)路徑與實(shí)踐參考。

以芯華章驗(yàn)證技術(shù)為底層引擎,ChatDV能夠自動(dòng)完成斷言SVA、測(cè)試向量TB、參照模型Reference Model的生成以及RTL代碼錯(cuò)誤自動(dòng)調(diào)試,使芯片開發(fā)效率提升超過10倍,驗(yàn)證成本降低10倍。在英偉達(dá)等學(xué)術(shù)與工業(yè)級(jí)測(cè)試中,ChatDV表現(xiàn)卓越,在超300個(gè)基準(zhǔn)上實(shí)現(xiàn)語法糾錯(cuò)率100%,功能糾錯(cuò)率83%。

對(duì)芯華章而言,AI帶來的機(jī)遇遠(yuǎn)不止于工具層面的突破,更在于與客戶建立深度協(xié)同、實(shí)現(xiàn)價(jià)值共創(chuàng)的契機(jī)。未來,芯華章將持續(xù)提供更加高效、可靠的驗(yàn)證解決方案,攜手合作伙伴,讓芯片驗(yàn)證EDA成為國(guó)產(chǎn)差異化優(yōu)勢(shì)領(lǐng)域。

關(guān)于EDA國(guó)創(chuàng)中心

國(guó)家集成電路設(shè)計(jì)自動(dòng)化技術(shù)創(chuàng)新中心(簡(jiǎn)稱EDA國(guó)創(chuàng)中心)是經(jīng)科技部于2022年12月批準(zhǔn)成立的我國(guó)集成電路設(shè)計(jì)領(lǐng)域首個(gè)國(guó)家級(jí)技術(shù)創(chuàng)新中心。中心聚焦下一代電子設(shè)計(jì)自動(dòng)化(EDA)技術(shù)突破,以"智能EDA——計(jì)算一切電路"為理念,合成海量集成電路設(shè)計(jì)數(shù)據(jù),研制電路生成專用工具,創(chuàng)新基于AI大模型的集成電路設(shè)計(jì)新范式,賦能集成電路設(shè)計(jì)產(chǎn)業(yè)。

-

集成電路

+關(guān)注

關(guān)注

5420文章

11955瀏覽量

367221 -

eda

+關(guān)注

關(guān)注

71文章

2893瀏覽量

176506 -

數(shù)字芯片

+關(guān)注

關(guān)注

1文章

113瀏覽量

18715 -

芯華章

+關(guān)注

關(guān)注

0文章

180瀏覽量

11571

原文標(biāo)題:開放試用 | 芯華章助力EDA國(guó)創(chuàng)中心打造數(shù)字芯片驗(yàn)證大模型

文章出處:【微信號(hào):X-EPIC,微信公眾號(hào):芯華章科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

芯華章以AI+EDA重塑芯片驗(yàn)證效率

國(guó)芯科技與美電科技攜手推出AI傳感器模組

國(guó)內(nèi)EDA大廠芯華章換將,聚焦發(fā)展,戰(zhàn)略升級(jí)

芯華章持續(xù)助力EDA精英挑戰(zhàn)賽

芯華章發(fā)布FPGA驗(yàn)證系統(tǒng)新品HuaProP3

芯華章發(fā)布新一代FPGA原型驗(yàn)證系統(tǒng)HuaPro P3

芯華章推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

國(guó)產(chǎn)EDA公司芯華章科技推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

芯華章獲評(píng)國(guó)家級(jí)專精特新“小巨人”企業(yè)

思爾芯攜手騰訊云,以EDA云服務(wù)賦能芯片設(shè)計(jì),共促數(shù)字經(jīng)濟(jì)

華中科技大學(xué)集成電路學(xué)院一行走訪EDA廠商芯華章

芯華章致力于打造完整的數(shù)字驗(yàn)證全流程工具

芯華章與華大九天推出數(shù)模混合仿真解決方案,引領(lǐng)EDA生態(tài)新篇章

芯華章生態(tài)戰(zhàn)略亮相DAC,發(fā)布全流程敏捷驗(yàn)證管理器FusionFlex,并聯(lián)合華大九天推出數(shù)模混合仿真解決方案

芯華章推出EDA全流程敏捷驗(yàn)證管理器昭睿FusionFlex

芯華章攜手EDA國(guó)創(chuàng)中心推出數(shù)字芯片驗(yàn)證大模型ChatDV

芯華章攜手EDA國(guó)創(chuàng)中心推出數(shù)字芯片驗(yàn)證大模型ChatDV

評(píng)論