概述

AD800和AD802采用二階鎖相環結構,對不歸零(NRZ)數據執行時鐘恢復和數據重定時。這種結構可支持20 Mbps至160 Mbps范圍內的數據速率。此處所述的產品規定以標準電信比特率工作。AD800-45和AD800-52分別支持45 Mbps DS-3和52 Mbps STS-1。AD802-155支持155 Mbps STS-3或STM-1。

數據表:*附件:AD800 45或52 Mbps時鐘和數據恢復IC技術手冊.pdf

與其它基于PLL的時鐘恢復電路不同,這些器件不需要前同步碼或外部VCXO來鎖定輸入數據。電路利用兩個控制環路采集頻率和相位鎖定。首先由頻率采集控制環路采集輸入數據的時鐘頻率,然后由鎖相環采集輸入數據的相位,并確保輸出信號相位跟蹤輸出數據相位的變化。電路的環路阻尼取決于用戶所選電容的值;它決定抖動峰值和性能,并影響采集時間。這些器件的抖動峰值為0.08 dB;當阻尼系數為5時,可以在4 X 10^5^ 位周期內鎖定隨機或加擾數據。

在采集過程中,鑒頻器提供一個頻率采集(FRAC)信號,指示器件尚未鎖定輸入數據。此信號是一系列脈沖,出現在輸入數據與同步時鐘信號之間的周跳點。一旦電路采集到頻率鎖定,FRAC輸出就不會出現脈沖。

器件中內置經過精密調整的VCO,不需要用于設置中心頻率的外部器件,從而也不需要對這些器件進行調整。無輸入數據時,VCO提供器件中心頻率±20%范圍內的時鐘輸出。

取得專利的鑒相器具有出色的性能,因而AD800和AD802幾乎沒有碼抖動。總環路抖動為20°峰峰值。抖動帶寬由掩模可編程小數環路帶寬決定。AD800用于90 Mbps以下的數據速率,標稱環路帶寬為中心頻率的0.1%。AD802用于90 Mbps以上的數據速率,環路帶寬為中心頻率的0.08%。

所有器件均采用+5 V或-5.2 V單電源供電。

特性

- 標準產品

44.736 Mbps—DS-3

51.84 Mbps—STS-1

155.52 Mbps—STS-3 或STM-1 - 接受NRZ數據,無需前同步碼

- 恢復時鐘和重定時數據輸出

- 鎖相環型時鐘恢復,無需晶振

- 隨機抖動:20°峰峰值

- 碼抖動:幾乎消除

- 兼容10KH ECL

- 單電源供電:–5.2 V或+5 V

- 寬工作溫度范圍:–40°C至+85°C

特性

- 標準產品

44.736 Mbps—DS-3

51.84 Mbps—STS-1

155.52 Mbps—STS-3 或STM-1 - 接受NRZ數據,無需前同步碼

- 恢復時鐘和重定時數據輸出

- 鎖相環型時鐘恢復,無需晶振

- 隨機抖動:20°峰峰值

- 碼抖動:幾乎消除

- 兼容10KH ECL

- 單電源供電:–5.2 V或+5 V

- 寬工作溫度范圍:–40°C至+85°C

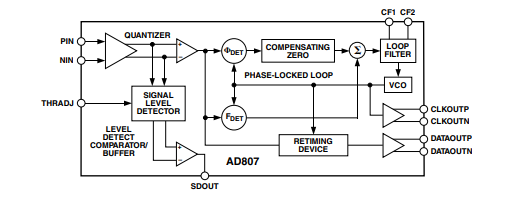

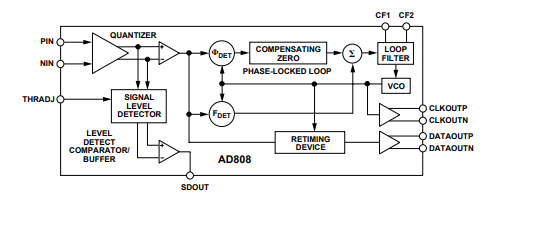

框圖

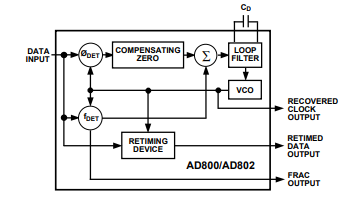

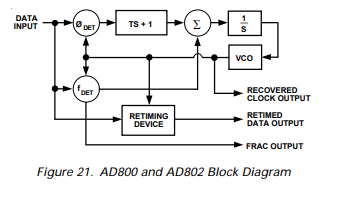

AD800 和 AD802 是用于從不歸零制(NRZ)數據中恢復時鐘的鎖相環電路。其架構采用頻率檢測器來實現初始頻率捕獲,相關方框圖見圖 21。需注意,頻率檢測器始終處于工作狀態。當鎖相環(PLL)鎖定時,頻率檢測誤差為零,且頻率檢測器不再產生影響。由于頻率檢測器內置于電路中,因此無需額外的控制功能來啟動捕獲或改變捕獲模式。

頻率檢測器還提供一個頻率獲取輸出(FRAC),用于指示鎖相環何時處于捕獲狀態。在捕獲過程中,FRAC 輸出是一系列寬度等于壓控振蕩器(VCO)周期的脈沖。這些脈沖在數據轉換時出現。當 VCO 頻率與最大密度(1010…)數據模式的頻率匹配時,每次循環滑動都會在 FRAC 處產生一個脈沖。然而,對于隨機數據,并非每次循環滑動都會在 FRAC 處產生脈沖。不過,FRAC 處的脈沖密度會隨著數據轉換的密度增加而增加。隨著頻率誤差趨近于零,每個周期滑動產生脈沖的概率增加。當頻率誤差降為零后,FRAC 輸出將不再有脈沖。此時,PLL 開始進入相位捕獲階段,在此設置下,大約需要 2000 個位周期才能保證數據恢復有效。等待 2000 個位周期后,最終的 FRAC 脈沖就會出現。

通過使用一種新的相位誤差(專利技術),由數據轉換密度變化(模式抖動)引起的抖動實際上被消除了。簡而言之,測量得到的相位誤差不會導致 VCO 相位增加,從而使平均運行速率由數據頻率決定。所產生的抖動由 2??1 偽隨機碼決定,其抖動幅度為 1/2 度,與隨機抖動相比幅度較小。

AD802 - 155 的抖動帶寬為中心頻率的 0.08%。選擇該參數是為了使 130 kHz 處的固有輸入抖動衰減 3 dB。AD800 - 45 和 AD800 - 52 的抖動帶寬分別為各自中心頻率的 0.1%。AD800 或 AD802 的抖動掩碼可編程范圍為中心頻率的 0.01% - 1%。一個具有極低帶寬(0.01% 中心頻率)的器件能夠有效地過濾(凈化)抖動定時參考。如果您的應用需要特殊的環路帶寬,請咨詢工廠。

鎖相環的阻尼比可通過單個外部電容器由用戶編程。在 155 MHz 時,使用 0.22 μF 電容器可獲得 10 的阻尼比。一般來說,阻尼比與 √(f_DATAC_D)成正比。在 155 MHz 時,使用 2.2 nF 電容器可獲得 1 的阻尼比。較低的阻尼比允許更快的頻率捕獲;通常,捕獲時間與電容值直接成比例。然而,當阻尼比接近 1 時,捕獲時間不再直接與電容值相關。捕獲時間包含兩個部分:頻率捕獲和相位捕獲。頻率捕獲始終與電容值成比例,但相位捕獲由鎖相環帶寬決定,且與阻尼比無關。因此,0.08% 的鎖相環帶寬可設定最小捕獲時間為 15000 個位周期。注意,阻尼因子為 1 時的捕獲時間規定為 15000 個位周期,其中 13000 個位周期用于頻率捕獲,2000 個周期用于相位捕獲。將此與阻尼比為 5 時規定的 400000 個位周期的捕獲時間進行比較;此時完全是頻率捕獲,相位捕獲的 2000 個位周期可忽略不計。

雖然較低的阻尼比可加快捕獲速度,但它也會增加抖動傳輸響應(抖動峰值)。例如,對于阻尼比為 10 的情況,抖動峰值為 0.02 dB,但對于阻尼因子為 1 的情況,抖動峰值為 2 dB。

-

定時

+關注

關注

1文章

124瀏覽量

25794 -

時鐘

+關注

關注

11文章

1883瀏覽量

132845 -

數據恢復

+關注

關注

10文章

637瀏覽量

18012

發布評論請先 登錄

AD800 45或52 Mbps時鐘和數據恢復IC

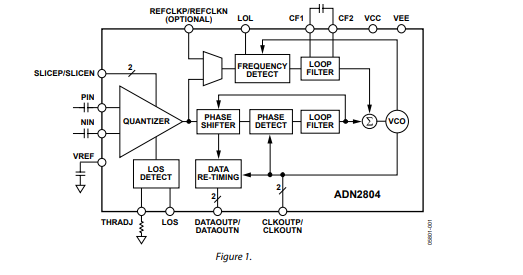

ADN2804:帶集成限幅放大器的622 Mbps時鐘和數據恢復IC產品說明書

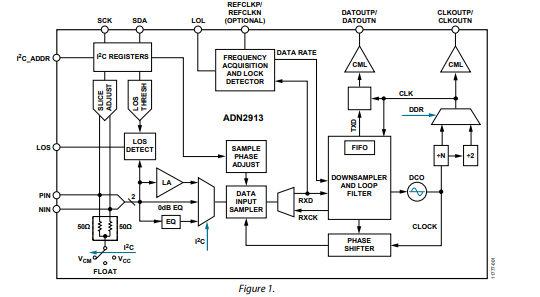

ADN2913:連續速率6.5 Mbps至8.5 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器數據表

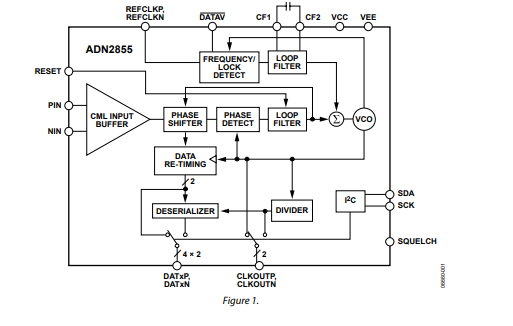

ADN2855:多速率155 Mbps/622 Mbps/1244 Mbps/1250 Mbps突發模式時鐘和數據恢復IC,帶解串器產品手冊

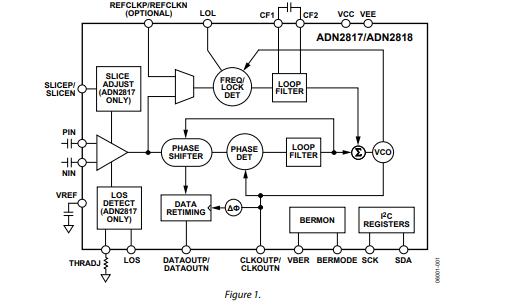

ADN2817/ADN2818:連續速率10 Mbps至2.7 Gbps時鐘和數據恢復IC數據表

ADN2913連續速率6.5 Mbps至8.5 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器技術手冊

ADN2855多速率155 Mbps/622 Mbps/1244 Mbps/1250 Mbps突發模式時鐘和數據恢復IC技術手冊

ADN2817連續速率10 Mbps至2.7 Gbps時鐘和數據恢復IC技術手冊

AD800 45或52 Mbps時鐘和數據恢復IC技術手冊

AD800 45或52 Mbps時鐘和數據恢復IC技術手冊

評論