概述

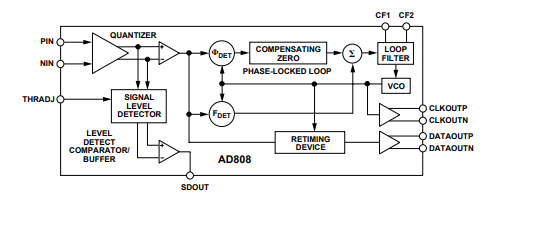

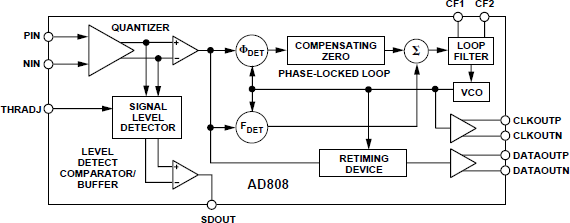

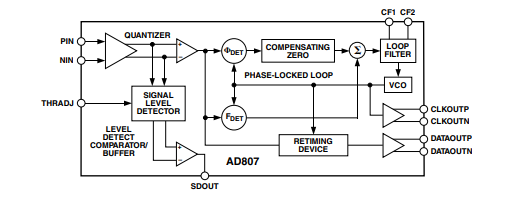

AD808可提供四種接收器功能:數(shù)據(jù)量化、信號電平檢測、時鐘恢復和數(shù)據(jù)重定時,適用于622 Mbps NRZ數(shù)據(jù)。該器件連同PIN二極管/前置放大器組合,可以用于高度集成、低成本、低功耗SONET OC-12或SDH STM-4光纖接收器。

數(shù)據(jù)表:*附件:AD808 622MBPS、低功耗、后置放大器 時鐘和數(shù)據(jù)恢復IC技術(shù)手冊.pdf

特性

- 滿足CCITT G.958 STM-4再生器—A型要求

- 滿足Bellcore TR-NWT-000253 OC-12要求

- 輸出抖動:2.5°(均方根)

- 622 Mbps 時鐘恢復和數(shù)據(jù)重定時

- 接受NRZ數(shù)據(jù),無需前同步碼

- 鎖相環(huán)型時鐘恢復,無需晶振

- 量化器靈敏度:4 mV

- 電平檢測范圍:10 mV至40 mV,可編程

- 單電源供電:+5 V或–5.2 V

- 低功耗:400 mW

- 10 KH ECL/PECL 兼容輸出

- 封裝:16引腳窄體150 Mil SOIC

框圖

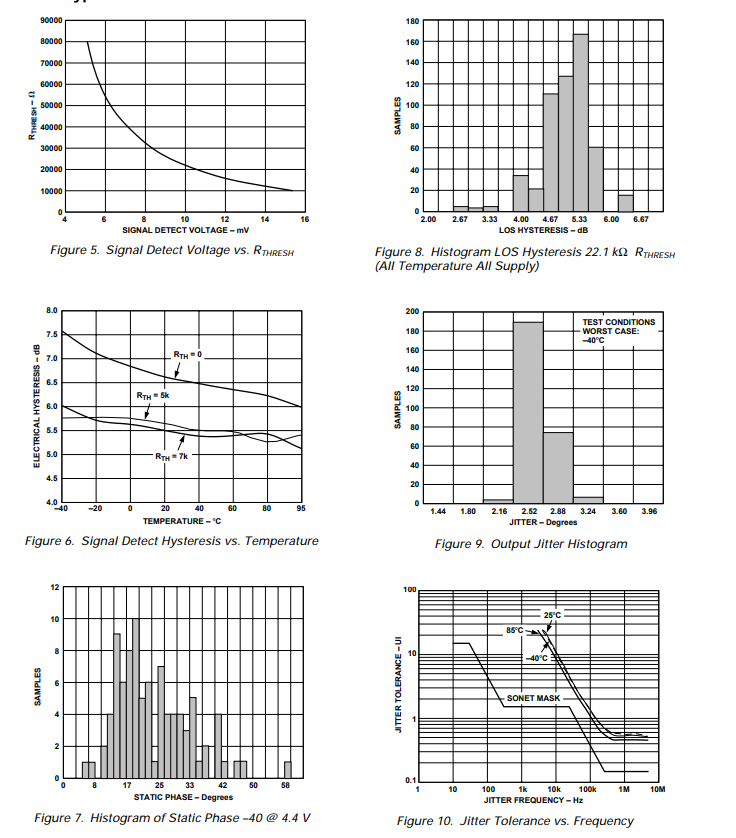

ad 808–典型性能特征

量化器

量化器(比較器)有三級增益,總增益為 350。量化器利用額外快速互補雙極(XFCB)工藝。輸入級是一個寬帶寬跨導放大器,可處理大信號且無失真,以應對輸入信號的共模電壓較高的情況。輸入失調(diào)電壓由工廠調(diào)整,通常小于 1 mV。XFCB 工藝使輸入信號之間實現(xiàn)了良好的隔離,因此可實現(xiàn) 4 mV 峰峰值靈敏度。傳統(tǒng)上,高速比較器會因輸出與輸入之間的串擾而受到影響,導致輸入信號接近 10 mV 時出現(xiàn)振蕩。ADN2813 輸入信號范圍可達 100 mV,且在不使輸入信號過載的情況下可處理低至 2 mV 的輸入信號,電路性能主要受輸入噪聲影響,且無擊穿現(xiàn)象。

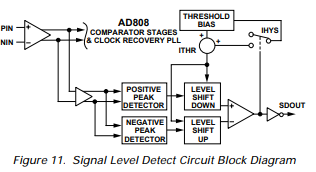

信號檢測

信號檢測電路的輸入來自量化器的第一級增益。該增益級的輸出同時輸入到正峰值檢測器和負峰值檢測器。將正峰值信號與負峰值信號相加,然后與閾值進行比較。如果正峰值、負峰值之和大于閾值,NEG 信號幅度將指示輸入信號的存在,此時 SDOUT 將指示 LOS 信號(低于閾值)。當輸入信號幅度降至低于閾值時,SDOUT 將指示 LOS 信號(高于閾值)。該電路通過調(diào)整閾值電平來提供滯后功能。這意味著輸入信號幅度需要超過設定的 LOS 閾值,SDOUT 才會指示數(shù)據(jù)再次有效。這對應于 3 dB 的光學滯后。

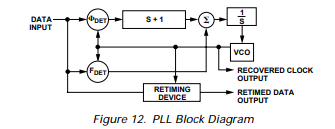

鎖相環(huán)(PLL)

PLL 恢復時鐘并對來自 NRZ 數(shù)據(jù)的信號進行重新定時。架構(gòu)使用頻率檢測器進行初始頻率捕獲,相關(guān)方框圖見圖 12。當 PLL 鎖定時,頻率誤差為零,頻率檢測器不再產(chǎn)生影響。由于頻率檢測器內(nèi)置于電路中,因此無需額外的控制功能來啟動捕獲或改變捕獲模式。

頻率檢測器向電荷泵提供電流脈沖,其平均電流與頻率誤差成正比。在頻率捕獲過程中,頻率檢測器輸出一系列寬度等于 VCO 周期的脈沖。這些脈沖在數(shù)據(jù)轉(zhuǎn)換時出現(xiàn)。當 VCO 頻率與最大密度(1010…)數(shù)據(jù)模式的頻率匹配時,每次循環(huán)滑動都會在頻率檢測器輸出處產(chǎn)生一個脈沖。然而,對于隨機數(shù)據(jù),并非每次循環(huán)滑動都會產(chǎn)生脈沖。不過,隨著數(shù)據(jù)轉(zhuǎn)換密度的增加,頻率檢測器輸出處的脈沖密度會增加。隨著頻率誤差趨近于零,每次循環(huán)滑動產(chǎn)生脈沖的概率也會增加。當頻率誤差降為零后,頻率檢測器將不再有脈沖輸出。此時,PLL 開始進入相位捕獲階段,設置時間約為 2000 個位周期。通過使用新的相位誤差測量方法(專利技術(shù)),由數(shù)據(jù)轉(zhuǎn)換密度變化(模式抖動)引起的抖動實際上被消除了。簡而言之,測量得到的相位誤差不會導致 VCO 相位增加,從而使平均運行速率由數(shù)據(jù)頻率決定。所產(chǎn)生的抖動由 2??1 偽隨機碼決定,其抖動幅度為 1/2 度,與隨機抖動相比幅度較小。

PLL 的抖動帶寬為中心頻率的 0.06%。選擇該參數(shù)是為了使 350 kHz 處的固有輸入抖動衰減 3 dB。

PLL 的阻尼比可通過單個外部電容器由用戶編程。一般來說,阻尼比與(f_DATA×C_O)2 成正比。

較低的阻尼比允許更快的頻率捕獲;通常,捕獲時間與電容值直接成比例。然而,當阻尼比接近 1 時,捕獲時間不再直接與電容值相關(guān)。捕獲時間包含兩個部分:頻率捕獲和相位捕獲。在實際應用中,相位捕獲時間由鎖相環(huán)帶寬決定。在這種情況下,頻率捕獲占主導地位。0.06% 的鎖相環(huán)帶寬對應的理論捕獲時間為 2000 個位周期。然而,實際捕獲時間為幾百萬個位周期,這是為了使阻尼電容上的電壓緩慢上升至最終值。

-

接收器

+關(guān)注

關(guān)注

15文章

2563瀏覽量

73394 -

時鐘

+關(guān)注

關(guān)注

11文章

1883瀏覽量

132845 -

數(shù)據(jù)恢復

+關(guān)注

關(guān)注

10文章

637瀏覽量

18013

發(fā)布評論請先 登錄

AD808 622 MBPS、低功耗、后置放大器/時鐘和數(shù)據(jù)恢復IC

ADN2807:155/622 Mb/s時鐘和數(shù)據(jù)恢復IC,帶集成限幅放大器數(shù)據(jù)表

AD808:帶量化器和時鐘恢復和數(shù)據(jù)重定時數(shù)據(jù)表的光纖接收器

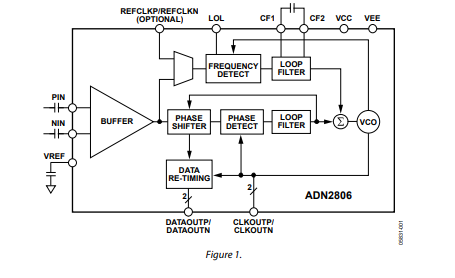

ADN2806:622 Mbps時鐘和數(shù)據(jù)恢復IC數(shù)據(jù)表

ADN2812:連續(xù)速率12.3 Mb/s至2.7 Gb/s時鐘和數(shù)據(jù)恢復IC,帶集成限幅放大器數(shù)據(jù)表

ADN2819:多速率至2.7 Gb/s時鐘和數(shù)據(jù)恢復IC,帶集成限幅放大器數(shù)據(jù)表

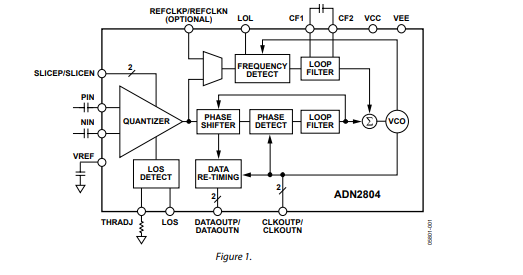

ADN2804:帶集成限幅放大器的622 Mbps時鐘和數(shù)據(jù)恢復IC產(chǎn)品說明書

ADN2814:連續(xù)速率10 Mb/s至675 Mb/s時鐘和數(shù)據(jù)恢復IC,帶集成限幅放大器數(shù)據(jù)表

ADN2913:連續(xù)速率6.5 Mbps至8.5 Gbps時鐘和數(shù)據(jù)恢復IC,集成限幅放大器/均衡器數(shù)據(jù)表

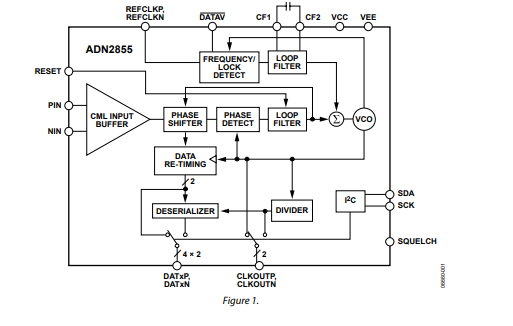

ADN2855:多速率155 Mbps/622 Mbps/1244 Mbps/1250 Mbps突發(fā)模式時鐘和數(shù)據(jù)恢復IC,帶解串器產(chǎn)品手冊

ADN2855多速率155 Mbps/622 Mbps/1244 Mbps/1250 Mbps突發(fā)模式時鐘和數(shù)據(jù)恢復IC技術(shù)手冊

ADN2804 622Mbps時鐘和數(shù)據(jù)恢復IC,集成限幅放大器技術(shù)手冊

ADN2806 622Mbps時鐘和數(shù)據(jù)恢復IC技術(shù)手冊

AD807 155 Mbps、低功耗、后置放大器/時鐘和數(shù)據(jù)恢復IC技術(shù)手冊

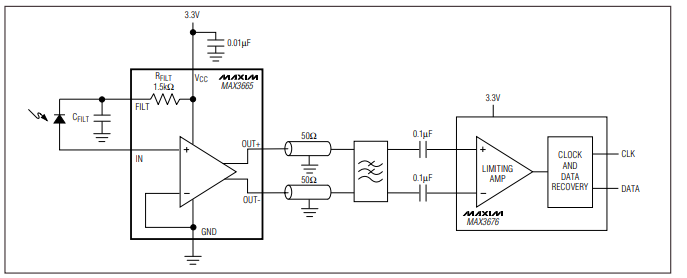

MAX3665 622Mbps、超低功耗,3.3V跨阻前置放大器,用于SDH/SONET技術(shù)手冊

AD808 622MBPS、低功耗、后置放大器/時鐘和數(shù)據(jù)恢復IC技術(shù)手冊

AD808 622MBPS、低功耗、后置放大器/時鐘和數(shù)據(jù)恢復IC技術(shù)手冊

評論