概述

AD9512提供多路輸出時鐘分配功能,輸入信號最高可達1.6 GHz。它具有低抖動和低相位噪聲特性,能夠極大地提升數據轉換器的時鐘性能。

數據表:*附件:AD9512 1.2 GHz時鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調整、5路輸出技術手冊.pdf

3路獨立的LVPECL時鐘輸出和2路LVDS時鐘輸出工作頻率分別為1.2 GHz和800 MHz。可選的CMOS時鐘輸出工作頻率為250 MHz。每路輸出都有一個可編程分頻器,可以旁路該分頻器或者設置最高32的整數分頻比。

用戶可以通過各分頻器改變一路時鐘輸出相對于其它時鐘輸出的相位,這種相位選擇功能可用于時序粗調。1路輸出還提供可編程延遲特性,具有最長10 ns的用戶可選滿量程延遲值。該精調延遲模塊通過一個5位字進行編程,提供32個可用的延遲時間供用戶選擇。

AD9512非常適合數據轉換器時鐘應用,利用亞皮秒抖動編碼信號,可實現優質的轉換器性能。

AD9512提供48引腳LFCSP封裝,額定溫度范圍為-40°C至+85°C,可以采用3.3 V單電源供電。

應用

特性

- 兩路1.6 GHz差分時鐘輸入

- 5個可編程分頻器,1至32整數分頻比

- 用于輸出到輸出延遲粗調的相位選擇

- 3路獨立的1.2 GHz LVPECL輸出

加性輸出抖動:225 fs均方根值 - 2路獨立的800 MHz/250 MHz LVDS/CMOS輸出

加性輸出抖動:275 fs均方根值

1路輸出提供延遲精調,5位延遲字 - 4線式或3線式串行控制端口

- 節省空間的48引腳LFCSP封裝

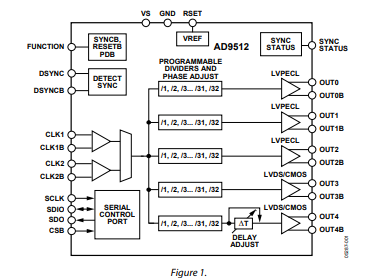

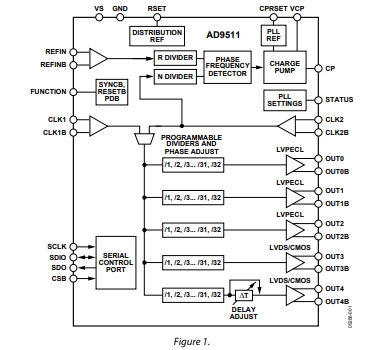

框圖

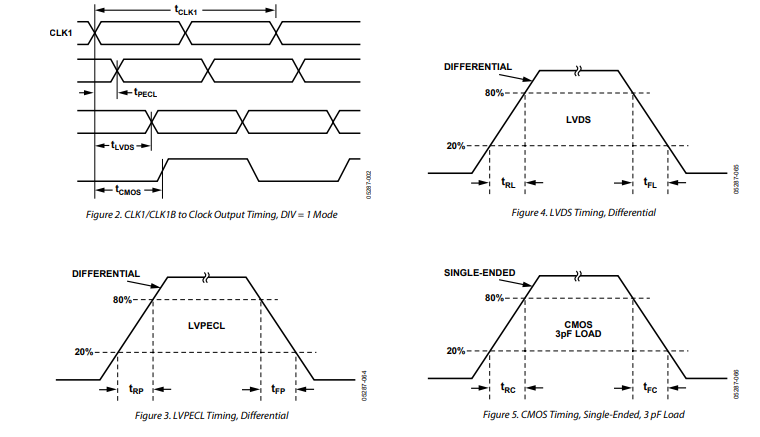

時序圖

引腳配置描述

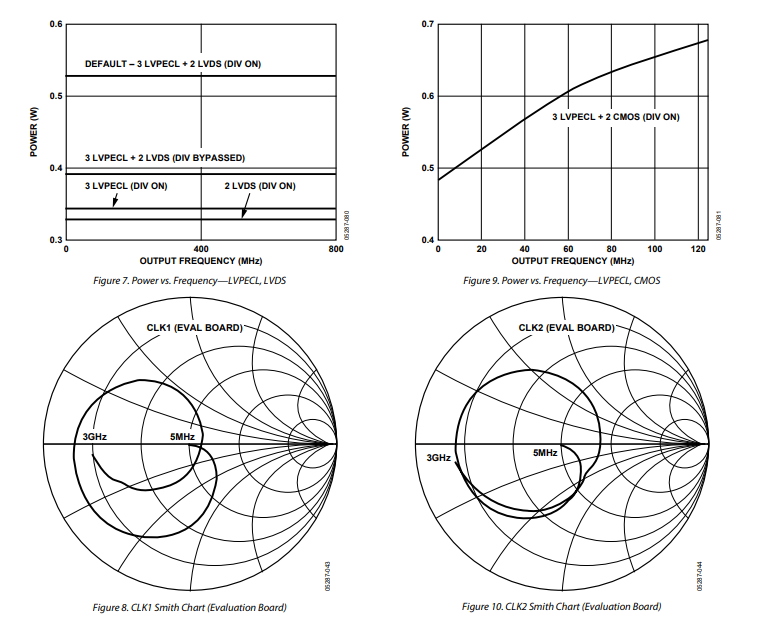

典型性能特征

功能描述

總體

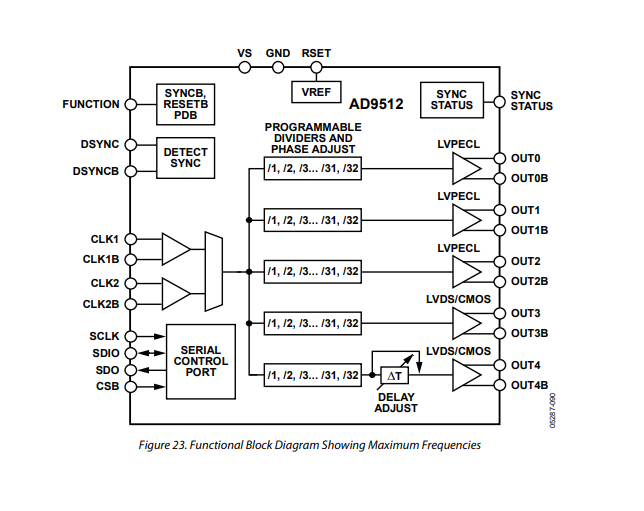

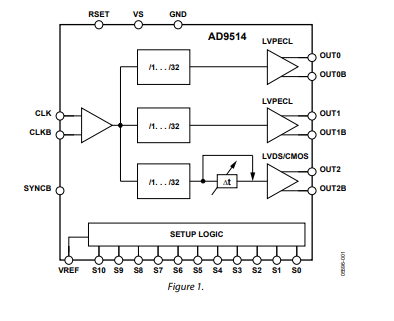

圖 23 展示了 AD9512 的框圖。AD9512 接受兩個時鐘輸入(CLK1 或 CLK2)中的任意一個。該時鐘可被除以 1 到 32 之間的任意整數值。輸出的占空比和相對相位可進行調整。

有三個 LVPECL 輸出(OUT0、OUT1、OUT2)和兩個可設置為 LVDS 或 CMOS 邏輯電平的輸出(OUT3、OUT4)。OUT4 也可使用可變延遲模塊。

AD9512 僅提供時鐘分配功能,不存在時鐘倍頻。輸入時鐘信號直接通過并可在輸出端占主導地位。

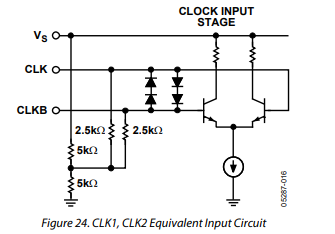

有關 CLK1 和 CLK2 的等效電路,請參見圖 24。

功能引腳(引腳 12)有三種功能,通過寄存器 58h<6:5> 中的設置進行選擇。此引腳上有一個 30 kΩ 的下拉電阻。

- RESETB:58h<6:5> = 00b(默認) :在其默認模式下,功能引腳充當 RESETB,拉低時會產生異步復位或硬復位。復位結果會將默認值寫入串行控制端口緩沖寄存器,并使芯片控制寄存器恢復默認值。AD9512 會立即按照默認值恢復運行。當該引腳再次拉高時,會發出異步 SYNC 信號(參見 SYNCB:58h<6:5> = 01b 部分)。

- SYNCB:58h<6:5> = 01b :功能引腳可用于使不同時鐘輸出之間實現同步或對齊相位。同步僅適用于以下時鐘輸出:

- 未斷電;

- 分頻器未被屏蔽(no_sync = 0);

- 未被旁路(bypass = 0)。

SYNCB 低電平有效。當 SYNCB 為低電平時,所選輸出會進入預設狀態。分頻器以預設的分頻值或快速時鐘(fast clock,由 CLK1 或 CLK2 中的選定時鐘輸入決定)開始計數。SYNCB 的應用會影響分頻器相位引腳中的所有位。無論該引腳是否也被指定用于復位或斷電,只要 SYNCB 功能被選中,功能引腳就不會充當 RESETB 或 PDB。

- PDB:58h<6:5> = 11b :功能引腳也可被編程為全功率關閉。在此斷電模式下,仍有一些殘余電壓 V 存在。在 PDB 模式下,功能引腳為高電平有效。芯片在該引腳變為低電平之前一直保持低功耗狀態。返回設置請參閱芯片斷電或睡眠模式 - PDB 部分,以了解有關功能引腳啟動斷電時的更多詳細信息。

動態同步引腳(DSYNC AND DSYNCB PINS)

DSYNC 和 DSYNCB 引腳(引腳 1 和引腳 2)用于 AD9512 在多路同步配置中(見多路同步部分)。

時鐘輸入(CLOCK INPUTS)

AD9512 有兩個時鐘輸入(CLK1、CLK2)可供使用。CLK2 和 CLK1 可接受高達 1600 MHz 的輸入頻率。圖 24 為 CLK2 和 CLK1 的等效電路。

時鐘輸入為全差分且自偏置。如果必須使用單端輸入,可通過在差分輸入的一側連接一個電容器來實現。另一側應通過一個電容器旁路至安靜的交流地。

未選擇的時鐘輸入(無論是 CLK1 還是 CLK2)應接地,以消除不需要的時鐘信號進入選定時鐘輸入的任何可能性。

-

時鐘

+關注

關注

11文章

1879瀏覽量

132840 -

數據轉換器

+關注

關注

1文章

374瀏覽量

28737 -

ad9512

+關注

關注

0文章

3瀏覽量

1319

發布評論請先 登錄

ADI設計峰會講義分享:實現更高信號處理性能的高級技術

1.2千兆赫時鐘分配IC 1.6GHz輸入分頻器延遲調整五輸出ad9512數據表

AD9512 1.2 GHz時鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調整、5路輸出

AD9512: 1.2 GHz Clock Distribution IC, 1.6 GHz Inputs, Dividers, Delay Adjust, Five Outputs Data Sheet

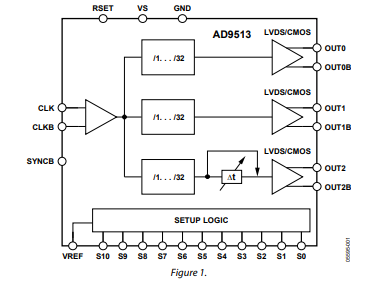

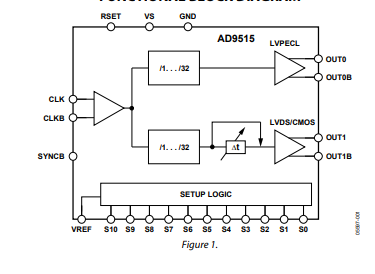

AD9514 1.6GHz時鐘分配IC、分頻器、延遲調整、3路輸出技術手冊

AD9510 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出技術手冊

AD9511 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,5路輸出技術手冊

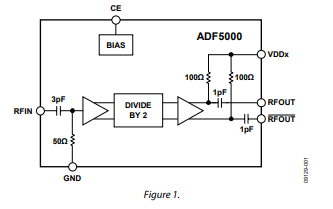

ADF5000 4GHz 至18GHz 2分頻預分頻器技術手冊

AD9512 1.2 GHz時鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調整、5路輸出技術手冊

AD9512 1.2 GHz時鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調整、5路輸出技術手冊

評論