概述

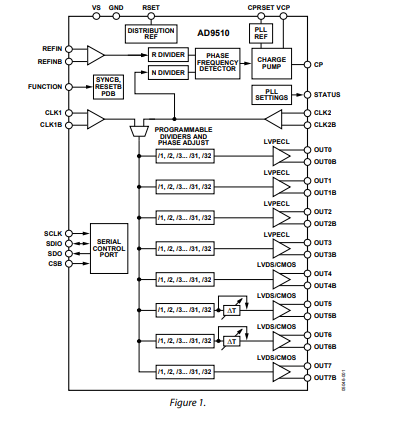

AD9514是一款多路輸出時鐘分配IC,具有低抖動和低相位噪聲特性,有助于實現優質數據轉換器性能。這款器件也適合相位噪聲和抖動要求嚴格的其它應用。

數據表:*附件:AD9514 1.6GHz時鐘分配IC、分頻器、延遲調整、3路輸出技術手冊.pdf

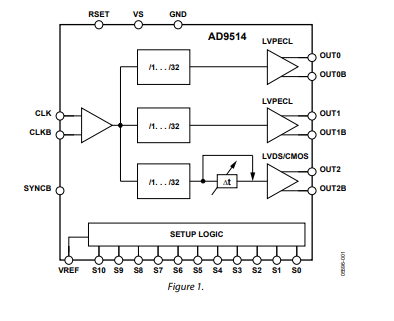

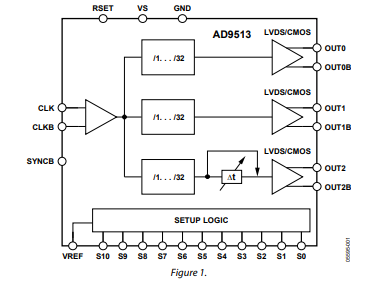

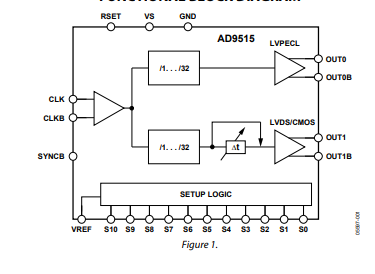

它提供3路獨立的時鐘輸出,其中2路為LVPECL,第3路輸出可設置為LVDS或CMOS電平。LVPECL輸出的工作頻率可達1.6 GHz,第3路輸出的工作頻率在LVDS模式下可達800 MHz,在CMOS模式下可達250 MHz。

數據表:

每路輸出都具有可編程分頻器,可設置1至32的整數分頻比。一路時鐘輸出相對于另一路時鐘輸出的相位可通過分頻器相位選擇功能進行設置,用作時序粗調。

LVDS/CMOS輸出提供延遲特性,具有三個可選的滿量程延遲值(1.5 ns、5 ns及10 ns),均可提供16級精調。

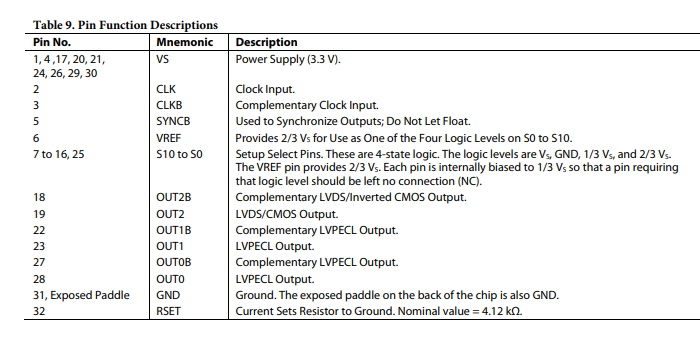

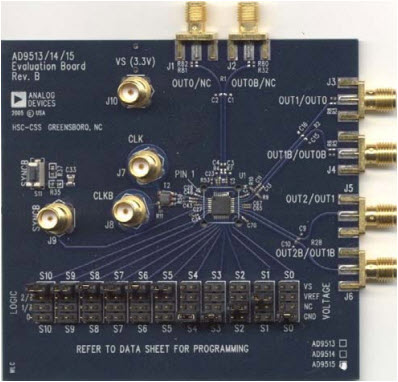

AD9514無需外部控制器即可進行操作或設置。器件通過11個引腳(S0至S10)和4個邏輯電平進行編程。編程引腳內部偏置為? VS。VREF引腳提供? VS電平。VS(3.3 V)和GND(0 V)提供另外兩個邏輯電平。

AD9514非常適合數據轉換器時鐘應用,利用亞皮秒抖動編碼信號,可實現優質的轉換器性能。

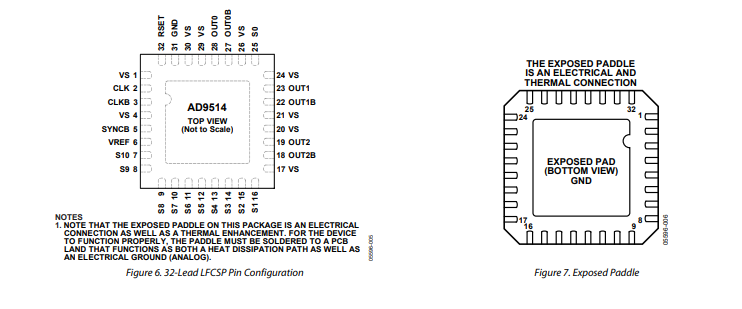

AD9514提供32引腳LFCSP封裝,采用3.3 V單電源供電。溫度范圍為?40°C至+85°C。

應用

特性

- 1.6 GHz差分時鐘輸入

- 3個可編程分頻器

- 編程范圍:1至32

- 用于輸出到輸出延遲粗調的相位選擇

- 2路獨立的1.6 GHz LVPECL時鐘輸出

- 加性寬帶輸出抖動:225 fs rms

- 1路獨立的800 MHz/250 MHz LVDS/CMOS時鐘輸出

- 加性寬帶輸出抖動:300 fs rms/290 fs rms

- 延遲時間最長10 ns

- 可利用4電平邏輯引腳進行器件配置

- 節省空間的32引腳LFCSP封裝

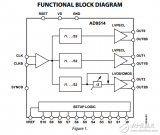

框圖

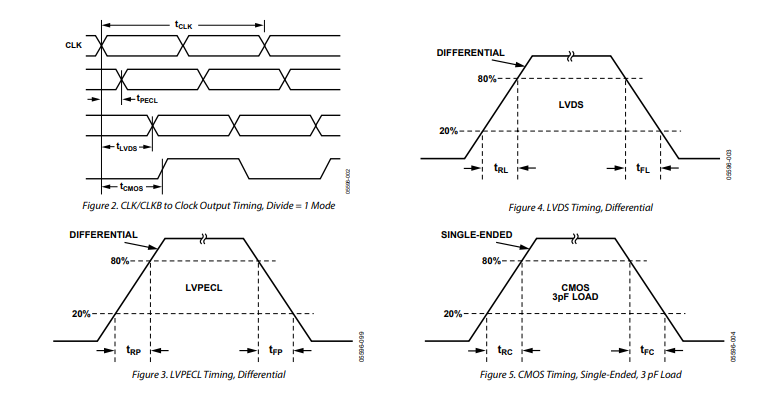

時序圖

引腳配置描述

術語

相位抖動和相位噪聲

理想正弦波可被視為在每個周期中,相位從 0 到 360 度連續且均勻變化。然而,實際信號的相位隨時間會偏離理想的相位變化,這種偏離量被稱為相位抖動。從總體來看,這種現象被稱為累積相位噪聲。導致相位抖動的因素眾多,其中一個主要因素是具有高斯(正態)分布統計特性的隨機噪聲。

這種相位抖動會使正弦波在頻域中的能量擴散,從而產生連續的功率譜。該功率譜通常以給定頻率偏移(相對于正弦波載波頻率)下的 dBc/Hz 為單位進行表示,其數值是在 1Hz 帶寬內與載波功率的比值。每次測量時,載波頻率的偏移量也會給出。

對特定頻率區間(例如 10kHz 至 10MHz)內的總功率進行積分也具有實際意義,這被稱為積分相位噪聲,它與該頻率偏移區間內相位噪聲所導致的時間抖動密切相關。

相位噪聲具有確定性影響,它會對模數轉換器(ADCs)、數模轉換器(DACs)和射頻混頻器的性能產生影響,降低這些轉換器和混頻器可實現的動態范圍,盡管影響方式略有不同。

時間抖動

相位噪聲是頻域現象,而時間抖動則是時域現象。當觀察正弦波時,會發現其過零點的時間出現變化。對于方波而言,時間抖動表現為信號從一個電平跳變到另一個電平的規則時間間隔出現位移。在這兩種情況下,與理想時間的偏差就是時間抖動。由于這些變化具有隨機性質,時間抖動通常以均方根(rms)值或高斯分布的 1 個標準差來表示。

數模轉換器(DAC)或模數轉換器(ADC)采樣時鐘的時間抖動會降低轉換器的信噪比(SNR)和動態范圍。抖動盡可能低的采樣時鐘能使給定轉換器發揮出最高性能。

附加相位噪聲

它是指可歸因于被測設備或子系統的相位噪聲量。測量時,必須減去任何外部振蕩器或時鐘源的相位噪聲,這樣就能確定設備對總系統相位噪聲的影響程度。在許多情況下,某個元件的相位噪聲會主導系統相位噪聲。

附加時間抖動

它是指可歸因于被測設備或子系統的時間抖動量。測量時,必須減去任何外部振蕩器或時鐘源的時間抖動,這樣就能確定設備對總系統時間抖動的影響程度。在許多情況下,外部振蕩器和時鐘源的時間抖動會主導系統時間抖動。

-

時鐘

+關注

關注

11文章

1883瀏覽量

132845 -

數據轉換器

+關注

關注

1文章

375瀏覽量

28747 -

ad9514

+關注

關注

0文章

2瀏覽量

1289

發布評論請先 登錄

1.6千兆赫時鐘分配IC分頻器延遲調整三輸出ad9514數據表

AD9514 1.6 GHz時鐘分配IC、分頻器、延遲調整、3路輸出

AD9514: 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Three Output Data Sheet

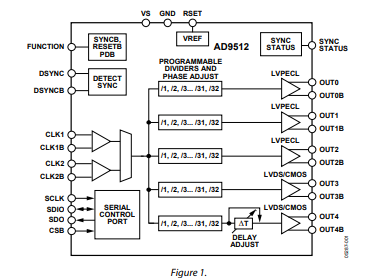

AD9512:1.2 GHz時鐘分配IC,1.6 GHz輸入,分頻器,延遲調整,五輸出數據表

基于AD9514/PCBZ時鐘緩沖器的參考設計

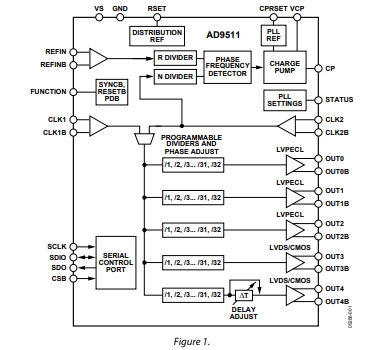

AD9510 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出技術手冊

AD9511 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,5路輸出技術手冊

AD9512 1.2 GHz時鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調整、5路輸出技術手冊

AD9514 1.6GHz時鐘分配IC、分頻器、延遲調整、3路輸出技術手冊

AD9514 1.6GHz時鐘分配IC、分頻器、延遲調整、3路輸出技術手冊

評論