本文聚焦高密度系統級封裝技術,闡述其定義、優勢、應用場景及技術發展,分析該技術在熱應力、機械應力、電磁干擾下的可靠性問題及失效機理,探討可靠性提升策略,并展望其未來發展趨勢,旨在為該領域的研究與應用提供參考。

關鍵詞:高密度系統級封裝技術;可靠性;失效機理;發展趨勢

一、引言

在電子信息技術飛速發展的當下,電子產品不斷朝著小型化、輕量化、高性能、多功能和低成本的方向邁進。系統級封裝(System in Package,SiP)技術作為一種先進的封裝技術,憑借其能夠滿足電子產品發展需求的特點,逐漸成為研究熱點。高密度系統級封裝技術作為SiP技術的進一步發展,更是展現出巨大的潛力和應用前景。本文將對高密度系統級封裝技術及其可靠性研究進展進行深入探討。

二、高密度系統級封裝技術概述

(一)定義與原理

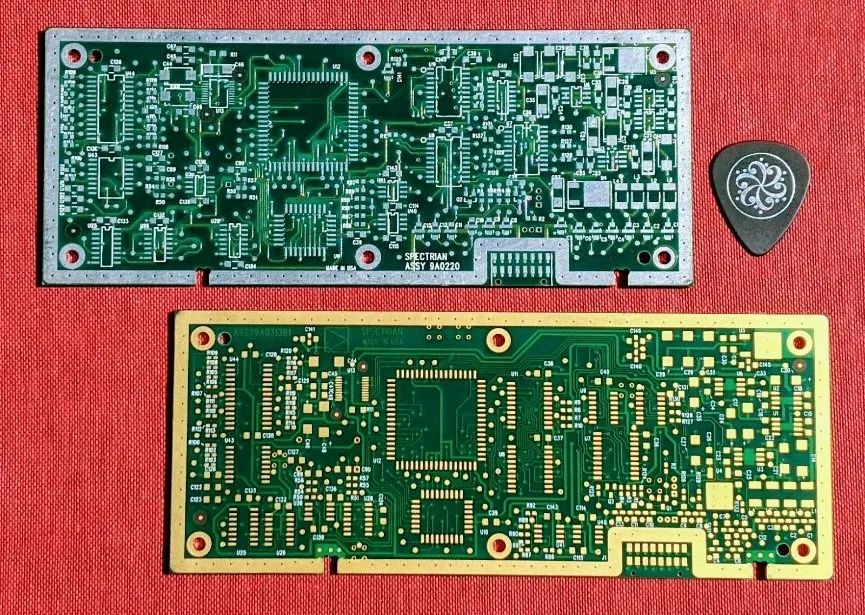

系統級封裝技術是將多個裸片(Die)及無源器件整合在單個封裝體內的集成電路封裝技術。根據國際半導體路線組織(ITRS)的定義,SiP為將多個具有不同功能的有源電子元件與可選無源器件,以及諸如MEMS或者光學器件等其他器件優先組裝到一起,實現一定功能的單個標準封裝件,形成一個系統或者子系統。從原理上講,SiP技術在封裝過程中涉及多種工藝,如無源器件貼片倒裝(Flip Chip)貼片、焊線鍵合(Wire Bond)、塑封(Molding)等,通過這些工藝將不同功能的芯片和無源器件集成在一起。

(二)技術優勢

高密度系統級封裝技術具有諸多優勢。它能夠增加芯片的集成度,將多個不同功能的芯片和無源器件集成在一個封裝內,減小了電路板的面積,降低了功耗,有助于延長移動設備的電池續航時間。例如,在手機中,通過SiP技術可以將處理器、存儲器、傳感器等不同功能的元件集成在一起,使手機更加輕薄便攜。此外,SiP技術相對片上系統(SoC)具有靈活度高、集成度高、設計周期短、開發成本低、容易進入等特點,能夠快速滿足市場對電子產品多樣化的需求。

(三)應用場景

高密度系統級封裝技術在多個領域得到了廣泛應用。在智能手機、AR/VR設備等消費電子領域,其對輕薄化與高性能的需求促使SiP技術得到了廣泛應用,如蘋果M系列芯片采用臺積電InFO-PoP封裝,實現CPU與內存的垂直集成。在汽車電子領域,從發動機控制單元到車載娛樂系統等各個部分都可以應用SiP技術,例如在汽車的高級駕駛輔助系統(ADAS)中,將攝像頭傳感器、雷達傳感器、信號處理芯片、通信芯片等集成在一個SiP封裝中,可以提高系統的響應速度和可靠性,同時減小系統的體積和重量,有助于汽車的輕量化設計。在醫療設備領域,如便攜式血糖儀、血壓計等小型醫療設備,SiP技術可以將測量電路、信號處理芯片、數據傳輸芯片等集成在一起,減小設備的體積,方便患者攜帶和使用。

三、高密度系統級封裝技術發展

(一)技術演進

高密度系統級封裝技術從傳統的二維封裝逐漸向三維堆疊封裝推進。傳統的二維封裝技術,如雙列直插式封裝(DIP)、四方扁平封裝(QFP)等,隨著電子產品對小型化和高性能的要求不斷提高,逐漸難以滿足需求。而三維堆疊封裝技術,如通過硅通孔(TSV)技術實現將一個芯片直接連接到另一個芯片上,能夠進一步縮小封裝尺寸,提高芯片之間的互連密度和信號傳輸速度。

(二)關鍵技術突破

在互連技術方面,除了傳統的引線鍵合、載帶自動焊(TAB)、倒裝焊等,通過直接互連實現芯片堆疊的TSV技術得到了廣泛應用。TSV技術可以實現芯片之間的高速互聯,縮短互連長度、提升帶寬、降低功耗。同時,混合鍵合技術也在不斷發展,銅-銅直接鍵合間距縮至1μm以下,互連密度大幅提升。在封裝材料方面,低k介質與原子層沉積(ALD)工藝結合,降低了寄生電容;石墨烯-金屬復合材料的導熱系數突破500W/m·K,應用于芯片層間熱擴散;玻璃基板替代有機基板,實現了超低翹曲與高頻特性。

(三)產業趨勢

隨著技術的不斷發展,高密度系統級封裝在全球先進芯片中的滲透率將不斷提高。臺積電、三星等代工廠在高密度3D封裝產能方面占據主導地位,傳統封測廠則轉向特定工藝。同時,地緣政治因素也對高密度系統級封裝產業產生了影響,美國CHIPS法案限制先進封裝設備出口,推動了中國本土供應鏈的建設。

四、高密度系統級封裝可靠性問題及失效機理

(一)熱應力問題

高密度系統級封裝內部復雜的封裝結構以及多種芯片、元件的組合構造導致其對熱應力更加敏感。在組裝焊接和工作過程中,溫度分布不均勻以及異常高溫的出現,會使不同材料之間因熱膨脹系數不一致產生熱失配,界面出現分層、裂紋等失效現象。例如,在回流焊過程中,由于上層器件的翹曲,堆疊焊球會呈現出不一致的焊接成型,且雪人式焊球的應力集中現象比水桶狀焊球更加嚴重。

(二)機械應力問題

芯片或器件的堆疊帶來的機械方面的可靠性挑戰也逐漸成為人們關注的焦點。SiP在機械應力方面的可靠性主要涉及堆疊封裝的厚度和尺寸、熱失配、焊點可靠性和包封體的硬度等。在循環彎曲、跌落等機械應力作用下,SiP產品的主要失效點集中在焊點位置,特別是當包封體的硬度較大時,高硬度的包封體會將更多的力傳遞到焊球上,加速互連失效。

(三)電磁干擾問題

高密度系統級封裝作為高度集成的封裝技術,存在高速、高密度、高功耗、低電壓和大電流的發展趨勢,產品的抗電磁干擾能力對新產品的成敗起到關鍵性的作用。其中電源分布網絡(PDN)設計和電源完整性(PI)研究的挑戰日益嚴峻。實際的供電系統是一個分布式網絡,存在大量的寄生電阻、寄生電感、寄生電容以及導納等,這些因素會降低電容的充放電速度,影響電源供給的穩定性。

五、高密度系統級封裝可靠性提升策略

(一)設計優化

在設計過程中,通過熱仿真分析熱應力的分布情況,可能存在的熱點等,據此通過更改SiP設計改善其熱設計。例如,合理選擇封裝材料以及采用合理的工藝流程,有利于減少熱-機械應力。同時,仿真技術的引入可對新設計的SiP產品的熱失配應力進行模擬,有利于減少產品的熱-機械應力。

(二)材料選擇

選擇正確的材料對于提高封裝的可靠性至關重要。材料的熱膨脹系數、彈性模量、熱導率和化學穩定性都直接影響封裝的可靠性。例如,選擇熱膨脹系數匹配的材料可以減少在溫度循環測試中封裝開裂的風險;高導熱性的材料可以幫助提高封裝的熱管理性能,而機械強度高的材料可以減少機械應力對封裝的影響。

(三)測試技術

采用先進的測試技術,如邊界掃描(Boundary Scan)與機器學習結合,實現堆疊芯片的快速缺陷定位。同時,針對不同的可靠性問題,制定相應的可靠性環境試驗,如溫度循環試驗、耐濕熱試驗、機械應力測試和電氣測試等,對封裝產品進行全面的可靠性評估。

六、結論與展望

高密度系統級封裝技術作為一種先進的封裝技術,在滿足電子產品小型化、高性能等方面具有顯著優勢,在多個領域得到了廣泛應用。然而,其可靠性問題也不容忽視,熱應力、機械應力和電磁干擾等問題都會影響封裝的性能和壽命。通過設計優化、材料選擇和測試技術等方面的努力,可以有效提高高密度系統級封裝的可靠性。

未來,高密度系統級封裝技術將繼續朝著更高密度、更高性能、更低成本的方向發展。隨著技術的不斷進步,新的封裝材料和互連技術將不斷涌現,如光子3D封裝、量子芯片集成等新興領域有望取得突破。同時,跨材料集成和Chiplet生態的成熟也將為高密度系統級封裝技術的發展帶來新的機遇和挑戰。企業需要在技術研發與生態合作中動態平衡,以搶占下一代制高點,推動半導體產業鏈格局的深度重塑。

-

半導體

+關注

關注

335文章

28609瀏覽量

232605 -

芯片封裝

+關注

關注

11文章

573瀏覽量

31245

發布評論請先 登錄

高密度系統級封裝:技術躍遷與可靠性破局之路

高密度系統級封裝:技術躍遷與可靠性破局之路

評論