劉曉昱 陳燕 李建強(qiáng) 喬彥彬 馬強(qiáng) 單書珊張海峰 唐曉柯

(北京智芯微電子科技有限公司國(guó)家電網(wǎng)公司電力芯片設(shè)計(jì)分析重點(diǎn)實(shí)驗(yàn)室 北京市電力高可靠性集成電路設(shè)計(jì)工程技術(shù)研究中心)

摘要:

高密度封裝技術(shù)在近些年迅猛發(fā)展,同時(shí)也給失效分析過程帶來新的挑戰(zhàn)。常規(guī)的失效分析手段難以滿足結(jié)構(gòu)復(fù)雜、線寬微小的高密度封裝分析需求,需要針對(duì)具體分析對(duì)象對(duì)分析手法進(jìn)行調(diào)整和改進(jìn)。介紹了X射線、計(jì)算機(jī)輔助層析成像(CT)技術(shù)、微探針和多方法聯(lián)用等失效分析技術(shù),分析了其原理和適用于高密度封裝的優(yōu)勢(shì)。并結(jié)合兩個(gè)高密度封裝失效分析案例,具體介紹了其在案例中的使用階段和應(yīng)用方法,成功找到失效原因。最后總結(jié)了各方法在高密度封裝失效分析中應(yīng)用的優(yōu)勢(shì)、不足和適用范圍。

0引言

20世紀(jì)80年代以來高密度微電子組裝技術(shù)迅速發(fā)展,大大提高了器件級(jí)IC封裝和板級(jí)電路組裝的密度[1-3]。近年來,以球柵陣列(ball grid array,BGA)封裝、小外形外殼封裝(small outline package,SOP)、芯片級(jí)封裝(chip scale package,CSP)、3D等封裝技術(shù)為代表的高密度封裝快速發(fā)展[4-5]。相對(duì)于扁平式封裝(quad flat package,QFP)等傳統(tǒng)封裝技術(shù),高密度封裝有著巨大優(yōu)勢(shì),例如:1.27mm間距的BGA在25mm邊長(zhǎng)的面積上可容納350個(gè)輸入/輸出(I/O)端口,遠(yuǎn)高于傳統(tǒng)封裝;CSP封裝的焊球節(jié)距小于1mm,有利于縮小整個(gè)芯片體積[6-8]。然而,隨著封裝特征尺寸逐漸減小,對(duì)其可靠性有著更高要求,高密度布線的金屬遷移短路、微銅柱凸點(diǎn)失效及BGA錫球焊接等新問題也隨之出現(xiàn)[9]。

失效分析在集成電路產(chǎn)業(yè)中發(fā)揮著重要作用,一般根據(jù)失效模式和現(xiàn)象,通過無損、有損實(shí)驗(yàn)分析驗(yàn)證,挖掘失效機(jī)理[10-11]。傳統(tǒng)失效分析方法包括:外部目檢、X射線檢查、超聲掃描檢查、電學(xué)測(cè)試、開封檢查等。由于高密度封裝具有線寬尺寸小、封裝密度高、結(jié)構(gòu)復(fù)雜等特點(diǎn),傳統(tǒng)的失效分析方法很容易產(chǎn)生無法探測(cè)失效點(diǎn)、破壞失效點(diǎn)等問題[12-13]。本文介紹了4種應(yīng)用于高密度封裝的失效分析檢測(cè)技術(shù)和方法,并結(jié)合案例詳述其分析過程。

1高密度封裝失效分析關(guān)鍵技術(shù)和方法

1.1X射線檢測(cè)技術(shù)

X射線檢測(cè)是一種重要的無損檢測(cè)技術(shù)。X射線在穿透物體不同部位時(shí),由于材料、厚度不同,會(huì)在不同路徑上產(chǎn)生不同衰減,進(jìn)而通過探測(cè)衰減程度而呈現(xiàn)物體內(nèi)部特征圖像[14-15]。

目前主流的X射線成像技術(shù)采用實(shí)時(shí)成像檢驗(yàn)系統(tǒng),主要特點(diǎn)是同時(shí)具有高分辨率和大動(dòng)態(tài)范圍。另外,隨著微焦點(diǎn)檢測(cè)等技術(shù)的應(yīng)用,X射線檢測(cè)精度日益提高,例如,YXLON公司生產(chǎn)的Y.CougarSMT型X射線檢測(cè)儀精度可達(dá)1μm,使其在高密度封裝產(chǎn)品檢測(cè)中發(fā)揮重要作用。

1.2CT檢測(cè)技術(shù)

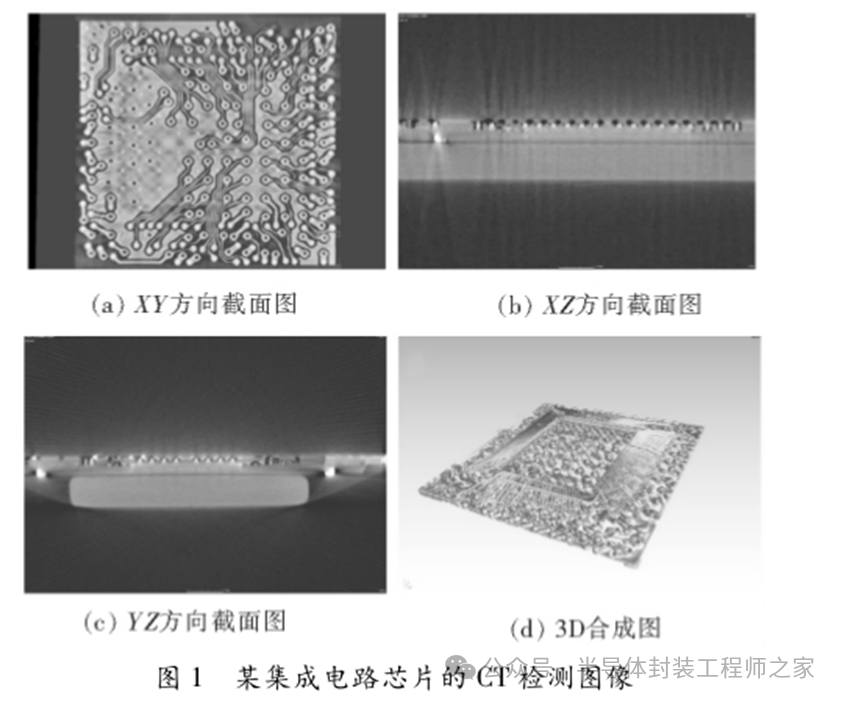

計(jì)算機(jī)輔助層析成像技術(shù)(computedtomography,CT)是X射線成像技術(shù)的延伸,通過采集待測(cè)物件不同角度的X射線投影信息,利用高性能計(jì)算機(jī)計(jì)算生成斷層圖像和三維(3D)圖像[16]。其中斷層掃描成像可以對(duì)待測(cè)樣品在XY,YZ,XZ三個(gè)方向上選取任意截面進(jìn)行成像,而不顯示其余無關(guān)部分,避免成像干擾。3D成像是利用計(jì)算機(jī)對(duì)選擇性過濾后的結(jié)構(gòu)或材料進(jìn)行3D重構(gòu),有利于分析高密度封裝中的復(fù)雜結(jié)構(gòu)。圖1為某集成電路芯片的CT檢測(cè)圖,其中圖1(a)~(c)分別為二維(2D)某層截面圖,圖1(d)為3D合成圖。

1.3X射線二維成像與CT技術(shù)聯(lián)用

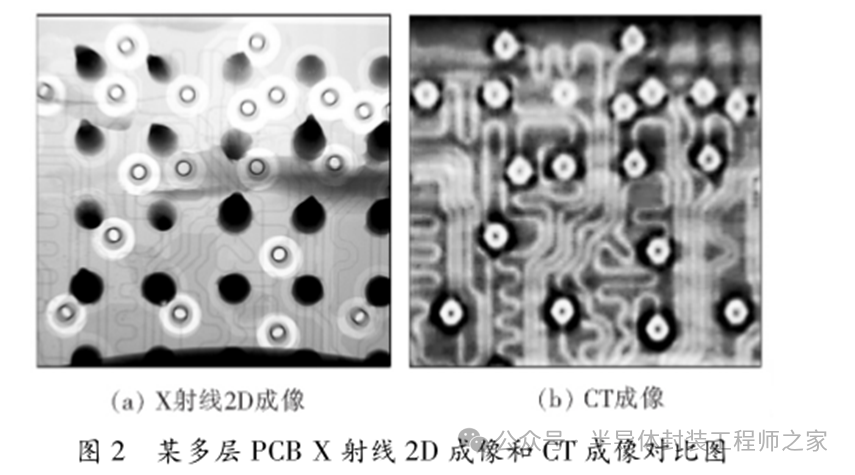

X射線在樣品內(nèi)部沿直線傳播,具有成像準(zhǔn)確、分辨率高的優(yōu)點(diǎn),然而對(duì)于結(jié)構(gòu)復(fù)雜的器件,多層結(jié)構(gòu)的投影會(huì)發(fā)生疊加;殼體較厚的陶瓷或金屬封裝電子元器件還會(huì)使細(xì)節(jié)特征襯度降低,影響分析結(jié)果[17]。CT技術(shù)成像是由計(jì)算機(jī)計(jì)算重建得來,其分辨率略低于X射線直接投影成像,尤其是在大倍數(shù)觀察時(shí),成像質(zhì)量低于X射線2D成像,如圖2所示,圖2(a)為某器件的多層印刷電路板(PCB)X射線2D放大成像圖,可見圖中金屬線輪廓清晰,分辨率較高,但BGA焊球(圖中黑色圓形陣列)等無關(guān)元素也同時(shí)被拍攝,圖2(b)為相同部位的CT斷層成像圖,過濾掉BGA焊球等無關(guān)成分,但分辨率較低。另外,3D成像還受到濾窗的人工調(diào)整、計(jì)算誤差、采集干擾等因素影響。聯(lián)合使用X射線2D成像、CT斷層成像和CT3D成像技術(shù),利用三者的優(yōu)勢(shì),對(duì)器件的不同部位采用不同分析手段,相同部位利用多種分析方法從不同角度進(jìn)行檢查,可以極大地提高分析準(zhǔn)確性。

1.4研磨制樣技術(shù)、X射線、FIB和探針臺(tái)聯(lián)用

研磨制樣技術(shù)是將樣品鑲嵌到樹脂中,經(jīng)過一系列研磨過程,得到樣品真實(shí)截面形貌的技術(shù),屬于有損分析,在元器件失效分析中具有重要作用。聚焦離子束(FIB)設(shè)備可以使用高能離子對(duì)樣品表面原子進(jìn)行剝離,以進(jìn)行微納加工。探針臺(tái)是晶圓測(cè)試領(lǐng)域的重要設(shè)備,探針可分為軟針和硬針,軟針針尖直徑為0.2~1μm,硬針針尖直徑多為5μm到幾百微米;探針座在X,Y,Z三個(gè)方向上的線性移動(dòng)精度可以小于1μm,探針臺(tái)具有靈活性高、精度高、信號(hào)穩(wěn)定等優(yōu)點(diǎn)[18]。

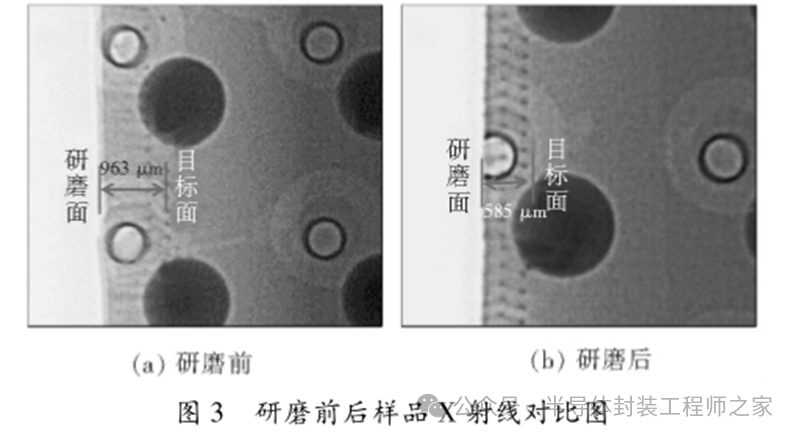

在高密度封裝中,金屬線寬減小,部分缺陷的尺寸也隨之降低,甚至只有幾十微米,這就要求在研磨制樣時(shí)做到高精度,并嚴(yán)格控制研磨速度,稍小的失誤都有可能造成研磨過量。這時(shí)可以在研磨的過程中使用X射線觀測(cè),測(cè)量研磨一定時(shí)間前后兩次觀察時(shí)的研磨長(zhǎng)度,以計(jì)算該研磨條件下的研磨速度;同時(shí)利用X射線測(cè)量研磨面至缺陷的剩余距離,結(jié)合研磨速度實(shí)現(xiàn)精準(zhǔn)研磨控制。使用特定的研磨條件對(duì)某高密度封裝失效樣品進(jìn)行30s研磨,研磨前后進(jìn)行X射線照射得到對(duì)比圖,如圖3所示,經(jīng)測(cè)量研磨面距目標(biāo)位置的距離分別為963和585μm,則研磨距離為378μm,該條件下研磨速度為12.6μm/s,則在該條件下再研磨46s左右可至目標(biāo)位置。

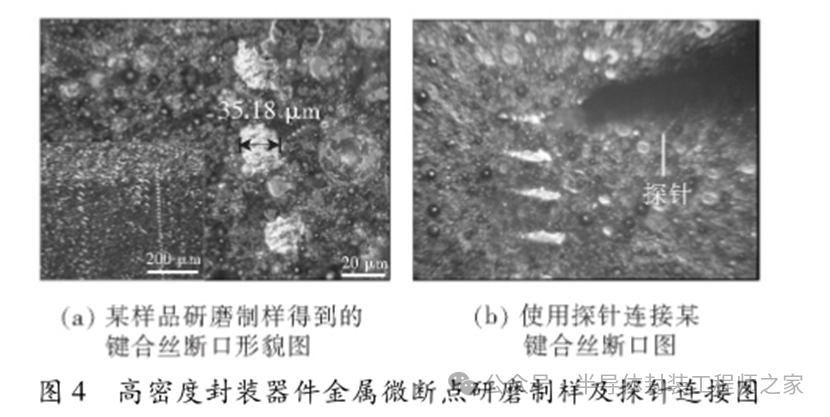

在研磨至觀測(cè)面時(shí),若缺陷尺寸遠(yuǎn)小于金屬線寬,則研磨造成的金屬延展的影響不可忽視,這時(shí)可以使用FIB設(shè)備去除表面延展金屬,露出底層金屬的真實(shí)形貌。若研磨得到某電路中間的微斷點(diǎn),需進(jìn)行部分電路的電學(xué)測(cè)試,則可使用探針臺(tái)建立精準(zhǔn)穩(wěn)定的電學(xué)連接。例如:研磨制樣得到的某鍵合絲斷口(圖4(a))直徑約為35μm,常規(guī)的電學(xué)連接針無法精準(zhǔn)連接,而探針臺(tái)的探針硬針針尖直徑可達(dá)5μm,并且通過精準(zhǔn)定位實(shí)現(xiàn)穩(wěn)定連接,如圖4(b)所示。

2失效分析在高密度封裝失效案例中的應(yīng)用

2.1CPU失效分析

某批次進(jìn)口CPU產(chǎn)品發(fā)生功能失效,失效率為10-3。該芯片為BGA封裝,共1000多個(gè)芯片管腳,868個(gè)封裝管腳,Cu鍵合絲,基板采用4層FR4印刷電路板。進(jìn)口商不提供芯片管腳和封裝管腳的對(duì)應(yīng)關(guān)系。

將封裝輸入/輸出管腳依次對(duì)地管腳進(jìn)行正反向I-V測(cè)試。發(fā)現(xiàn)其中7個(gè)輸入/輸出管腳的I-V曲線異常,表現(xiàn)為同一管腳在多次測(cè)試中會(huì)隨機(jī)出現(xiàn)開路和正常兩種情況,測(cè)試時(shí)對(duì)芯片的按壓力度影響兩種曲線出現(xiàn)的概率,按壓力度大時(shí)多表現(xiàn)為正常,按壓力度小時(shí)多表現(xiàn)為開路,初步判斷器件內(nèi)部存在虛接。

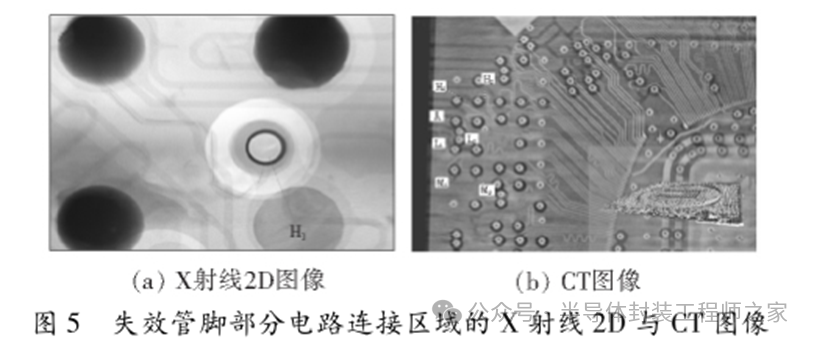

利用X射線2D成像、CT斷層成像和CT3D成像技術(shù)共同對(duì)失效件進(jìn)行檢查分析。首先,利用CT獲取平行于芯片表面的斷層圖像,逐層分析,部分金屬線寬過小區(qū)域結(jié)合X射線2D圖像,確定封裝管腳、金屬引線框架、鍵合絲、芯片管腳的連接對(duì)應(yīng)關(guān)系,以便進(jìn)行后續(xù)有損電學(xué)檢測(cè)分析,如圖5所示,圖中H1,H2,J1,L1,L2,M1,M2為失效管腳名稱,圖5(b)中插圖為3D圖像。

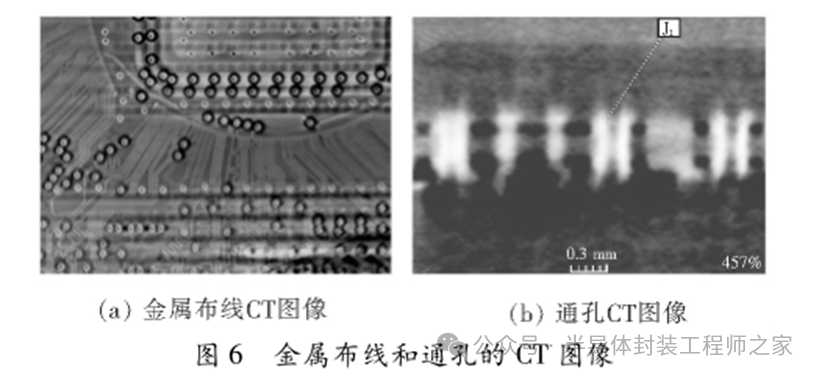

其次,利用CT在平行于芯片方向和垂直于芯片方向的斷面圖上分別檢查金屬布線和通孔有無異常,如圖6所示。經(jīng)初步檢查,失效管腳對(duì)應(yīng)的封裝金屬布線均無開路、短路的明顯異常。推斷失效點(diǎn)可能位于鍵合絲第一鍵合點(diǎn)或第二鍵合點(diǎn)。

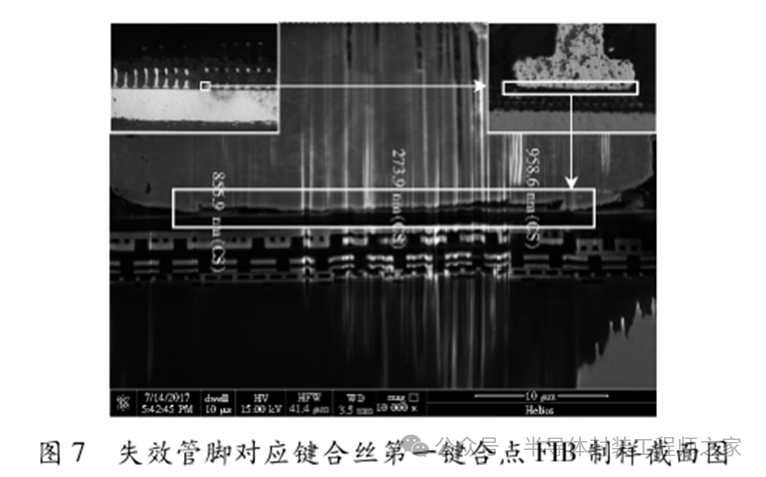

對(duì)失效點(diǎn)進(jìn)行由外側(cè)向內(nèi)側(cè)的縱向研磨制樣,第二鍵合點(diǎn)未見異常,第一鍵合點(diǎn)存在異常。得到第一鍵合點(diǎn)失效的截面后,為消除研磨過程中的金屬延展影響,對(duì)截面采用FIB切去表面層,露出深層截面的原始形貌,如圖7所示,插圖均為截面金相顯微圖。結(jié)果發(fā)現(xiàn),失效管腳的Cu鍵合絲和Al管腳之間存在縫隙,縫隙的最大寬度為959nm,最小寬度為274nm。該縫隙是造成開路虛接失效的原因。

2.2BGA封裝ARM芯片失效分析

某進(jìn)口BGA封裝ARM芯片在使用時(shí)出現(xiàn)功能異常,失效率約為6×10-4,芯片為Cu鍵合。解焊芯片后,首先將失效芯片和參考芯片的功能管腳對(duì)地管腳進(jìn)行I-V測(cè)試。發(fā)現(xiàn)異常管腳I-V曲線與參考件不同,曲線正、負(fù)向電流均減小,懷疑由某處電阻增大造成。芯片進(jìn)行X射線和CT檢查均未見異常,但由于失效現(xiàn)象并非開路失效,X射線檢測(cè)精度有可能無法滿足要求,故采用二分法進(jìn)行電學(xué)定位,同樣利用X射線和CT技術(shù)聯(lián)用確定封裝內(nèi)部連接關(guān)系。

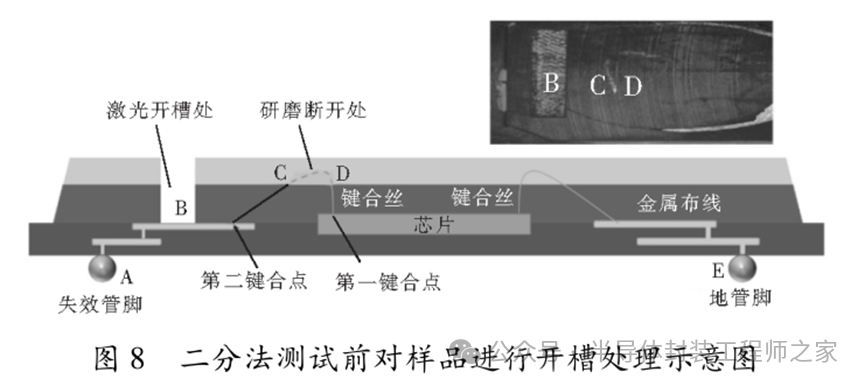

由于其他封裝管腳對(duì)相同地端管腳測(cè)試表現(xiàn)為正常曲線,故異常點(diǎn)出現(xiàn)在失效管腳-金屬布線-鍵合絲-芯片的區(qū)域。如圖8所示(插圖為樣品研磨后B,C,D區(qū)域圖像),圖中A點(diǎn)為失效管腳,B點(diǎn)為激光開槽露出的金屬引線框架,C點(diǎn)為鍵合絲研磨的第一斷口,D點(diǎn)為鍵合絲研磨的第二斷口,E點(diǎn)為地管腳。首先,對(duì)鍵合絲和失效管腳之間的金屬引線框架區(qū)域進(jìn)行激光開槽,露出金屬引線框架。利用探針臺(tái)測(cè)試B點(diǎn)和失效管腳之間的電阻,顯示無異常,而B點(diǎn)至地管腳的I-V曲線為異常。之后,從樣品上表面沿平行于樣品表面的方向向下研磨,磨斷鍵合絲中部,不破壞其余部分,漏出C和D兩點(diǎn)。利用探針臺(tái)連接斷點(diǎn),進(jìn)行電學(xué)測(cè)試發(fā)現(xiàn):A和C之間電阻無異常,D和地管腳之間測(cè)試為I-V異常。表明異常點(diǎn)處于失效管腳對(duì)應(yīng)鍵合絲的第一鍵合點(diǎn)處,排除第二鍵合點(diǎn)異常。

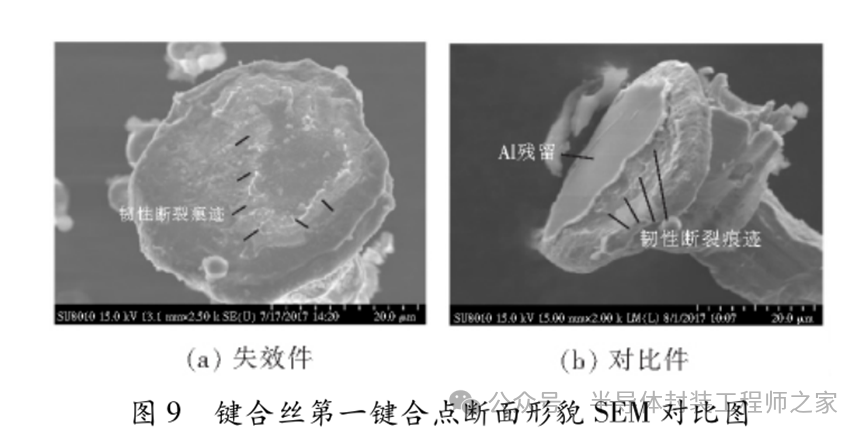

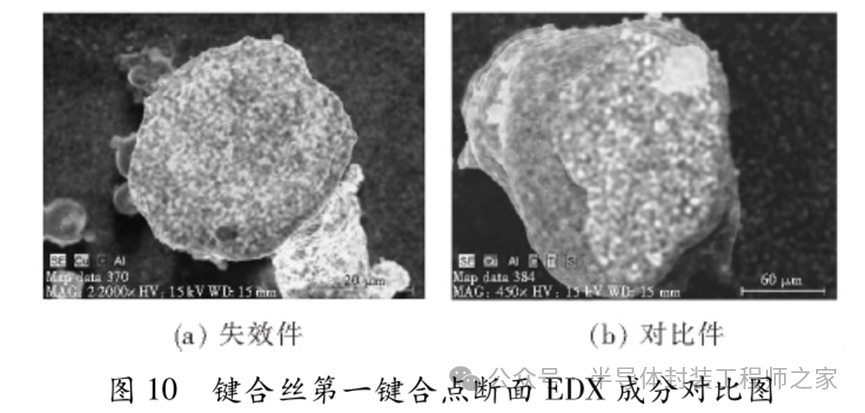

對(duì)芯片進(jìn)行正面開封,首先使用激光進(jìn)行初步開封,然后使用弱冷酸進(jìn)行開封,最大限度地保留Cu鍵合完整。將鍵合絲拔下,鍵合絲在其和Al管腳結(jié)合處斷開,得到斷口,使用相同辦法得到對(duì)比器件的鍵合絲第一鍵合點(diǎn)斷口。使用掃描電子顯微鏡(SEM)對(duì)兩個(gè)器件的第一鍵合點(diǎn)典型斷口進(jìn)行形貌觀察和對(duì)比分析,結(jié)果如圖9所示,使用SEM設(shè)備的能量色散X射線光譜儀(EDX)進(jìn)行斷口成分分析,結(jié)果如圖10所示。

結(jié)合圖9和圖10可以發(fā)現(xiàn),失效樣品鍵合絲典型斷口區(qū)域形貌和元素特征為:斷口大面積區(qū)域?yàn)镃u,少部分區(qū)域顯示為兩種結(jié)合金屬脫離的韌性斷裂形貌,并且有Al殘留。對(duì)比件典型斷口處有大面積Al管腳脫離殘留以及阻擋層鈦,未有脫離Al管腳殘留的其余部分均顯示為兩種結(jié)合金屬脫離的韌性斷裂形貌,并且有Al成分殘留。對(duì)比檢測(cè)實(shí)驗(yàn)表明,失效件第一鍵合點(diǎn)Cu鍵合絲和Al管腳之間沒有形成良好的金屬間化合物,導(dǎo)致接觸電阻增大,進(jìn)而導(dǎo)致失效。

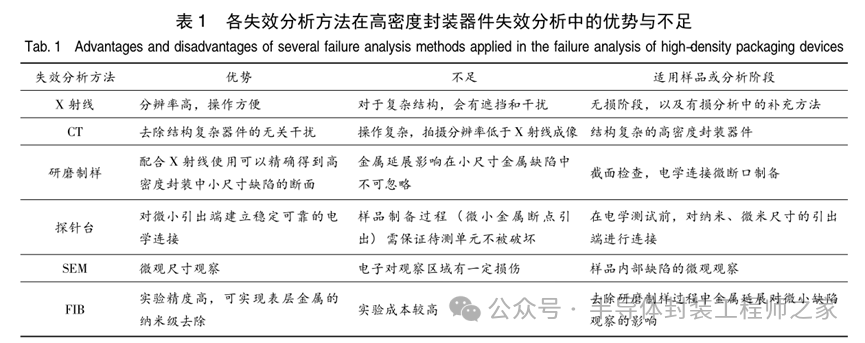

各種失效分析方法在高密度封裝器件失效分析中均有自身的優(yōu)勢(shì)與不足,詳見表1,并且在一定情況下應(yīng)不單純遵循傳統(tǒng)的方法,可以根據(jù)樣品特點(diǎn)進(jìn)行創(chuàng)新,或?qū)⒍喾N方法聯(lián)合使用。

3結(jié)論

按常規(guī)方法使用傳統(tǒng)的失效分析手段對(duì)高密度封裝器件進(jìn)行分析,會(huì)遇到結(jié)構(gòu)復(fù)雜、線寬尺寸過小等困難,這時(shí)應(yīng)對(duì)傳統(tǒng)的失效分析手段進(jìn)行創(chuàng)新,或者將多種分析方法進(jìn)行聯(lián)合使用,例如本文提到的鍵合絲斷口電學(xué)連接測(cè)試、X射線測(cè)量輔助的高精度研磨方法等,通過實(shí)例展示了創(chuàng)新方法在高密度封裝器件失效分析中的應(yīng)用效果,給出了傳統(tǒng)失效分析方法在高密度封裝器件失效分析中的優(yōu)勢(shì)與不足。

微電子封裝技術(shù)是微電子制造技術(shù)的延伸,隨著集成電路器件的小型化發(fā)展,分立封裝向系統(tǒng)級(jí)封裝演變,高密度封裝技術(shù)必將持續(xù)推進(jìn)。常規(guī)失效分析技術(shù)仍需要不斷改進(jìn)或創(chuàng)新,以解決更高密度封裝的失效問題。

-

芯片

+關(guān)注

關(guān)注

459文章

52091瀏覽量

435428 -

集成電路

+關(guān)注

關(guān)注

5416文章

11923瀏覽量

366870 -

封裝

+關(guān)注

關(guān)注

128文章

8446瀏覽量

144694 -

失效分析

+關(guān)注

關(guān)注

18文章

227瀏覽量

66842

原文標(biāo)題:適用于高密度封裝的失效分析技術(shù)及其應(yīng)用

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

器件高密度BGA封裝設(shè)計(jì)

元器件失效分析方法

探討高密度小間距LED屏工藝

高速高密度PCB設(shè)計(jì)的關(guān)鍵技術(shù)問題是什么?

DC/DC轉(zhuǎn)換器的高密度印刷電路板(PCB)布局

高密度封裝技術(shù)推動(dòng)測(cè)試技術(shù)發(fā)展

指導(dǎo)分享高密度光纖配線架安裝方法

高密度Interposer封裝設(shè)計(jì)的SI分析

揭秘高密度有機(jī)基板:分類、特性與應(yīng)用全解析

高密度3-D封裝技術(shù)全解析

高密度系統(tǒng)級(jí)封裝:技術(shù)躍遷與可靠性破局之路

高密度封裝失效分析關(guān)鍵技術(shù)和方法

高密度封裝失效分析關(guān)鍵技術(shù)和方法

評(píng)論