概述

AD9548可為包括同步光纖網絡(SONET/SDH)在內的許多系統提供同步。它可以產生一個與高達四個差分或者八個單端外部輸入基準之一同步的輸出時鐘。數字PLL能減少與外部基準有關的輸入時間抖動或者相位噪聲。即使當所有基準發生故障,AD9548仍能夠利用數控環路和保持(holdover)電路連續產生有效的、干凈的(低抖動)輸出時鐘。

數據表:*附件:AD9548 4-8路輸入的網絡時鐘發生器-同步器技術手冊.pdf

AD9548可工作于-40°C至+85°C的工業溫度范圍。

應用

- 網絡同步

- 基準時鐘抖動清除

- GPS 1 每秒脈沖數同步

- SONET/SDH時鐘,直到OC-192,包括前向糾錯(FEC)

- Stratum 2保持(holdover),抖動清除,及相位瞬變控制

- Stratum 3/3E 基準時鐘

- 無線基站,控制器

- 有線基礎設施

- 數據通信

特性

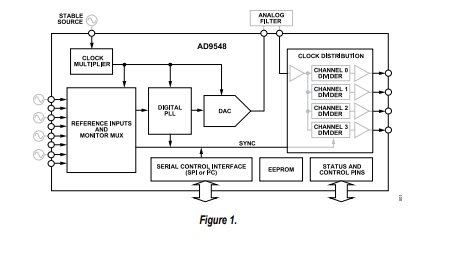

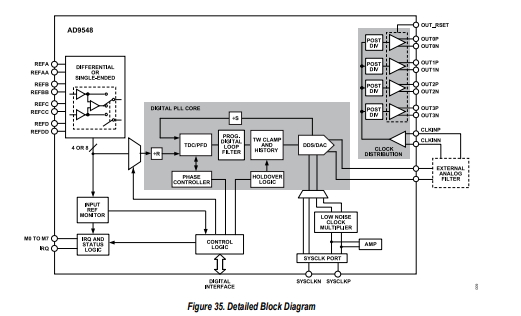

框圖

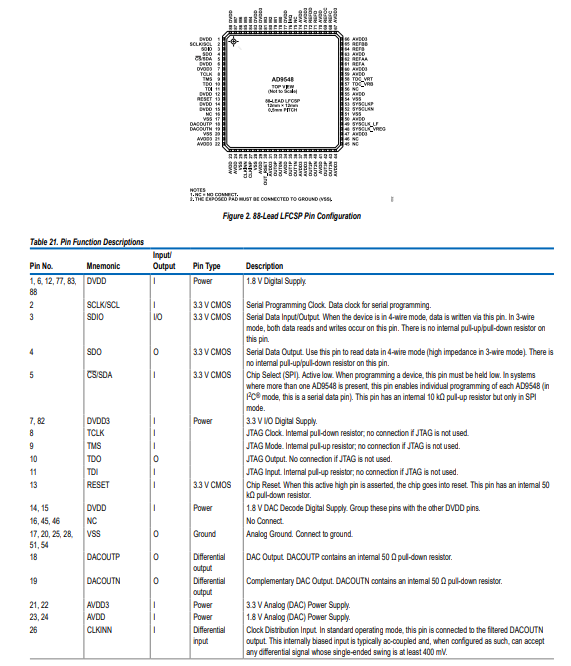

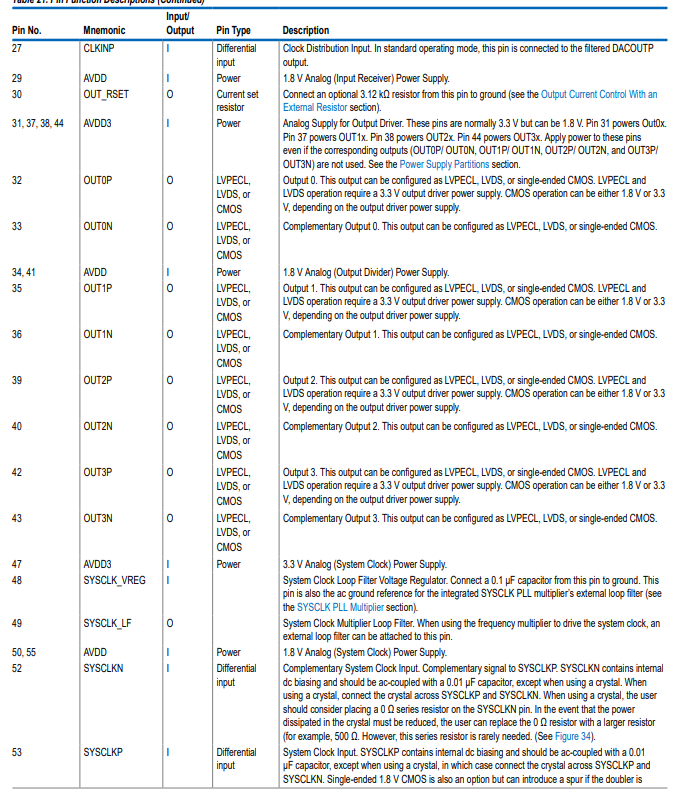

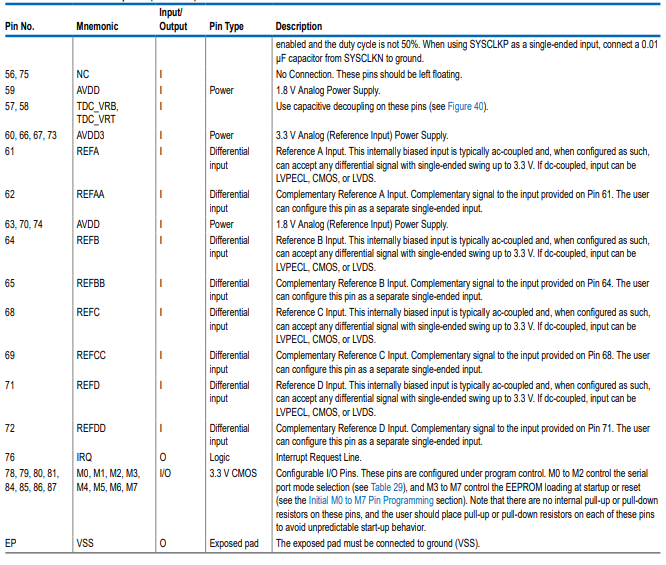

引腳配置描述

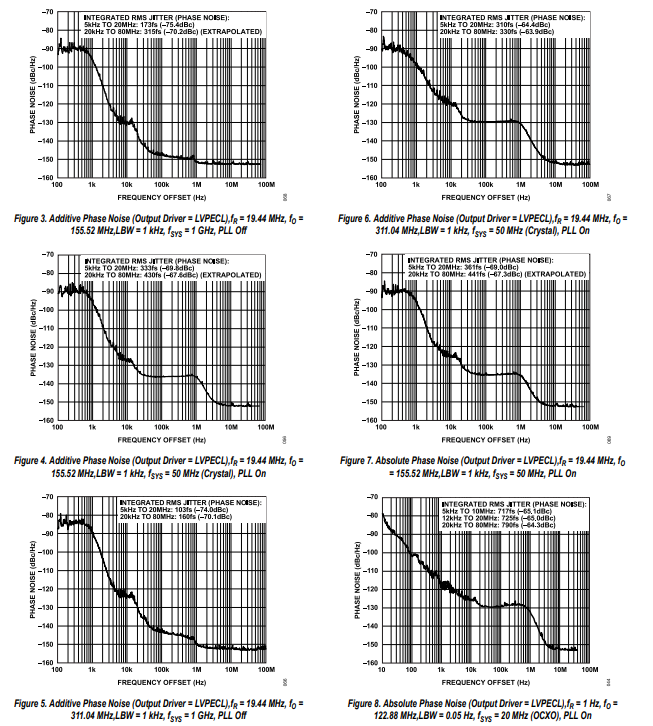

典型性能特征

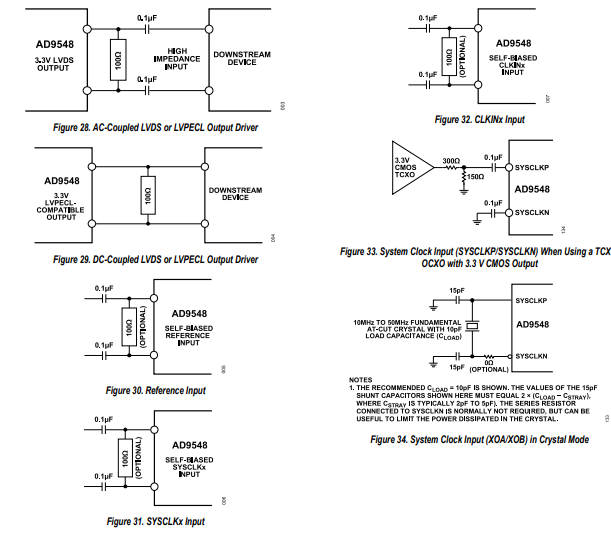

輸入/輸出端接建議

操作理論

AD9548提供的時鐘輸出在相位和頻率上與所選(有效)參考時鐘直接相關,主要由系統時鐘控制。AD9548支持多達八個參考輸入通道以及廣泛的參考頻率。該產品的核心是一個數字鎖相環(DPLL)。DPLL具有可編程數字環路濾波器,可大幅降低抖動傳輸,從有源參考時鐘到輸出。AD9548支持多種手動和自動切換模式。在保持模式下,只要數模轉換器(DAC)采樣時鐘存在,AD9548就會持續提供輸出。保持模式輸出頻率是保持模式前輸出頻率歷史記錄的時間平均值。

該器件提供手動和自動參考切換功能,如果有源參考失效或出現故障,它可以切換到備用參考。直接數字合成器(DDS)和集成DAC構成一個數字控制振蕩器(DCO)。DCO輸出是一個正弦信號(最大450 MHz),其頻率由有源參考頻率以及可編程參考預分頻器(R)和反饋分頻器(S)確定。雖然圖35中未明確顯示,但D - 除法器包含一個整數和分數組件,類似于分數N型合成器。

SYSCLKx輸入為DAC提供采樣時鐘,它可以是直接應用的高頻源,也可以是低頻源,通過集成的PLL倍頻器提供所需頻率。低頻選項還允許使用連接在SYSCLKx輸入兩端的晶體諧振器。

DAC輸出直接在芯片上進行濾波,去除采樣雜散。一旦輸入信號轉換為單端信號,內部濾波器就會將濾波后的正弦信號轉換為時鐘信號(方波),其上升沿和下降沿都非常快。

時鐘分配部分為四個輸出驅動器提供信號。每個驅動器可配置為單端差分LVPECL/LVDS輸出或雙單端CMOS輸出。此外,四個輸出中的每一個都有一個專用的30位可編程正/負分頻器。這使得時鐘分配部分在高達725 MHz的頻率下都能使用。它可以使用帶通重建濾波器(例如SAW濾波器)從DAC輸出頻譜中提取圖像,從而允許輸出頻率超過DAC輸出典型的450 MHz限制。

參考時鐘輸入

四對引腳為參考時鐘接收器提供接入。每對引腳可配置為單個差分接收器或兩個獨立的單端接收器,以適應輸入信號以及緩慢上升和下降沿的情況。差分和單端輸入接收器都采用遲滯方式,遲滯可確保輸入不會因浮動輸入而導致接收器出現自發振蕩。

配置為差分工作模式時,輸入接收器可適應交流或直流耦合輸入信號。接收器內部直流偏置,以處理交流耦合操作。

配置為單端工作模式時,輸入接收器具有典型值為45 kΩ的下拉負載。每個單端接收器都有三個用戶可編程閾值電壓范圍。

-

發生器

+關注

關注

4文章

1395瀏覽量

62494 -

時鐘

+關注

關注

11文章

1879瀏覽量

132836 -

同步器

+關注

關注

1文章

106瀏覽量

15045 -

AD9548

+關注

關注

0文章

9瀏覽量

11752

發布評論請先 登錄

MAX3679A高性能四路輸出時鐘發生器(Maxim)

基于AD9548的數據同步采集系統設計

四/八進制輸入網絡時鐘發生器/同步器AD9548數據表

AD9548 4/8路輸入的網絡時鐘發生器/同步器

AD9548芯片的性能特點及應用

毫微微時鐘網絡同步器、抖動衰減器和時鐘發生器RC32112A 數據表

AD9548 4-8路輸入的網絡時鐘發生器/同步器技術手冊

AD9548 4-8路輸入的網絡時鐘發生器/同步器技術手冊

評論