概述

AD9571具有多路輸出時鐘發生器功能,內置專用PLL內核,針對以太網線路卡應用進行了優化。整數N PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器產品系列,確保實現較高的網絡性能。這款器件也適合相位噪聲和抖動要求嚴格的其它應用。

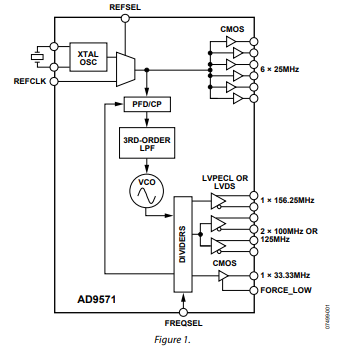

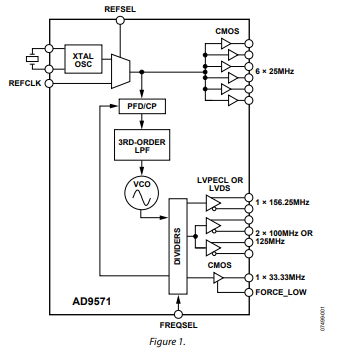

PLL部分由低噪聲鑒頻鑒相器(PFD)、精密電荷泵(CP)、低相位噪聲電壓控制振蕩器(VCO)和預編程反饋分頻器與輸出分頻器組成。通過將外部晶振或基準時鐘連接至REFCLK引腳,可將最高達156.25 MHz的頻率鎖定至輸入基準。

每個輸出分頻器和反饋分頻器分頻比都針對要求的輸出速率進行預編程。無需外部環路濾波器元件,從而節約了寶貴的設計時間和電路板空間。

AD9571提供40引腳6 mm × 6 mm引腳架構芯片級封裝,采用3.3 V單電源供電。工作溫度范圍為?40°C至+85°C。

數據表:*附件:AD9571以太網時鐘發生器,10路時鐘輸出技術手冊.pdf

特性

- 完全集成VCO/PLL內核

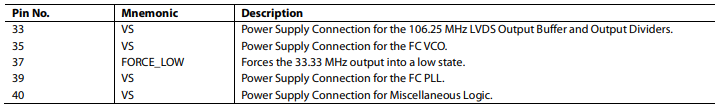

156.25 MHz時,抖動值:0.17 ps均方根值(1.875 MHz至20 MHz)

125 MHz時,抖動值:0.41 ps均方根值(12 kHz至20 MHz)

輸入晶振或時鐘頻率:25 MHz

- 完全集成VCO/PLL內核

- 針對156.25 MHz、33.33 MHz、100 MHz和125 MHz預設分頻比

- 可選LVPECL或LVDS輸出格式

- 集成環路濾波器

- 6路基準時鐘輸出

- 速率通過綁定引腳配置

- 節省空間的6 mm × 6 mm、40引腳LFCSP封裝

- 功耗:0.48 W(LVDS工作模式)

- 欲了解更多特性,請參考數據手冊

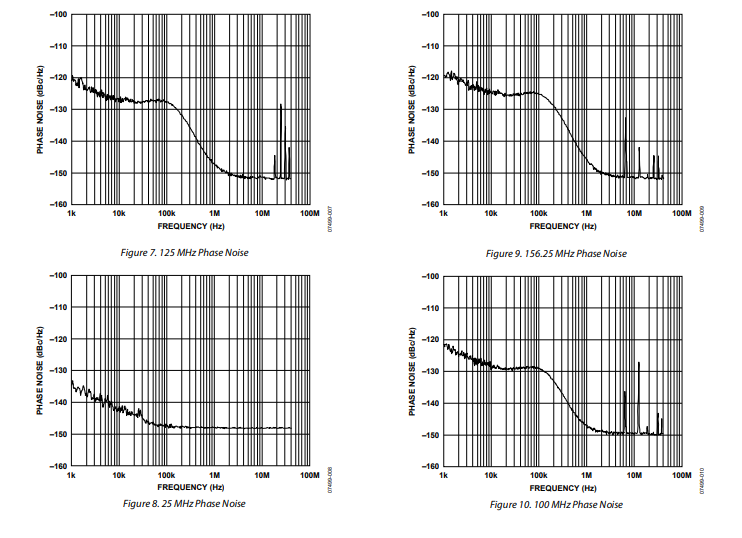

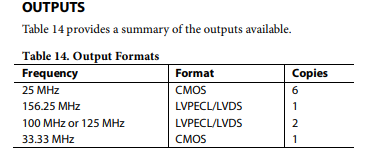

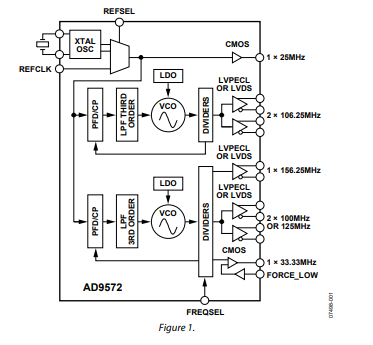

框圖

框圖

總體描述

AD9571提供多輸出時鐘發生器功能,其專用的鎖相環(PLL)核心針對以太網線路卡應用進行了優化。獨特的N分頻PLL設計基于亞德諾半導體公司的技術,集成了高性能、低抖動頻率合成器,以最大化網絡性能。其他對相位噪聲和抖動要求嚴苛的應用也能從此設計中受益。

PLL部分由低噪聲鑒頻鑒相器(PFD)、精密電荷泵(CP)、低壓擺幅電壓控制振蕩器(VCO)以及預編程的反饋分頻器和輸出分頻器組成。通過將外部晶體或參考時鐘連接到REFCLK引腳,高達156.25MHz的頻率可與輸入參考頻率鎖定。

每個輸出分頻器和反饋分頻器的比例都針對所需的輸出速率進行了預編程。無需外部環路濾波器組件,從而節省了寶貴的設計時間和電路板空間。

AD9571采用40引腳、6mm×6mm引線框架芯片級封裝,可在-40°C至85°C的單一溫度范圍內工作。

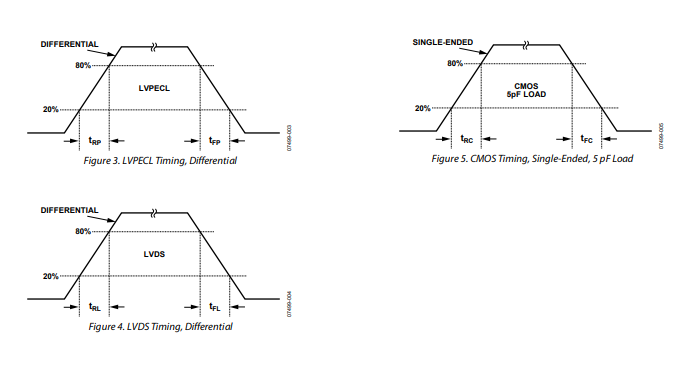

時序圖

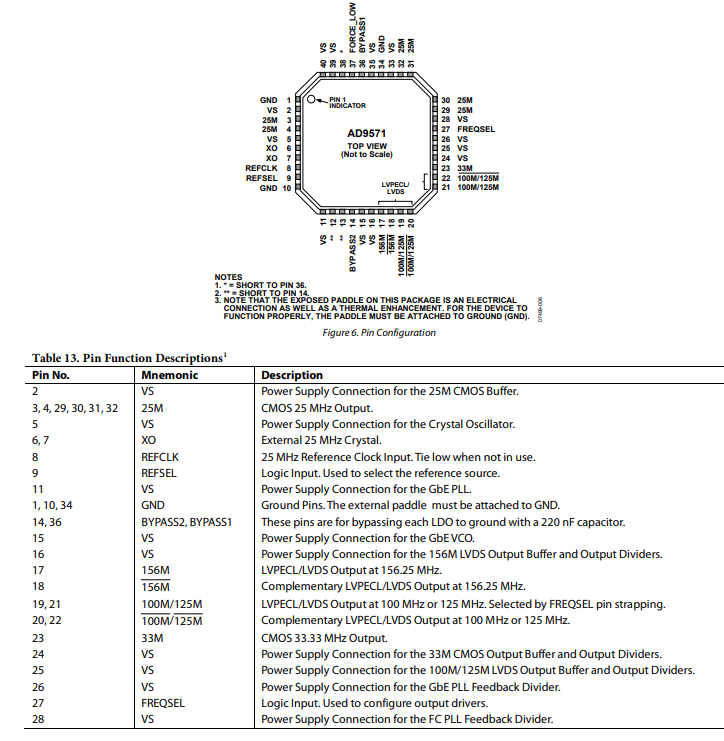

引腳配置描述

典型性能特征

操作理論

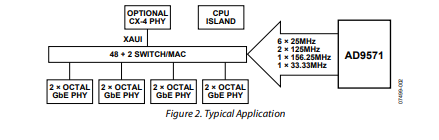

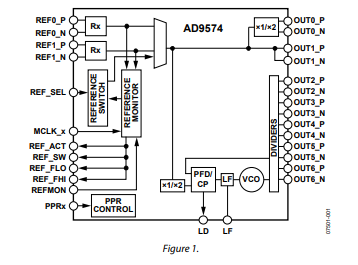

圖11展示了AD9571的框圖。該芯片由一個PLL核心組成,其被配置為生成以太網應用所需的特定時鐘頻率,無需任何用戶編程。這基于亞德諾半導體成熟的合成器技術,以卓越的相位噪聲性能著稱。AD9571集成度高,包含環路濾波器、電源噪聲抑制調節器,以及所有必要的分頻器和多種輸出緩沖器格式,還帶有一個晶體振蕩器。用戶只需選擇一個25MHz參考時鐘或外部晶體,即可實現完整的線路卡時鐘解決方案,無需任何處理器干預。此外,還提供六個25MHz參考時鐘源。

-

發生器

+關注

關注

4文章

1399瀏覽量

62551 -

時鐘發生器

+關注

關注

1文章

223瀏覽量

68938 -

ad9571

+關注

關注

1文章

3瀏覽量

3839

發布評論請先 登錄

AD9571ACPZPEC時鐘發生器銷售

Maxim推出高性能、三路輸出時鐘發生器MAX3625B

MAX3679A高性能四路輸出時鐘發生器(Maxim)

以太網時鐘發生器10時鐘輸出ad9571數據表

AD9571 以太網時鐘發生器,10路時鐘輸出

AD9520-0:12路LVPECL/24路CMOS輸出時鐘發生器,集成2.8 GHz VCO

AD9523-1:低抖動時鐘發生器,14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出 數據手冊

AD9574以太網 千兆以太網時鐘發生器技術手冊

AD9572光纖通道/以太網時鐘發生器IC,PLL內核,分頻器,7路時鐘輸出技術手冊

AD9571以太網時鐘發生器,10路時鐘輸出技術手冊

AD9571以太網時鐘發生器,10路時鐘輸出技術手冊

評論