概述

HMC7043旨在滿足多載波GSM和LTE基站設計的要求,并通過多種時鐘管理和分配特性來簡化基帶和無線電卡時鐘樹的設計

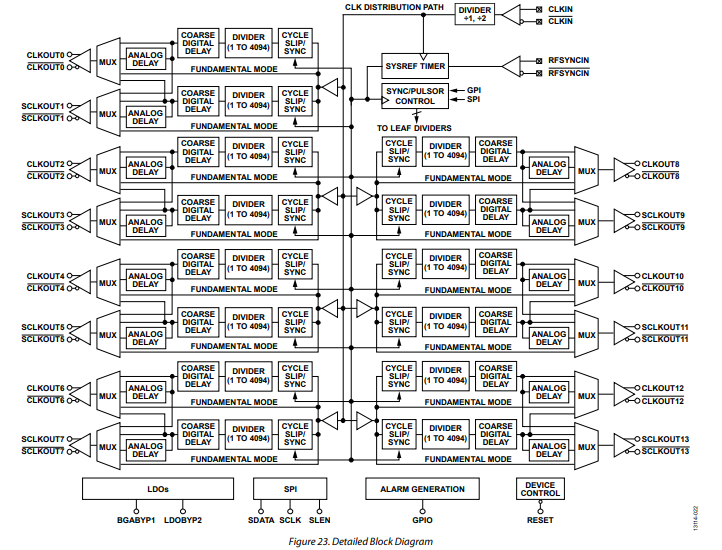

HMC7043提供14路低噪聲且可配置的輸出,可以靈活地與基站收發臺(BTS)系統中的許多不同器件接口,如數據轉換器、本振、發射/接收模塊、現場可編程門陣列(FPGA)和數字前端ASIC等。 HMC7043可生成符合JESD204B接口要求的多達7個DCLK和SYSREF時鐘對。

數據表:*附件:HMC7043高性能、3.2 GHz、14輸出扇出緩沖器技.pdf

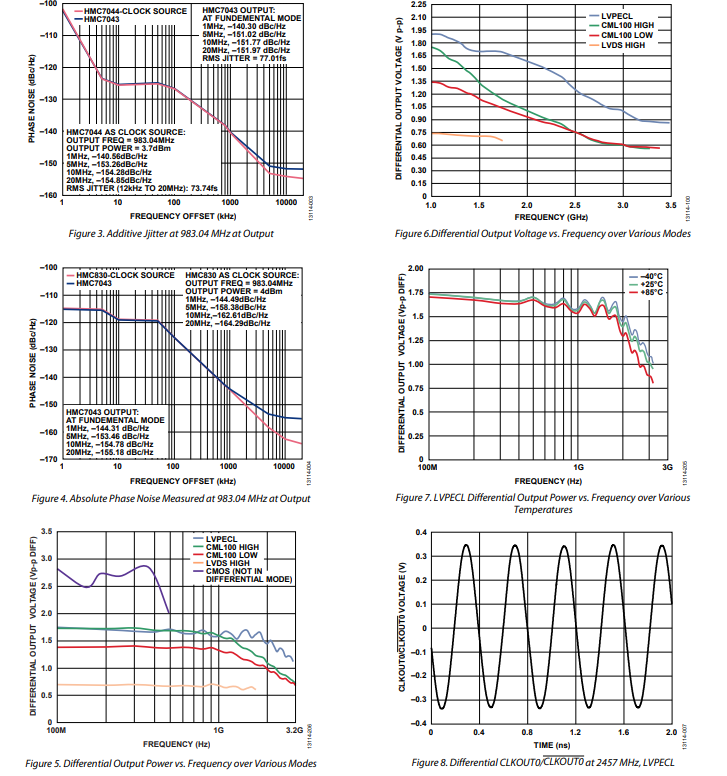

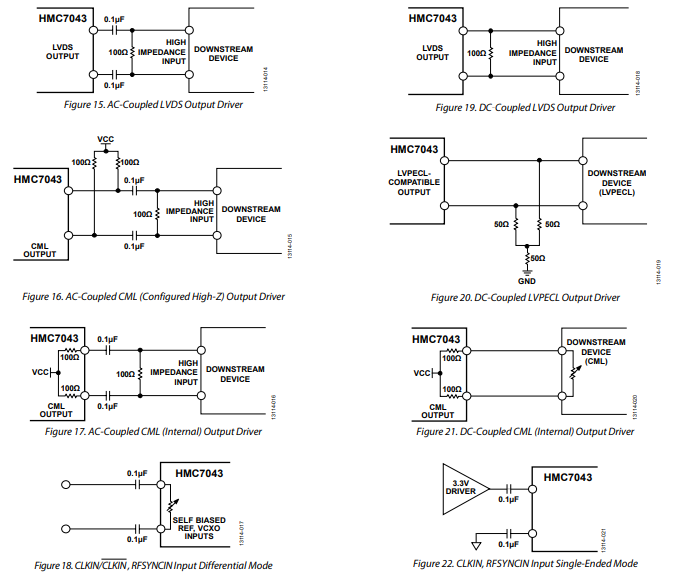

系統設計人員可以生成更少的DCLK和SYSREF對,并針對獨立的相位和頻率配置其余的輸出信號路徑。 DCLK和SYSREF時鐘輸出均可配置為支持CML、LVDS、LVPECL和LVCMOS等不同的信號標準,不同的偏置條件則可調整變化的板插入損耗。

HMC7043獨特的特性之一是對14個通道分別進行獨立靈活的相位管理。 所有14個通道均支持頻率和相位調整。 這些輸出還可針對50 Ω或100 Ω內部和外部端接選項進行編程。

HMC7043器件具有RF SYNC功能,支持確定性同步多個HMC7043器件,即確保所有時鐘輸出從同一時鐘沿開始。 可通過改寫嵌套式HMC7043或SYSREF控制單元/分頻器,然后重新啟動具有新相位的輸出分頻器來實現。

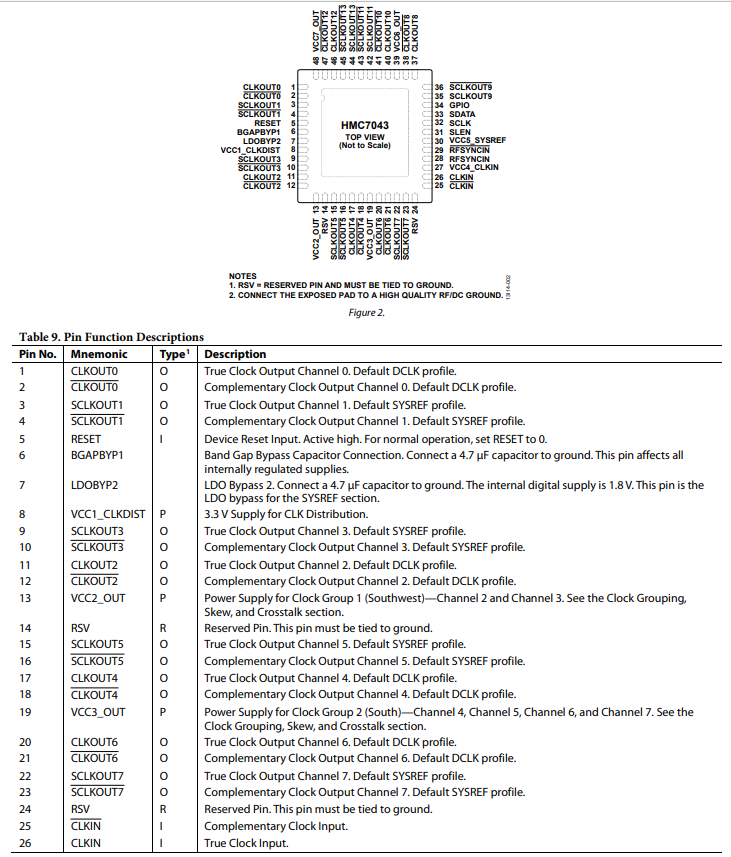

HMC7043采用48引腳、7 mm × 7 mm LFCSP封裝,且裸露焊盤接地。

應用

特性

- 支持JEDEC JESD204B

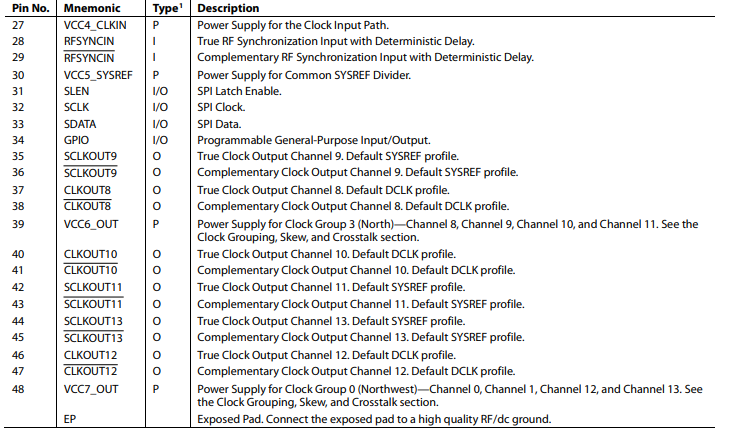

- 低加性抖動: <15 fs rms(2457.6 MHz,12 kHz至20 MHz)

- 極低噪底: -155.2 dBc/Hz (983.04 MHz)

- 最多提供14路LVDS、LVPECL或CML型器件時鐘(DCLK)

- CLKOUTx/CLKOUTx and SCLKOUTx/SCLKOUTx 最高頻率達 3200 MHz

- JESD204B兼容系統參考(SYSREF)脈沖

- 25 ps模擬延遲和?時鐘輸入周期數字延遲,14個時鐘輸出通道各自都能對延遲進行編程

- 可調噪底與功耗的關系可通過SPI編程

- SYSREF有效中斷可簡化JESD204B同步

- 支持確定性同步多個HMC7043器件

- RFSYNC引腳或SPI控制的SYNC觸發用于輸出同步JESD204B

- GPIO報警/狀態指示用于確定系統狀況

- 時鐘輸入支持高達6 GHz的頻率

- 片內穩壓器提供出色的PSRR

- 48引腳、7 mm × 7 mm LFCSP封裝

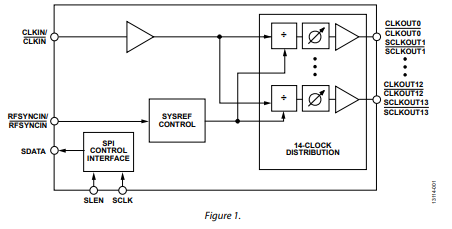

框圖

引腳配置描述

典型性能特征

典型應用電路

詳細框圖

評估印刷電路板(PCB)和原理圖

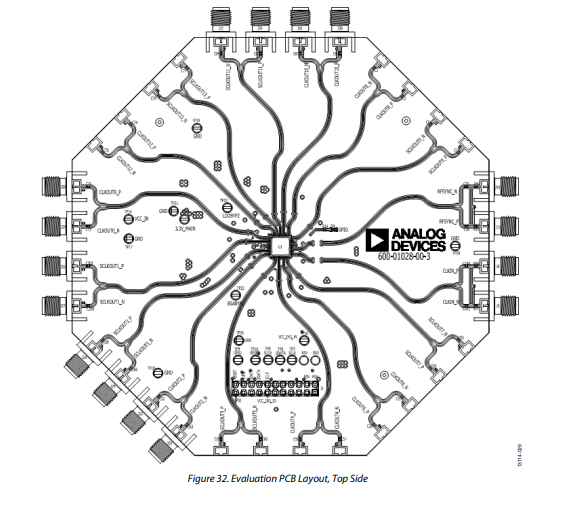

在此應用中,電路板需采用射頻(RF)電路設計技術。確保信號線的阻抗為 50Ω。將封裝的接地引腳和裸露焊盤直接連接到接地層,如圖 32 和圖 33 所示。使用足夠數量的過孔連接頂層和底層接地層。評估電路板可從凌力爾特公司(Analog Devices, Inc.)獲取,具體情況視庫存而定。

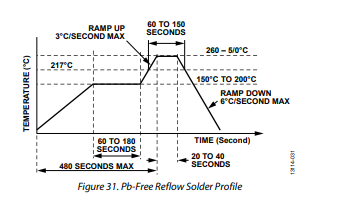

典型的無鉛回流焊溫度曲線如圖 31 所示,基于 JEDEC J - STD - 20C 標準。

-

緩沖器

+關注

關注

6文章

2037瀏覽量

46603 -

時鐘

+關注

關注

11文章

1882瀏覽量

132842 -

基帶

+關注

關注

5文章

162瀏覽量

31272

發布評論請先 登錄

請教關于HMC7043的RF SYNC對CLKOUT的影響

ADCLK846/PCBZ,ADCLK954高性能時鐘扇出緩沖器評估板

HMC7043 高性能、3.2 GHz、14輸出扇出緩沖器

HMC7044: 帶 JESD204B 接口的高性能、3.2 GHz、14 路輸出抖動衰減器

UG-942:HMC6832 3.5 GHz、低噪聲、2:8差分扇出緩沖器評估板

EVAL-HMC7043 HMC7043評估套件

高性能時鐘緩沖器HMC7043介紹

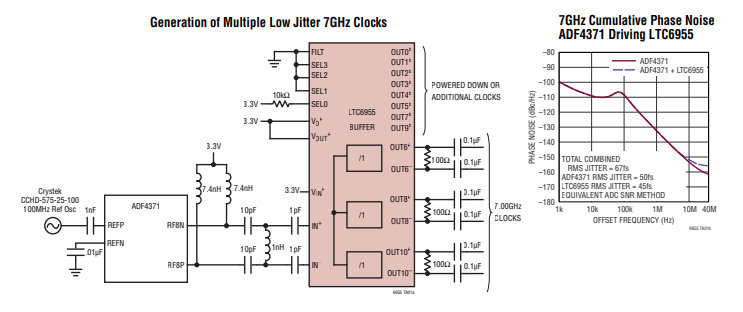

LTC6955超低抖動7.5GHz 11輸出扇出緩沖器系列技術手冊

HMC7043高性能、3.2 GHz、14輸出扇出緩沖器技術手冊

HMC7043高性能、3.2 GHz、14輸出扇出緩沖器技術手冊

評論