多芯片封裝(MCP)技術通過將邏輯芯片、存儲芯片、射頻芯片等異構模塊集成于單一封裝體,已成為高性能計算、人工智能、5G通信等領域的核心技術。其核心優勢包括性能提升、空間優化、模塊化設計靈活性,但面臨基板制造、熱管理、電源傳輸等關鍵挑戰。本文從技術原理、應用場景、行業趨勢三個維度剖析MCP的利弊,揭示其在算力密度與可靠性之間的技術平衡難題。

關鍵詞:多芯片封裝;2.5D/3D封裝;硅中介層;熱管理;電源傳輸

一、技術原理:從平面到立體的封裝革命

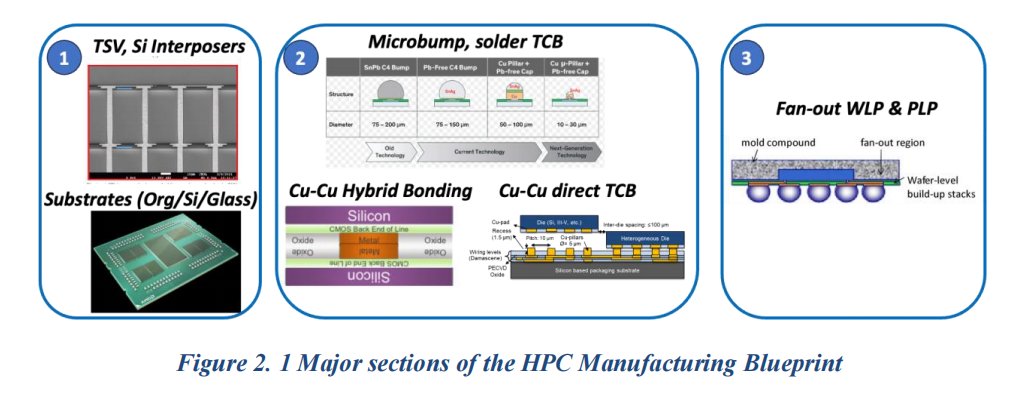

多芯片封裝技術本質上是半導體制造工藝的垂直延伸。傳統單芯片封裝將單個裸片(Die)通過引線鍵合或倒裝芯片技術連接至基板,而MCP則通過2.5D封裝(硅中介層)或3D封裝(芯片堆疊)實現多個裸片的三維集成。例如,Intel的EMIB技術通過硅中介層提供高密度互連,而臺積電的CoWoS(Chip-on-Wafer-on-Substrate)則利用TSV(硅通孔)實現垂直堆疊。

技術演進中,基板材料與互連技術是兩大核心瓶頸。當前,先進基板需支持線寬/線距≤1/1μm以適應高帶寬需求,但美國在精細間距RDL(重新布線層)技術上落后于亞洲。互連方案中,硅中介層雖可提供5000-10000根/mm2的互連密度,但成本較有機基板高出3-5倍。

二、優勢解析:性能與效率的雙重突破

1. 性能躍升:信號延遲降低70%

MCP通過縮短芯片間物理距離,顯著降低信號傳輸延遲。以HBM3存儲為例,將8個DRAM芯片堆疊至同一封裝體后,數據傳輸速率可達4-6Gbps/通道,相比傳統PCB布線延遲降低70%。此外,3D封裝通過垂直互連減少寄生電容,使能效比提升40%。

2. 空間革命:封裝體積縮小80%

在移動設備領域,MCP技術已實現“芯片級系統”(SoC+存儲+射頻)的集成。例如,蘋果A系列芯片采用MCP設計后,主板面積從400mm2縮減至80mm2,為電池和散熱模塊騰出更多空間。

3. 模塊化設計:開發周期縮短50%

MCP支持不同工藝節點的芯片異構集成,如將7nm邏輯芯片與28nm電源管理芯片封裝于同一基板。這種靈活性使廠商可根據需求動態調整配置,例如NVIDIA H100 GPU通過MCP技術集成8顆HBM3芯片,存儲帶寬突破3TB/s。

4. 成本優化:系統級成本下降30%

盡管單個MCP封裝成本較單芯片封裝高20%-30%,但系統級成本可降低。以數據中心服務器為例,采用MCP設計的計算卡減少PCB層數、連接器數量及散熱模塊,整體BOM成本下降15%-20%。

三、技術挑戰:從實驗室到量產的鴻溝

1. 基板制造:1/1μm線寬的工藝極限

先進基板需滿足高密度布線與低介電損耗的雙重需求。然而,當前RDL制造技術面臨三大難題:

- 光刻精度:1/1μm線寬需EUV光刻機支持,設備成本超1億美元;

- 材料性能:有機基板熱導率僅為0.3W/m·K,難以滿足200-400W TDP需求;

- 制造良率:面板級封裝(PLP)技術雖可降低單位成本,但良率較晶圓級封裝低15%-20%。

2. 熱管理:200W/cm2的散熱極限

3D封裝功率密度已突破200W/cm2,遠超傳統風冷散熱能力。以AMD EPYC處理器為例,其7nm工藝芯片采用MCP設計后,TDP達400W,需依賴液冷技術維持穩定運行。目前,業界正探索熱界面材料(TIM)與微通道散熱技術,但成本增加20%-30%。

3. 電源傳輸:1000A/mm2的電流密度挑戰

高帶寬需求導致封裝內電流密度達1000A/mm2,傳統分立電源組件難以滿足。基于封裝內電壓調節器(IVR)的技術雖可實現高效電源傳輸,但需解決以下問題:

- 電感寄生效應:高頻開關導致信號完整性下降;

- 熱應力失配:芯片與基板CTE(熱膨脹系數)差異引發封裝開裂。

4. 可靠性風險:機械應力與熱膨脹失配

堆疊芯片在熱循環測試中面臨三大失效模式:

- 焊點疲勞:3000次循環后焊點裂紋擴展速率達0.5μm/cycle;

- 分層現象:芯片與基板間粘附力下降40%;

- 電磁干擾:高頻信號導致封裝內串擾增加20dB。

四、行業應用:從實驗室到產業化的落地路徑

1. 高性能計算:算力密度提升10倍

在AI訓練領域,MCP技術使HBM3存儲與GPU芯片的互連距離從50mm縮短至5mm,顯著降低數據搬運能耗。例如,Google TPU v4采用MCP設計后,矩陣乘法效率提升60%。

2. 5G通信:射頻前端集成度提高3倍

智能手機射頻前端通過MCP技術集成PA(功率放大器)、LNA(低噪聲放大器)等模塊,使天線數量從8根減少至4根,同時支持Sub-6GHz與毫米波頻段。

3. 汽車電子:功能安全等級達ASIL-D

自動駕駛域控制器采用MCP技術實現MCU、AI加速器與存儲芯片的集成,滿足ISO 26262功能安全標準。例如,特斯拉FSD芯片通過MCP設計后,故障診斷覆蓋率(FDC)提升至99.9%。

五、未來趨勢:技術融合與生態重構

1. 小芯片(Chiplet)與異構集成

Chiplet技術通過將不同工藝節點的芯片封裝為標準模塊,降低制造難度。例如,AMD Zen 4架構CPU采用Chiplet設計后,良率提升15%,同時支持X86與ARM指令集的異構計算。

2. 3D封裝技術演進

- 混合鍵合(Hybrid Bonding):實現10μm間距的芯片直接互連;

- 玻璃基板:熱導率提升至3W/m·K,成本較硅基板降低30%;

- 光子芯片集成:在封裝內集成硅光子器件,突破電互連帶寬瓶頸。

3. 封裝內系統(SiP)2.0

未來SiP技術將向功能系統級封裝(FSoP)發展,實現電源管理、熱管理、傳感器等模塊的完全集成。例如,蘋果M系列芯片通過FSoP設計后,系統功耗降低25%。

六、結論:技術代價與產業價值的辯證

多芯片封裝技術以性能提升為代價,換取了空間優化與系統級成本下降。其核心矛盾在于:

- 技術投入:先進基板、熱管理、電源傳輸等關鍵技術需持續研發投入;

- 生態壁壘:Chiplet標準不統一導致碎片化風險;

- 可靠性驗證:長期運行穩定性需通過嚴苛測試(如JEDEC JESD22-A110C標準)。

未來,MCP技術將向三維異構集成與系統級優化方向演進,但其成功與否仍取決于材料科學、制造工藝與芯片設計的協同創新。對于產業界而言,MCP不僅是技術競賽,更是對半導體產業價值鏈的重構。

-

芯片封裝

+關注

關注

11文章

574瀏覽量

31256 -

MCP

+關注

關注

0文章

271瀏覽量

14252

發布評論請先 登錄

耐能KNEO Pi開發板的三大技術革新

電池充放電測試儀廠家:技術革新與市場動態的深度洞察

汽車車架焊接技術革新與應用前景

劃片機在Micro-LED芯片封裝中的應用與技術革新

蓄電池放電技術革新:引領能源存儲新時代

CSA公開規范加速芯片技術革新

無人機自動巡檢系統技術革新與應用前景

霍爾傳感器的發展歷史與技術革新

NVH-FLASH語音芯片支持平臺做語音—打造音頻IC技術革新

多芯片封裝:技術革新背后的利弊權衡

多芯片封裝:技術革新背后的利弊權衡

評論