文章來源:學習那些事

原文作者:前路漫漫

多芯片封裝技術

概述

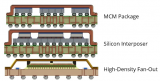

多芯片封裝在現代半導體領域至關重要,主要分為平面多芯片封裝和多芯片堆疊封裝。多芯片堆疊封裝又細分為多芯片3D堆疊引線鍵合封裝、3D堆疊引線鍵合和倒裝異質封裝、3DTSV堆疊倒裝封裝等。

在實際應用中,智能設備的存儲芯片需求推動著封裝技術發展。存儲芯片用于保存程序代碼,在電子設備中應用廣泛,要求存儲容量大、產品尺寸小。將多個薄芯片通過垂直堆疊、引線鍵合互連和塑封結構封裝,可滿足高密度、低成本的存儲封裝設計要求。調制解調器(Modem)則需要小型化與模塊化集成,引線鍵合和倒裝互連技術結合的芯片堆疊異質封裝結構能滿足其需求。雖然3D TSV堆疊倒裝封裝可大幅提升性能,但生產周期長、成本高,難以廣泛應用,所以多芯片堆疊引線鍵合互連以及多芯片堆疊封裝與引線鍵合異質互連仍是主流。

封裝體內裸芯片堆疊

1.早期常見堆疊方案

金字塔形:封裝、生產工藝簡單,下層芯片可有效支撐上層芯片引線鍵合,具有高良率、高穩定性、低生產成本等優點。但僅適用于不同尺寸芯片疊裝,因對芯片尺寸要求特殊,很少用于四層以上芯片堆疊。

工字形:設計相對成熟,可使用較小尺寸封裝體,但添加間隔硅片增加了產品成本和封裝體總體高度,主要用于四層以內芯片疊裝。

階梯式:封裝結構簡單、良品率高,但需較大封裝空間,包封易出現空洞問題,對焊線穩定性、工藝空間及設備穩定性與精度要求高,主要用于存儲產品封裝。

早期芯片堆疊的兩種方式

2.階梯式回旋裸芯片堆疊

相比階梯式堆疊,階梯式回旋裸芯片堆疊能有效解決過長焊線導致的焊線位置穩定性不良和封裝體體積增大問題。其優勢明顯,如堆疊結構簡單、封裝體尺寸小、堆疊體強度高、封裝工藝簡單、堆疊體高度易控制、包封過程不易產生氣泡,適用于相同尺寸芯片的多層堆疊。

3.基于焊線堆疊的其他方式

基于焊線堆疊是成本較低、良率較高的芯片堆疊方式。根據芯片大小和堆疊方式,可分為金字塔形堆疊、臺階互連、十字交錯互連、基于隔離硅片的互連、采用芯片黏結膜作為隔離層的互連、采用具有焊線穿透能力的芯片黏結膏(DAP)或芯片黏結薄膜(DAF)作為隔離層的互連 。除金字塔形堆疊外,其他方式適合同尺寸芯片。從互連焊點看,不同層芯片間互連分為通過焊線直接連接和基板互連(不同層芯片連接到基板焊盤,通過基板布線實現組合互連 )。不過,隨著堆疊層數增加,引線密度和長度增加,會導致寄生電感增加、功率增加、帶寬降低,且引線鍵合數量和芯片厚度受限。

主要相關工藝技術

1.裸芯片貼裝位置精度

多芯片3D堆疊時,裸芯片對齊要求高。受封裝體高度限制,芯片厚度變薄,面臨翹曲等挑戰。兩層裸芯片位置精度要求控制在 -15~+15um 。為實現多芯片高精度裝片,采用一次工藝裝片系統(OPAS)技術,通過調整一個方向裝片位置實現梯形堆疊,要求治具、設備、機臺一致性好,確保裝片位置高精度、穩定、重復。

2.晶圓減薄技術

在封裝中,為控制堆疊體高度,常需對多層堆疊芯片減薄,一般減薄至35 - 100um ,目前已有25um量產芯片。但存儲芯片成本敏感,過度減薄會降低裸芯片強度,增加減薄、切割和拾取難度與成本。減薄工藝和后續集成面臨晶圓碎裂或芯片背面殘留機械應力導致裂片的挑戰,需優化減薄輪和工藝參數,監控設備參數,維護設備與磨輪。為確保減薄質量,采用超精密兩步機械磨削、研磨,結合化學與機械拋光或腐蝕的研磨方法。硅晶圓減薄關鍵挑戰是60um及以下厚度芯片的微裂紋損傷,尤其是DRAM芯片,量產中常采用濕法或干法拋光消除損傷和殘留應力。對于16nm及以下厚度晶圓技術節點硅芯片,需采用雜質收集型干法拋光(GDP)工藝避免銅污染并提高芯片強度。傳統減薄工藝后,濕法拋光可去除磨削表面損傷,對后續工藝有積極意義。當芯片厚度達50um時強度明顯降低,易斷裂,可使用預剝離(PF)技術,拋棄頂針,用剝離滑塊通過真空吸附滑動,使芯片與膜預脫離,減小黏接力,避免芯片斷裂。

3.膜埋線技術

在八層階梯式回旋裸芯片堆疊封裝中,第四層和第五層芯片尺寸一致時,采用鍵合引線植入貼芯片膜(DAF)技術,即膜埋線(WiF)技術,將超低弧高鍵合引線埋入DAF中實現引線保護。具體是第四層芯片貼裝后進行超低弧高引線鍵合,在引線上面貼裝上層芯片,膜受熱融化時,下層芯片引線絲被埋入融化的DAF中。

4.鍵合引線超低弧高技術

堆疊芯片數量增加時,為保持封裝體總體高度不變,需減小引線環形層間隙,降低較低層引線鍵合弧高防止引線短路,同時控制頂層芯片引線弧高防止引線絲露出塑封體背面。目前40mm以下弧高的低弧度鍵合引線工藝已用于芯片量產,如優化的超低弧高引線倒打工藝可使直徑20um的引線弧高低至40um 。

5.其他先進堆疊技術

基于倒裝 + 焊線的堆疊:在3D封裝中,倒裝互連常與引線互連結合使用,倒裝可在上或在下。

基于硅通孔的3D封裝:硅通孔技術通過在硅圓片制作垂直互連孔,用銅、多晶硅或鎢等導電物質填充實現電信號貫通,芯片疊層時實現垂直互連 。

薄芯片集成3D封裝(TCI):TSV技術雖先進但成本高、工藝難,M.Topper等基于晶圓級工藝發展了TCI工藝 。關鍵工藝包括在厚基座晶圓焊盤形成第一層金屬化TiW/Cu;在基座晶圓形成第一層圖案化的BCB,粘貼超薄芯片(20 - 40μm );涂覆并圖形化第二層BCB(平坦化層 );制作第二層金屬化Cu布線;涂覆并圖形化第三層BCB;在BCB開口處形成第三層金屬Cu - Ni - Au焊盤;在焊盤上倒裝其他器件 。該工藝與常規晶圓級封裝工藝兼容,本質是將超薄芯片埋入底座晶圓表面后再布線互連,薄膜導線技術與CMOS工藝兼容,能實現無源器件集成、高互連密度、短互連,有效控制線路阻抗,溫度循環可靠性較好。

芯片堆疊后埋入(EMWLP):2008年,Vaidyanathan Kripesh等報道了多芯片埋入式微晶圓級封裝(EMWLP),即3D EMWLP ,本質是多芯片堆疊的芯片先裝FOWLP,芯片堆疊、模壓前在焊盤制作銅柱 。工藝流程包括在承載晶圓片貼黏結載帶;將不同芯片(每個芯片I/O設置電鍍銅柱 )由大到小依次堆疊到承載晶圓;模塑;研磨銅;分離承載晶圓;剝離黏結載帶;制作再布線和植球 。

多芯片堆疊封裝存在芯片高精度裝片、超低線弧、超薄芯片、多層堆疊厚度和超高密度封裝等技術難點,通過開發應用15um裝片精度、超薄晶圓減薄、超薄芯片拾取、膜埋線、超低引線弧高等技術可有效克服。

-

半導體

+關注

關注

335文章

28435瀏覽量

230901 -

封裝技術

+關注

關注

12文章

571瀏覽量

68386 -

多芯片封裝

+關注

關注

0文章

6瀏覽量

6054

原文標題:多芯片封裝技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文詳解多芯片封裝技術

一文詳解多芯片封裝技術

評論