概述

AD8344是一款高度集成的SiGe有源濾波器,專門針對接收路徑下變頻進行了優化。該器件的輸入范圍為400 MHz至1.2 GHz,適合CDMA、GSM和TETRA基礎設施設備等眾多應用。

AD8344在RF和LO輸入端口上均提供一個單端50 Ω輸入阻抗。集成的LO驅動器提供LO驅動電平,典型值為0 dBm。

通過與EXRB引腳相連的一個外部偏置電阻,可以優化AD8344的功耗與線性度。AD8344采用+5 V單電源供電,功耗僅為84 mA,省電模式下為500 μA。

AD8344采用高性能SiGe工藝制造,提供節省空間的3 mm x 3 mm、16引腳LFCSP封裝,額定溫度范圍為-40°C至+85°C。

數據表:*附件:AD8344 400MHz至1.2GHz有源接收混頻器技術手冊.pdf

特性

- RF頻率范圍:400 MHz至1.2 GHz

- IF頻率范圍:70 MHz至400 MHz

- 集成的LO驅動器要求0 dBm

- 輸入三階交調截點(IP3):+24dBm

- 輸入壓縮點(P1dB):+8.5 dBm

- 轉換增益:+4.5 dB

- 噪聲系數:10.5dB

- 5 V單電源供電,具有省電模式

- 3mm x 3mm、小型LFCSP封裝

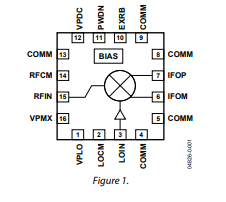

框圖

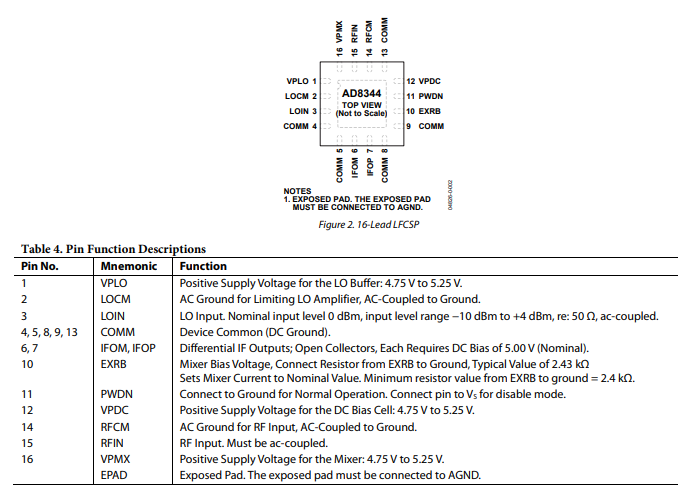

引腳配置描述

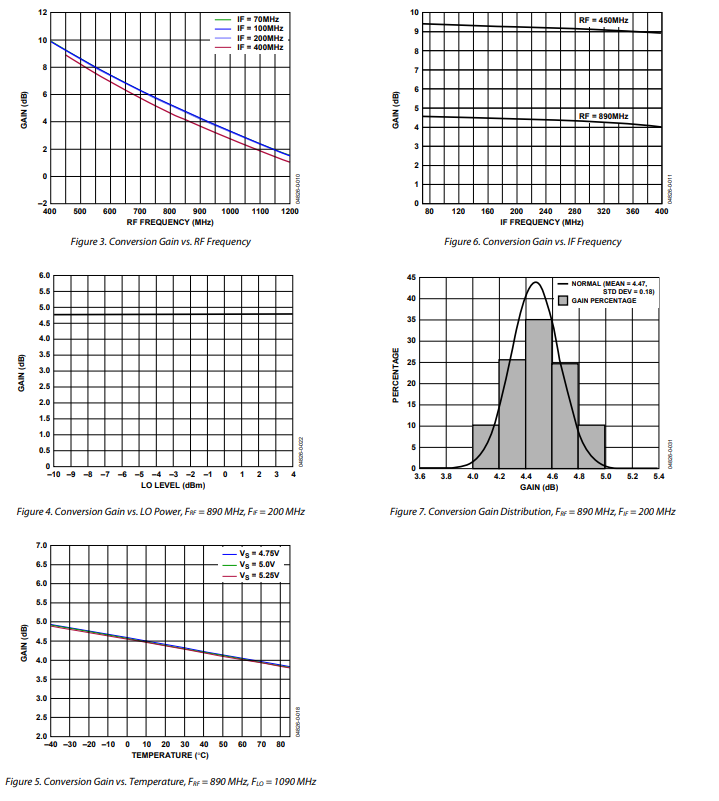

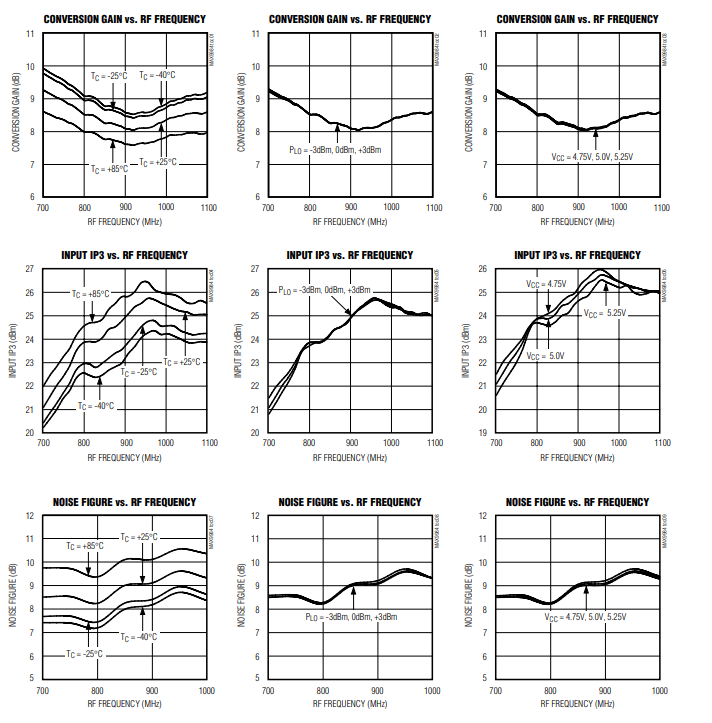

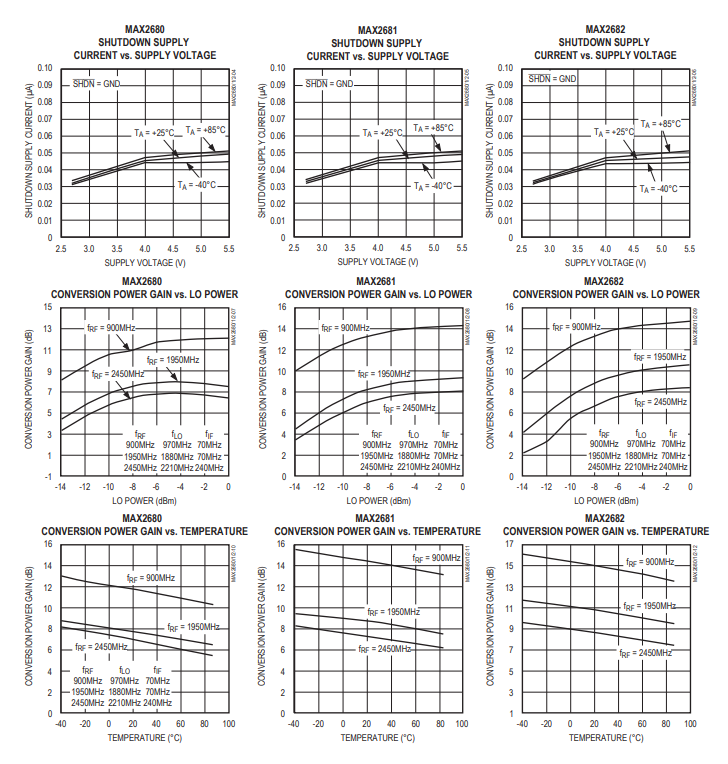

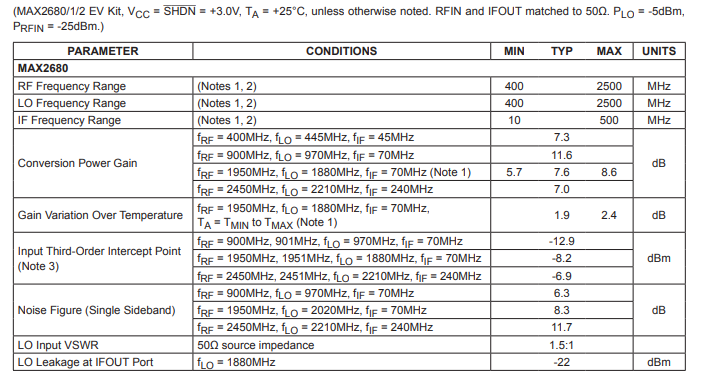

典型性能特征

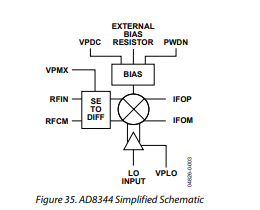

電路描述

AD8344 是一款下變頻混頻器,針對 400MHz 至 1.2GHz 的輸入頻率范圍進行了優化。它具有單端 50Ω 射頻輸入,以及單端 50Ω 本地振蕩器(LO)輸入。中頻輸出為差分集電極開路輸出。可通過外部電阻的值來調節混頻器的最大電流,以優化增益、壓縮和互調性能,或用于低功率操作。圖 35 展示了混頻器的基本模塊,包括本振緩沖器、射頻電壓 - 電流轉換器、偏置單元和混頻核心。

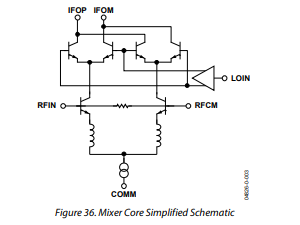

射頻電壓到射頻電流的轉換是通過電感退化差分對實現的。當差分對的一側交流接地時,另一側可進行單端驅動。射頻輸入也可以差分驅動。電壓到電流轉換器驅動四晶體管開關核心的發射極,該開關核心由放大的本振信號驅動。本地振蕩器信號連接到本振輸入。

本振輸入與外部本振信號之間有三個限幅增益級。第一級將單端本振驅動轉換為平衡的差分驅動。差分驅動信號通過另外兩個增益級,這確保了在限制信號驅動的同時,仍能保持出色的動態范圍和轉換性能。這三個本振增益級的輸出以本地振蕩器頻率的速率驅動混頻核心內的四個晶體管。混頻核心的輸出直接取自其集電極開路端。集電極開路輸出對中頻呈現高阻抗。轉換增益直接取決于呈現給這些開路集電極的阻抗。在特性描述中,通過 4:1 阻抗變壓器向器件提供 200Ω 負載。

AD8344 還具備掉電功能。在 PWDWN 引腳施加邏輯低電平可使 AD8344 進入掉電模式。PWDWN 引腳置高電平時,器件恢復正常工作。掉電時的功耗低于 10mW。

混頻器的偏置由來自 EXRB 引腳的外部電阻設置。該電阻的值直接影響混頻器核心的動態范圍。此外部電阻絕不能低于 2.4kΩ。若使用低于 2.4kΩ 的電阻,可能會對器件造成永久性損壞。

如圖 36 所示,中頻輸出引腳 IFOP 和 IFOM 直接連接到混頻核心中 NPN 晶體管的集電極開路端,因此差分和單端阻抗相對較高,約為幾 kΩ。為使 AD8344 混頻器核心正常工作,需要在電源電壓與這些輸出引腳之間進行連接。

AD8344 有三個電源電壓引腳:VPDC、VPMX 和 VPLO。這些引腳相互隔離,以盡量減少或消除可能導致雜散信號或降低互端口隔離的寄生耦合路徑。因此,這些引腳中的每一個都必須良好旁路,并盡可能靠近 AD8344 進行去耦。

-

SiGe

+關注

關注

0文章

99瀏覽量

23896 -

變頻

+關注

關注

1文章

455瀏覽量

34361 -

有源濾波器

+關注

關注

5文章

257瀏覽量

31316

發布評論請先 登錄

DC1983A,使用LTC5510,1 MHz至6 GHz寬帶高線性有源混頻器的演示板

AD8344 400 MHz 至1.2 GHz 有源接收混頻器

LT5557: 400MHz 至 3.8GHz、3.3V 有源下變頻混頻器 數據手冊

高動態范圍有源上變頻混頻器支持 400MHz 至 2.7GHz 所有 LTE / 蜂窩頻段

LT5527: 400MHz 至 3.7GHz、5V 高信號電平下變頻混頻器 數據手冊

ADL5802:雙通道、高IP3、100 MHz至6 GHz有源混頻器產品手冊

DC910A LT5557EUF | 400MHz至3.8GHz向下混頻器, 1.95GHz RF, 240MHz 分立匹配IF

MAX9984 SiGe、高線性度、400MHz至1000MHz下變頻混頻器技術手冊

AD8344 400MHz至1.2GHz有源接收混頻器技術手冊

AD8344 400MHz至1.2GHz有源接收混頻器技術手冊

評論