2025年3月21日,一站式定制芯片及IP供應商——燦芯半導體(上海)股份有限公司(燦芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平臺的DDR3/4, LPDDR3/4 Combo IP。該IP具備廣泛的協議兼容性,支持DDR3, DDR3L, DDR4和LPDDR3, LPDDR4協議,數據傳輸速率最高可達2667Mbps,并支持X16/X32/X64等多種數據位寬應用。

燦芯半導體此次發布的DDR3/4, LPDDR3/4 Combo IP集成高性能DDR PHY和靈活配置的Controller,具有高速率、低功耗和小面積的優點,不僅支持低功耗掉電模式和ECC(錯誤校正碼)功能,還可兼容市場上相應模式的各種成熟DDR DRAM顆粒,以確保客戶在設計中的靈活性和兼容性。

目前,該IP已成功流片,并順利通過芯片級的功能測試和性能測試,各項指標均達到預期標準。憑借其優越的性能和低功耗特性,該DDR3/4, LPDDR3/4 Combo IP可廣泛應用于網絡設備、移動裝置、IoT和存儲設備等應用領域,滿足高速數據傳輸、低功耗和在小面積設計中實現高性能的需求。

“28HKD是平面半導體工藝的一個關鍵平臺,我們的DDR3/4, LPDDR3/4 Combo IP將進一步豐富此工藝平臺上的IP庫,助力客戶進行產品設計。”燦芯半導體市場副總裁陳麗說,“燦芯半導體致力于為客戶提供卓越的設計服務和高可靠性的IP,今后,我們會陸續在此工藝平臺上推出更多的優質IP供客戶使用。”

燦芯半導體通過嚴格的設計和驗證流程,確保了該IP在實際應用中的可靠性和穩定性。未來,公司將繼續致力于為客戶提供各工藝平臺的IP和定制芯片解決方案,助力客戶提升市場競爭力。

關于燦芯半導體

燦芯半導體(上海)股份有限公司(燦芯股份,688691)是一家提供一站式定制芯片及IP的高新技術企業,為客戶提供從芯片規格制定、架構設計到芯片成品的一站式服務,致力于為客戶提供高價值、差異化的解決方案。

燦芯半導體的“YOU”系列IP和YouSiP(Silicon-Platform)解決方案,經過了完整的流片測試驗證。其中YouSiP方案可以為系統公司、無廠半導體公司提供原型設計參考,從而快速贏得市場。

燦芯半導體成立于2008年,總部位于中國上海,為客戶提供全方位的優質服務。

-

芯片

+關注

關注

459文章

52119瀏覽量

435623 -

DDR3

+關注

關注

2文章

282瀏覽量

42919 -

燦芯半導體

+關注

關注

0文章

57瀏覽量

12853 -

LPDDR3

+關注

關注

0文章

7瀏覽量

15004

原文標題:燦芯半導體推出DDR3/4, LPDDR3/4 Combo IP

文章出處:【微信號:BriteSemi,微信公眾號:燦芯半導體BriteSemi】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

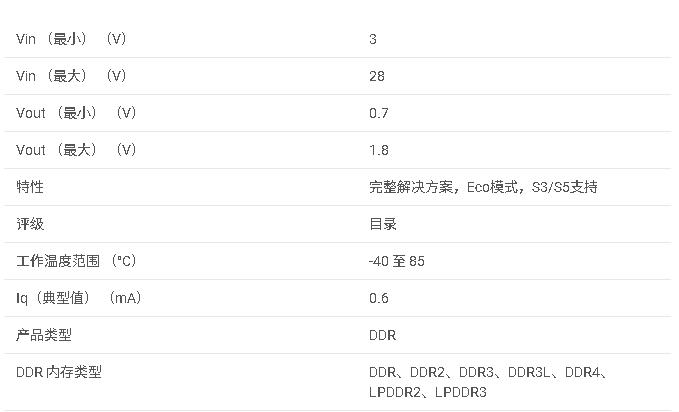

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據手冊

燦芯半導體受邀參加IP-SoC Silicon Valley 2025

TPS51716 完整的 DDR2/3/3L/4 存儲器電源解決方案同步降壓控制器數據手冊

DDR3 SDRAM配置教程

燦芯半導體推出DDR3/4和LPDDR3/4 Combo IP

燦芯半導體推出DDR3/4和LPDDR3/4 Combo IP

評論