以下文章來源于逍遙設(shè)計自動化 ,作者逍遙科技

引言

半導(dǎo)體行業(yè)不斷發(fā)展,不斷推動芯片設(shè)計和制造的邊界。隨著逐漸接近傳統(tǒng)平面縮放的極限,先進封裝技術(shù)正成為持續(xù)提升性能的關(guān)鍵推動力。在這些技術(shù)中,3.5D封裝作為當前2.5D解決方案和完全3D集成之間的折中方案,正在獲得廣泛關(guān)注。本文將探討3.5D封裝的概念、優(yōu)勢、挑戰(zhàn)以及對半導(dǎo)體設(shè)計未來的潛在影響。

什么是3.5D封裝?

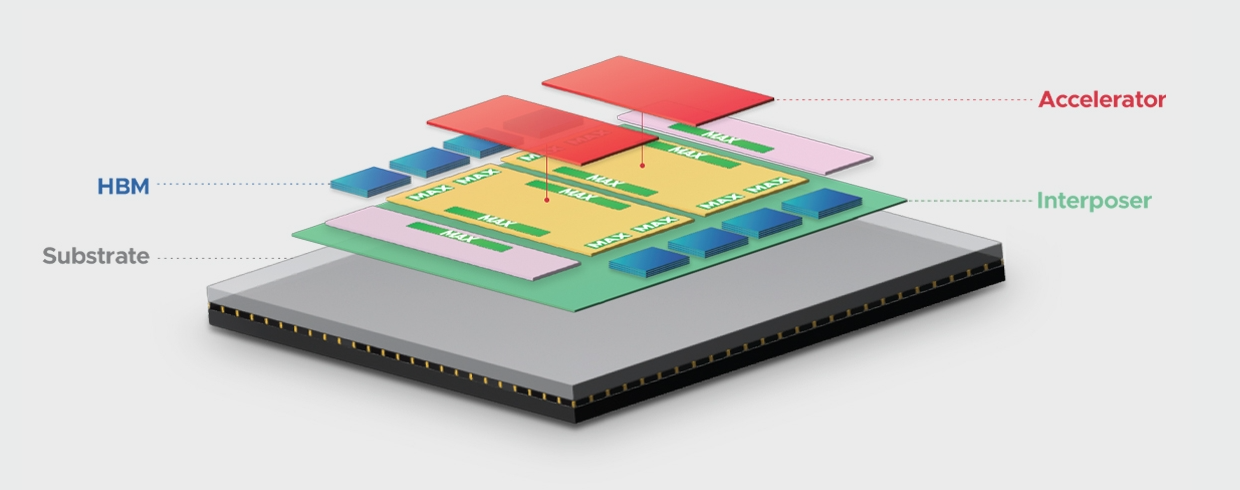

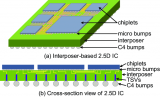

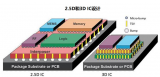

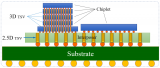

3.5D封裝是一種結(jié)合了2.5D和3D集成技術(shù)元素的混合方法。在3.5D配置中,邏輯chiplet垂直堆疊,然后與其他組件一起鍵合到共享基板上。這種方法在廣泛采用的2.5D技術(shù)和更復(fù)雜的完全3D-IC之間提供了一個中間地帶,而業(yè)界已經(jīng)努力將后者商業(yè)化近十年。

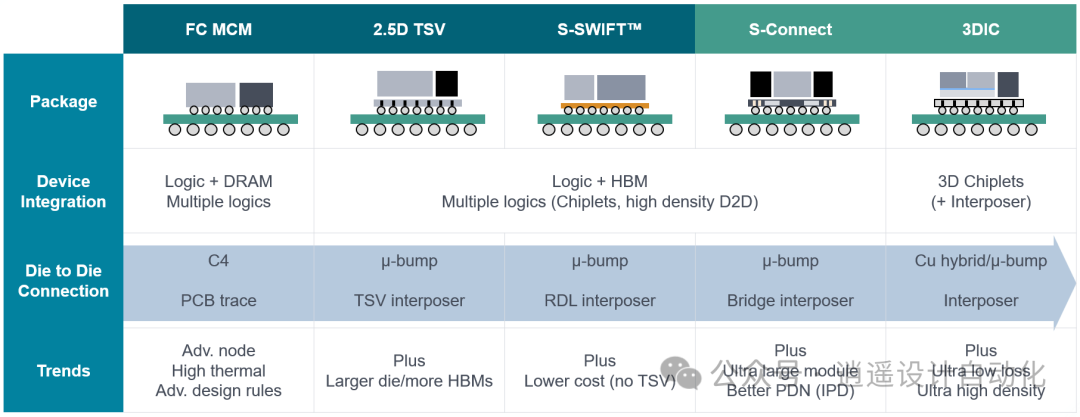

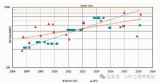

圖1:三星的異構(gòu)集成路線圖,展示了封裝技術(shù)的演變。(來源:三星代工廠)

3.5D封裝的主要優(yōu)勢

熱管理 :通過在組件之間創(chuàng)建物理分隔,3.5D封裝有效解決了困擾更密集3D配置的熱耗散和噪聲問題。

增加SRAM集成 :由于SRAM縮放落后于數(shù)字晶體管縮放,3.5D允許通過垂直堆疊chiplet將更多SRAM添加到高速設(shè)計中。這對于維持處理器緩存性能非常重要。

改善信號傳輸 :減薄處理元件和內(nèi)存之間的接口縮短了信號需要傳輸?shù)木嚯x,與平面實現(xiàn)相比顯著提高了處理速度。

靈活性和可擴展性 :3.5D組件提供了更大的靈活性來添加額外的處理器核心,并通過允許已知良好的裸片單獨制造和測試來實現(xiàn)更高的良率。

異構(gòu)集成 :這種方法使用不同制程節(jié)點制造的芯片可以組合在一起,優(yōu)化性能和成本。

實施策略

最常見的3.5D配置涉及將處理器堆疊在SRAM上。這種安排簡化了冷卻,因為高利用率處理元件產(chǎn)生的熱量可以通過散熱器或液體冷卻來移除。減薄的基板允許信號傳輸更短的距離,減少了處理器和內(nèi)存之間數(shù)據(jù)移動的功耗。

有趣的是,SRAM不一定需要與先進處理器處于相同的制程節(jié)點。這種靈活性有助于提高良率和可靠性。例如,三星提出了一個路線圖,顯示在不久的將來,2nm chiplet堆疊在4nm chiplet上,并計劃到2027年實現(xiàn)1.4nm chiplet堆疊在2nm chiplet上。

英特爾的3.5D技術(shù)方法涉及在帶有硅橋的基板上實現(xiàn)。這種方法以成本效益高的方式使用薄硅片來實現(xiàn)芯片間互連,包括堆疊芯片間互連。這種方法提供了硅密度和信號完整性性能的優(yōu)勢,而無需使用大型、昂貴的單片互連層。

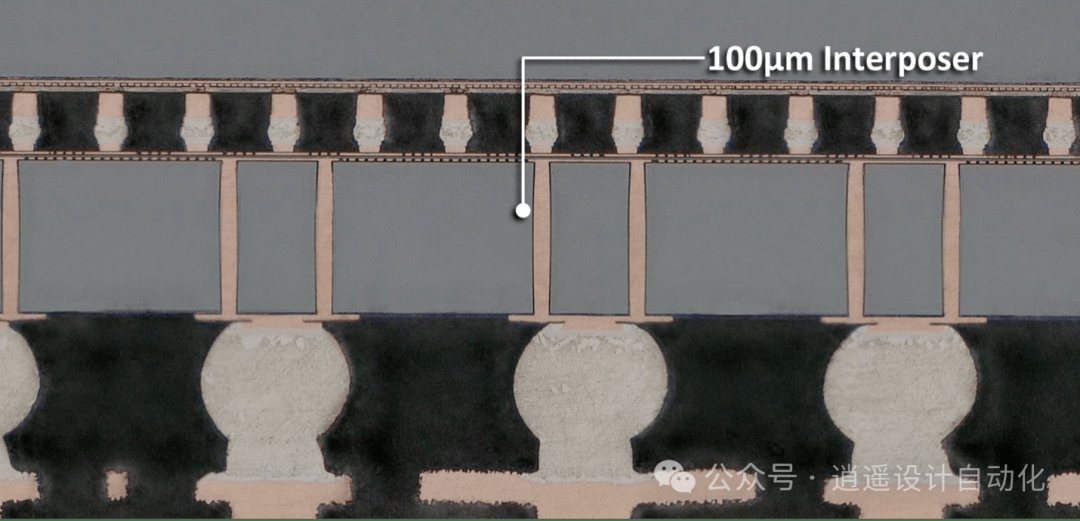

圖3:當前互連層技術(shù)支持高I/O數(shù)量和精細間距。(來源:日月光集團)

挑戰(zhàn)和持續(xù)發(fā)展

3.5D封裝提供了眾多優(yōu)勢,但也面臨著挑戰(zhàn)。一些關(guān)鍵的持續(xù)發(fā)展領(lǐng)域包括:

熱管理 :盡管相比完全3D設(shè)計有所改善,但在3.5D組件中管理熱量仍然是一個重大挑戰(zhàn)。業(yè)界正在探索各種冷卻解決方案,包括浸沒式冷卻、局部液體冷卻和蒸汽室。

互連技術(shù) :隨著我們推動更高的密度,業(yè)界正在向更精細的凸點間距解決方案和混合鍵合技術(shù)發(fā)展。目標是實現(xiàn)25到20微米的凸點間距,混合鍵合可能實現(xiàn)小于10微米的間距。

共面性 :在數(shù)千個微凸點上實現(xiàn)所需的平整度水平對傳統(tǒng)鍵合方法是一個重大挑戰(zhàn)。這正推動人們對混合鍵合等替代方法產(chǎn)生興趣。

時序收斂 :隨著在3.5D配置中添加更多元素,確保信號在正確的時間到達正確的位置變得越來越復(fù)雜。這需要復(fù)雜的熱感知和IR感知時序分析。

數(shù)據(jù)管理 :設(shè)計和分析這些復(fù)雜系統(tǒng)所涉及的數(shù)據(jù)量正在爆炸性增長。有效處理這些數(shù)據(jù)并減少模擬和分析運行時間是一個主要關(guān)注領(lǐng)域。

組裝復(fù)雜性 :物理組裝這些器件涉及管理具有不同厚度和熱膨脹系數(shù)的各種裸片的熱、電和機械連接。這需要進行密集的熱機械認證工作。

圖4:先進封裝路線圖,說明互連技術(shù)的演變。(來源:安靠科技)

商業(yè)化的道路

3.5D封裝的最終目標是實現(xiàn)芯片設(shè)計的"即插即用"方法,設(shè)計者可以從菜單中選擇chiplet,并迅速將連接到經(jīng)過驗證的架構(gòu)中。雖然這一愿景可能需要數(shù)年時間才能完全實現(xiàn),但可能在未來幾年內(nèi)看到商用chiplet出現(xiàn)在先進設(shè)計中,從高帶寬內(nèi)存與定制處理器堆疊開始。

實現(xiàn)這一愿景需要在幾個關(guān)鍵領(lǐng)域取得進展:

EDA工具 :電子設(shè)計自動化(EDA)工具需要發(fā)展以處理3.5D設(shè)計的復(fù)雜性。這包括同時考慮熱、信號完整性和功率完整性問題,以及改善IC設(shè)計師和封裝專家之間的協(xié)作。

工藝/組裝設(shè)計套件 :3.5D工藝和組裝的標準化設(shè)計套件非常重要。這些可能會在代工廠和外包半導(dǎo)體組裝和測試(OSAT)提供商之間分配。

標準化 :為可以預(yù)先構(gòu)建和預(yù)先測試的內(nèi)容設(shè)置現(xiàn)實的參數(shù)將是提高組裝速度和便利性的關(guān)鍵。像UCIe(通用chiplet互連快車)這樣的行業(yè)標準就是朝這個方向邁出的步伐。

工藝一致性 :確保3.5D組裝各個步驟的工藝一致性非常重要。這需要為每個工藝步驟定義可接受的輸出,并開發(fā)實時優(yōu)化配方的方法,以保持結(jié)果在所需范圍內(nèi)。

結(jié)論

3.5D封裝代表了半導(dǎo)體集成的重要進步,在3D-IC的性能優(yōu)勢和當前2.5D解決方案的實用性之間提供了平衡。隨著業(yè)界趨向于這種方法,可以期待在設(shè)計工具、制造工藝和標準化努力方面的快速發(fā)展。

在熱管理和互連技術(shù)等領(lǐng)域仍然存在挑戰(zhàn),但3.5D封裝的潛在優(yōu)勢正在推動大量投資和創(chuàng)新。隨著這些技術(shù)的成熟,有望在從高性能計算到人工智能等廣泛應(yīng)用中實現(xiàn)新的性能和功能水平。

實現(xiàn)完全的3.5D封裝及其他更高集成的旅程將需要整個半導(dǎo)體生態(tài)系統(tǒng)的持續(xù)合作。從EDA供應(yīng)商到代工廠、OSAT和系統(tǒng)集成商,每個參與者在將這項技術(shù)推向市場方面都發(fā)揮著重要作用。隨著我們向前發(fā)展,3.5D封裝可能成為連接當前技術(shù)與未來完全3D-IC的橋梁,開啟半導(dǎo)體創(chuàng)新的新時代。

-

芯片

+關(guān)注

關(guān)注

459文章

52162瀏覽量

436078 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28588瀏覽量

232472 -

封裝

+關(guān)注

關(guān)注

128文章

8481瀏覽量

144776 -

晶體管

+關(guān)注

關(guān)注

77文章

9978瀏覽量

140643

原文標題:3.5D封裝:2.5D和完全3D集成之間找到的平衡點

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一顆芯片面積頂4顆H200,博通推出3.5D XDSiP封裝平臺

繼vivo NEX 3后,OPPO又曝“瀑布屏”手機

UV固化封裝技術(shù)與普通膠水封裝相比,它有什么優(yōu)勢

1530億晶體管,AMD發(fā)布史上最大、最強芯片!多項指標數(shù)倍于H100,打響挑戰(zhàn)英偉達第一槍!

Chiplet&互聯(lián)要聞分享 「奇說芯語 Kiwi talks」

MEMS傳感器在汽車應(yīng)用增長快速,NEMS、3.5D封裝技術(shù)成趨勢

一文理解2.5D和3D封裝技術(shù)

深入剖析2.5D封裝技術(shù)優(yōu)勢及應(yīng)用

3.5D封裝來了(下)

3.5D封裝來了(上)

先進封裝技術(shù):3.5D封裝、AMD、AI訓(xùn)練降本

3.5D Chiplet技術(shù)典型案例解讀

什么是3.5D封裝?它有哪些優(yōu)勢?

什么是3.5D封裝?它有哪些優(yōu)勢?

評論